EE 271 - Digital Circuits and Systems

Lab Notes

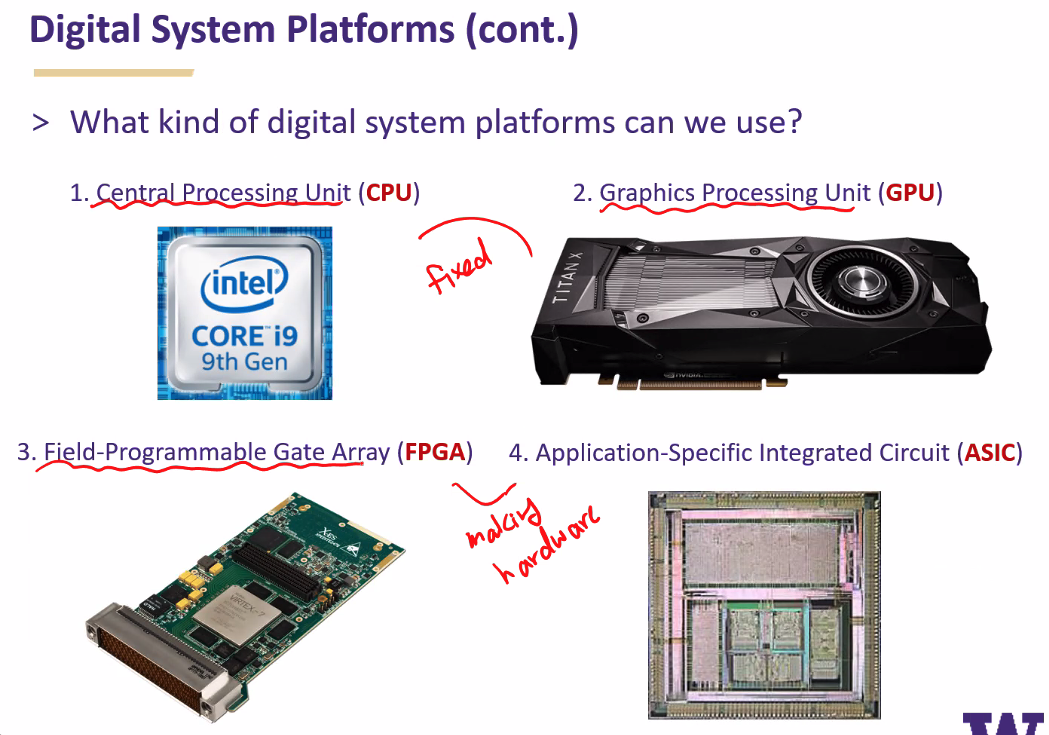

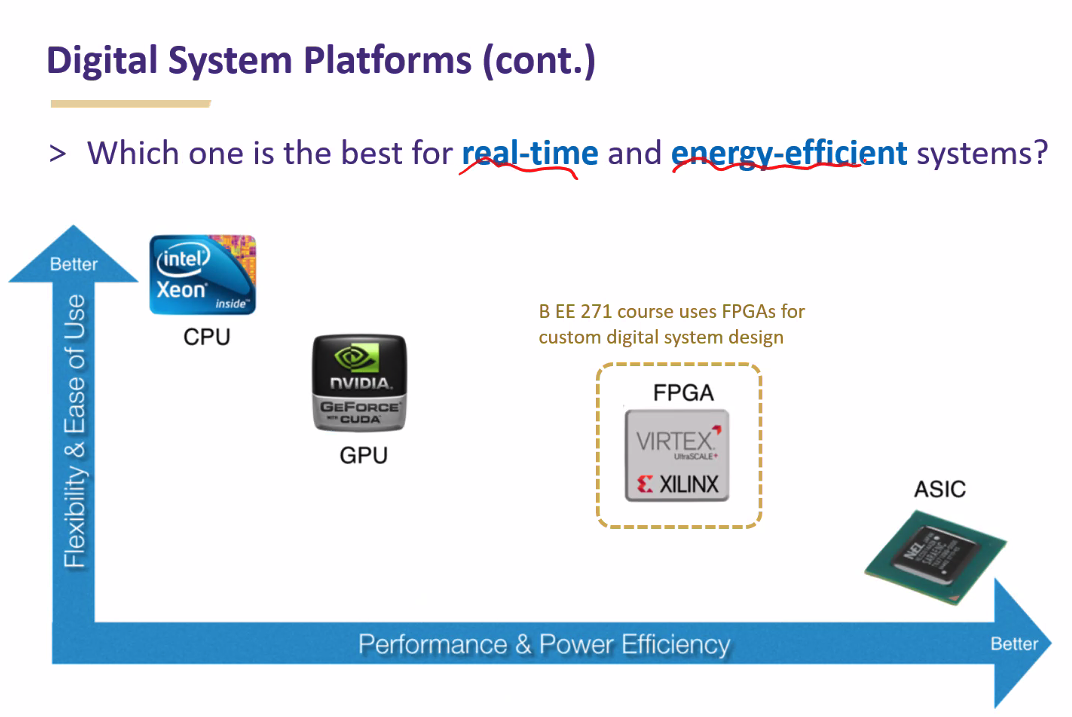

Types of digital system platforms

- CPU (Central Processing Unit)

- Graphics Processing Unit (GPU)

- Field-Programmable Gate Array(FPGA)

- Application-Specific Integrated Circuit (ASIC)

options for mac users

Day 1 Lecture Notes

Why should we study digital electronics?

"Because they're everywhere"

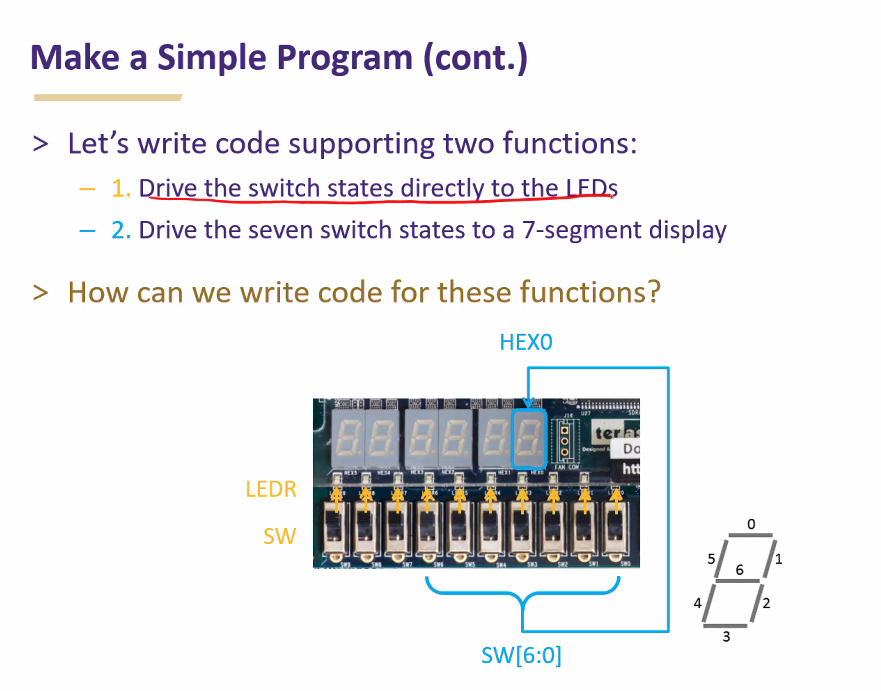

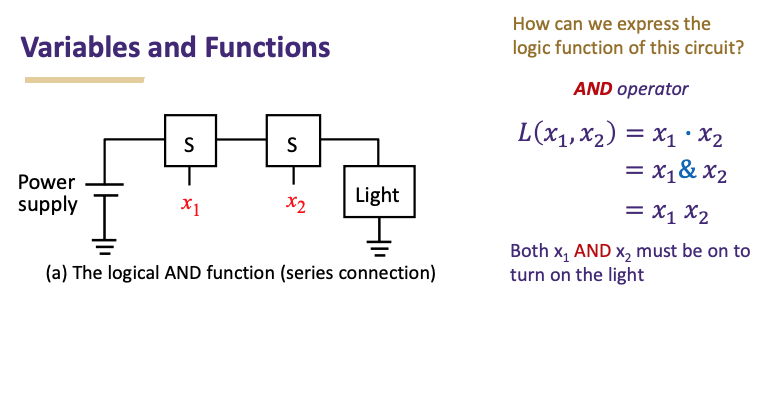

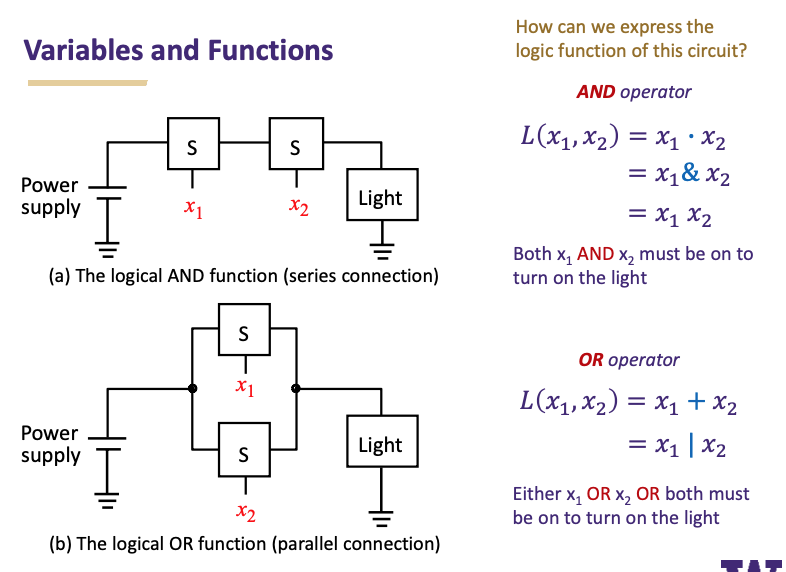

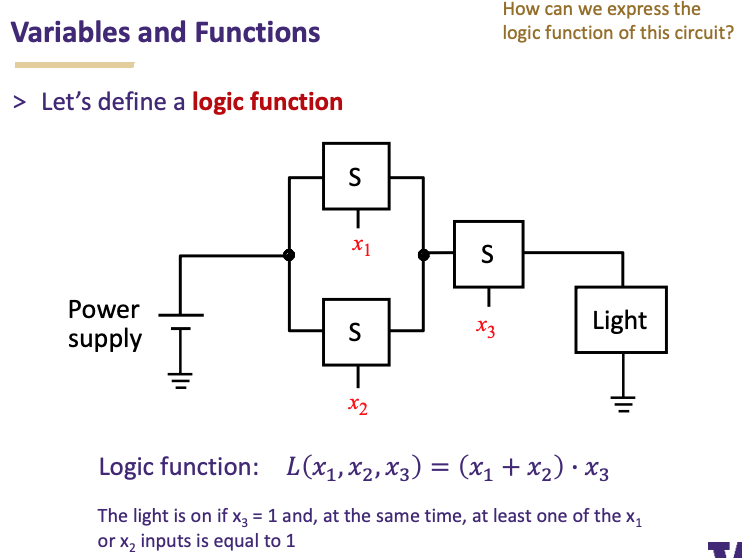

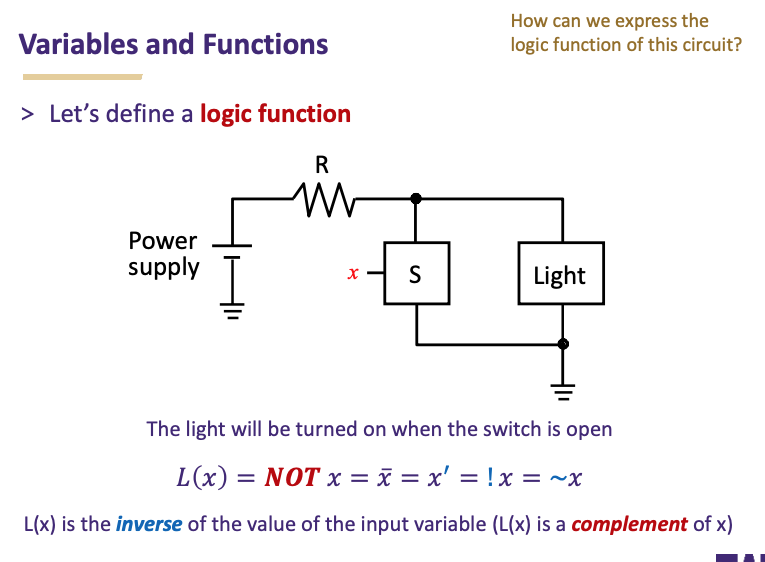

Variables and Functions

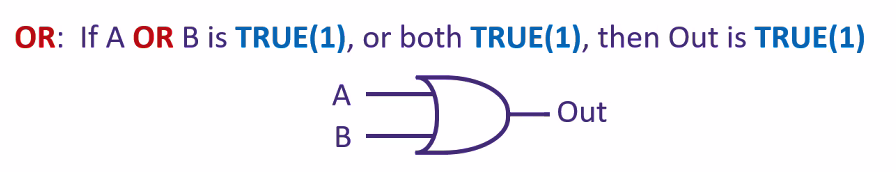

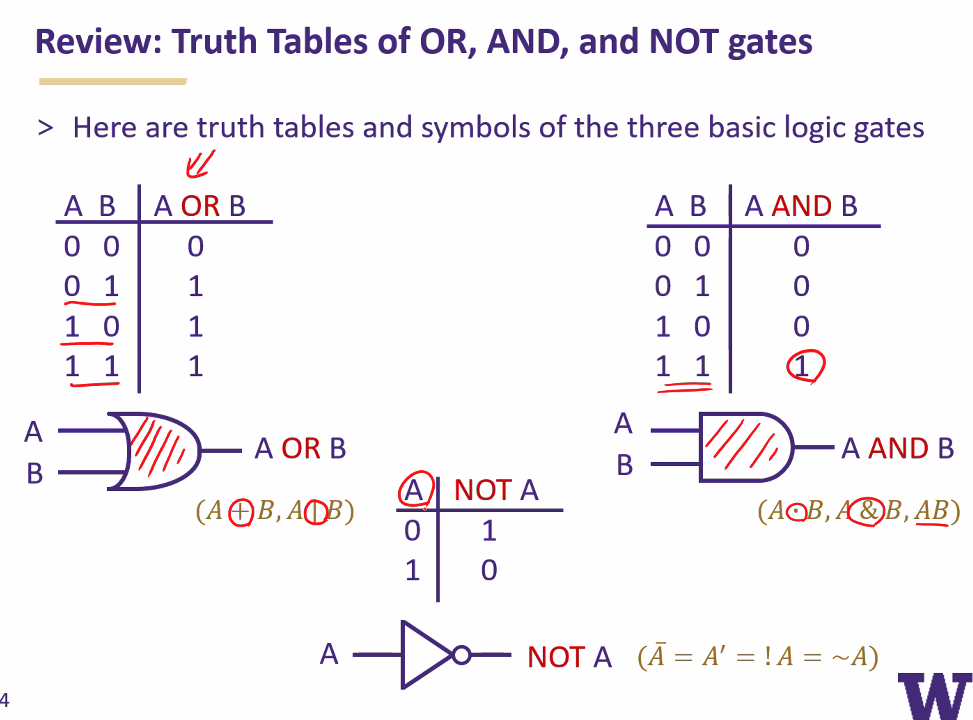

Or gate

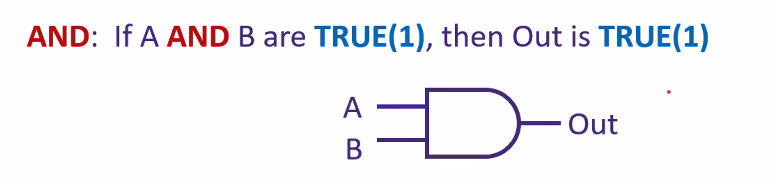

And Gate

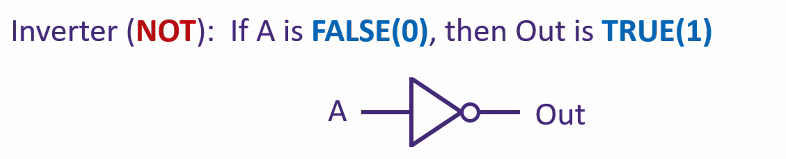

Inverter (Not Gate)

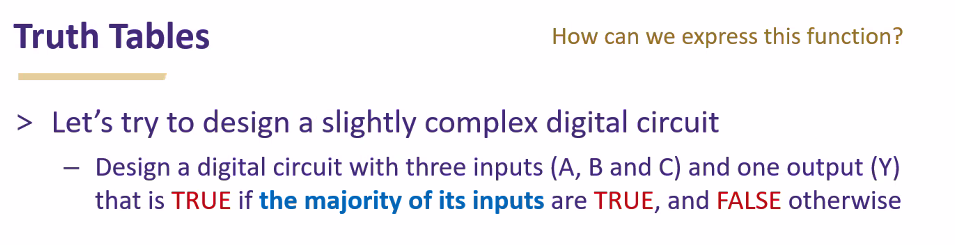

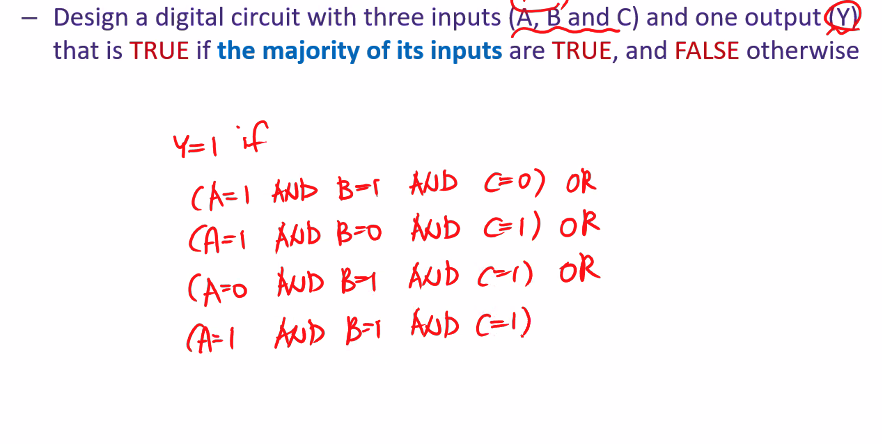

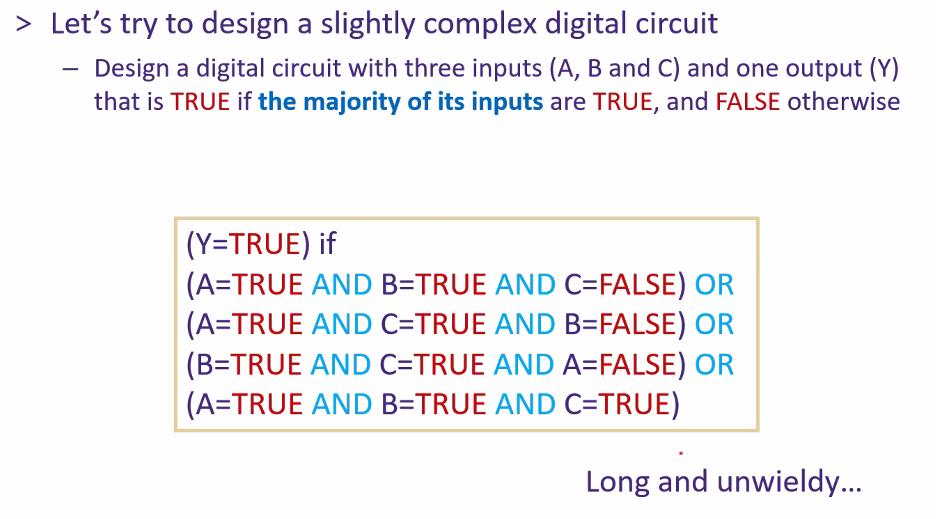

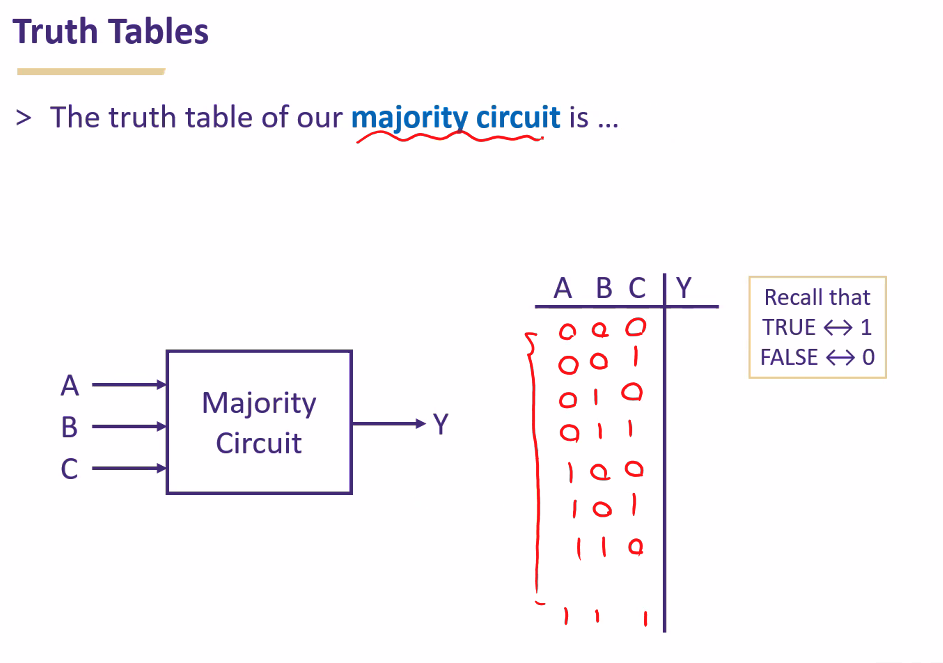

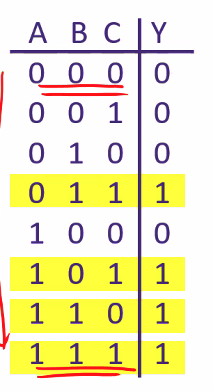

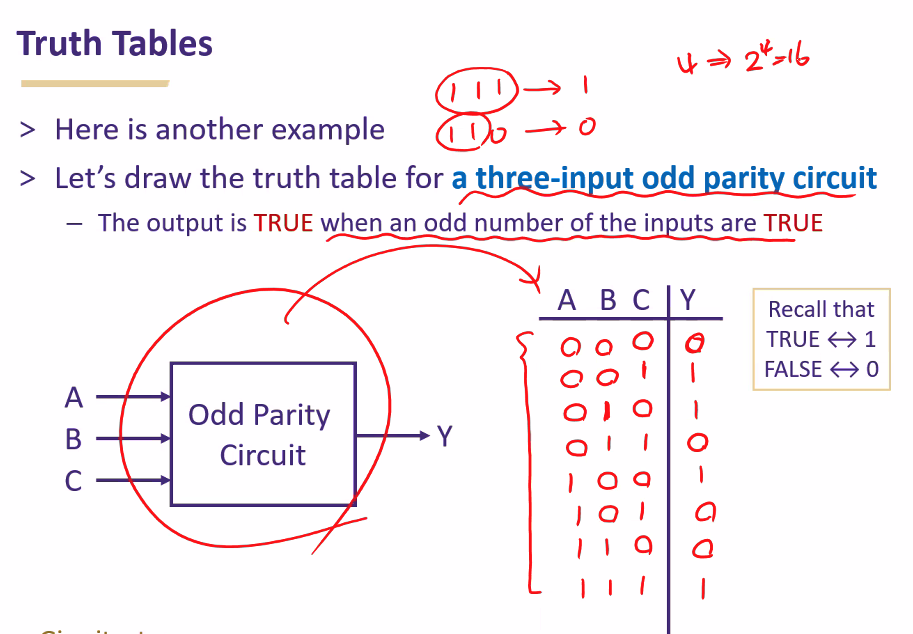

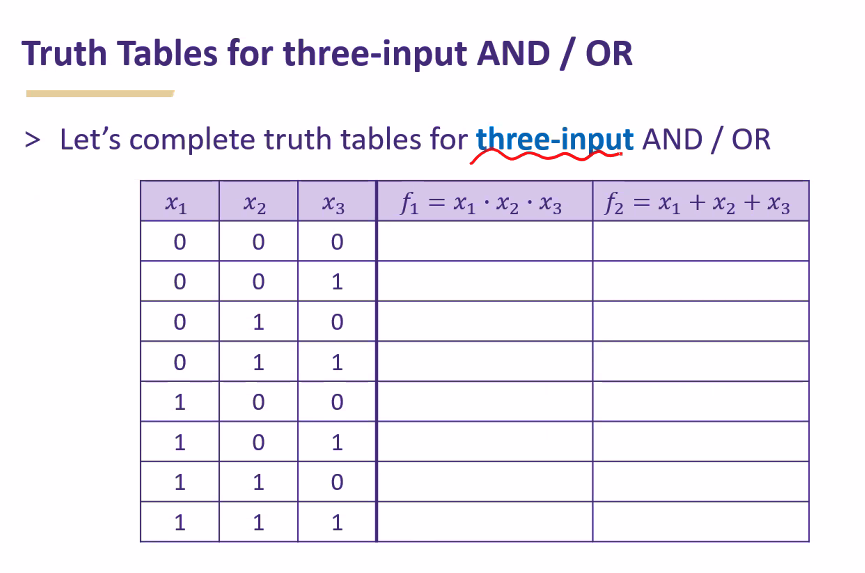

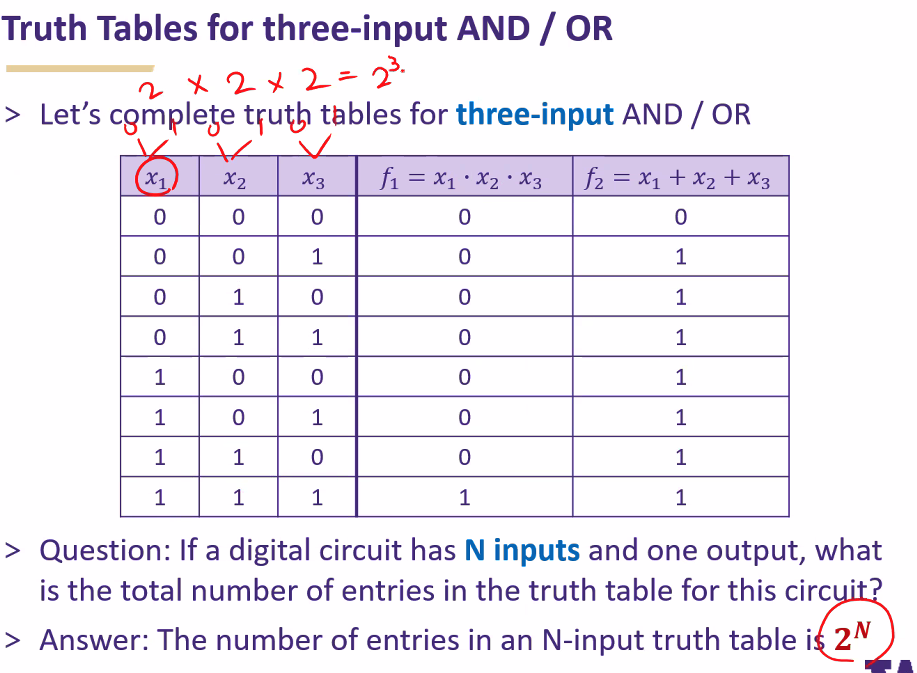

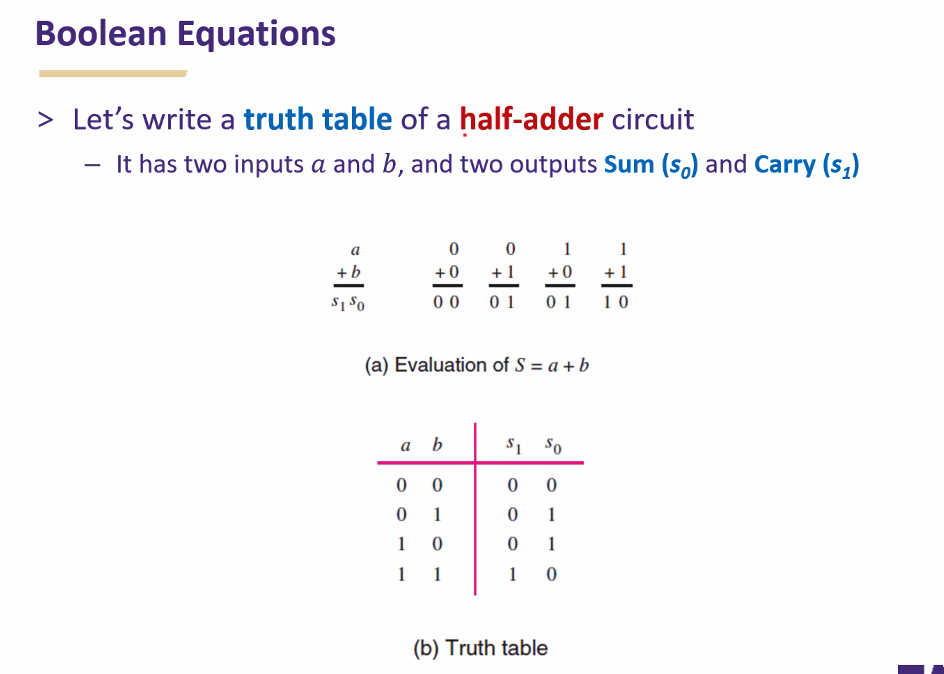

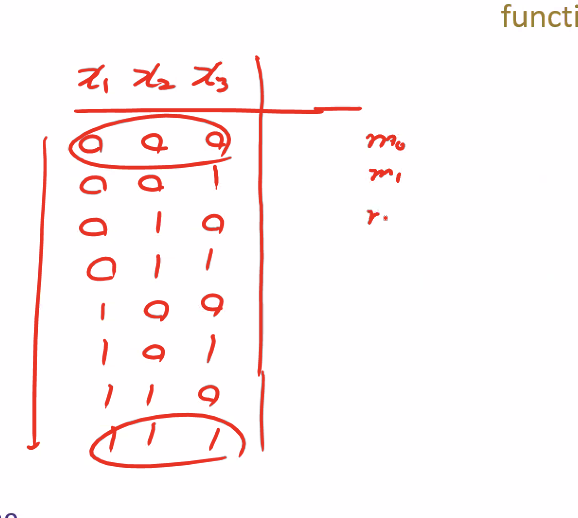

Truth Tables

there is a fixed order

000 first, 111 last

the number of cases is 2^n where n is the number of inputs

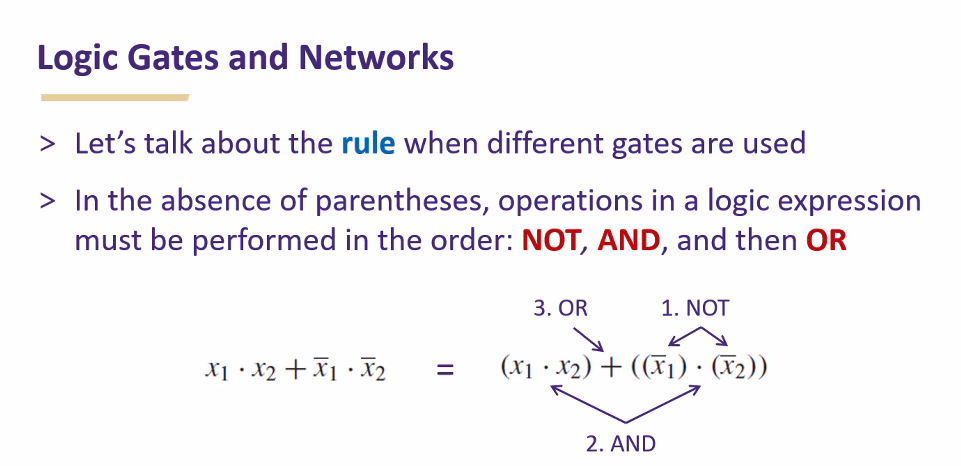

NOT, then AND, then OR with no parenthesis

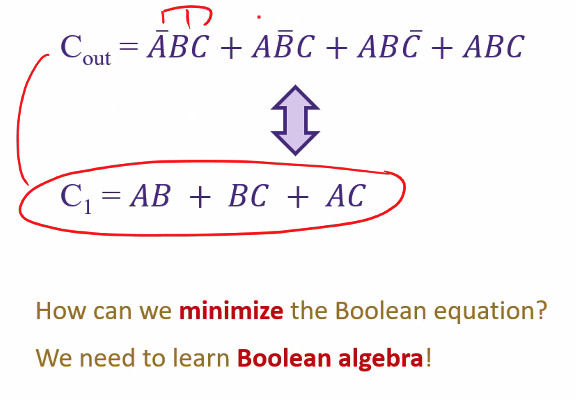

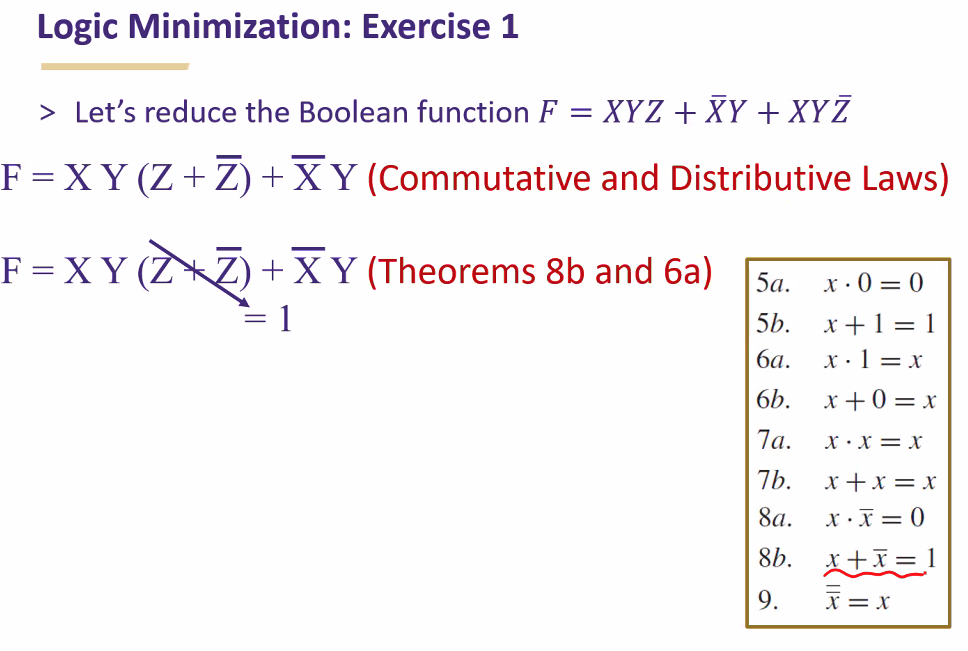

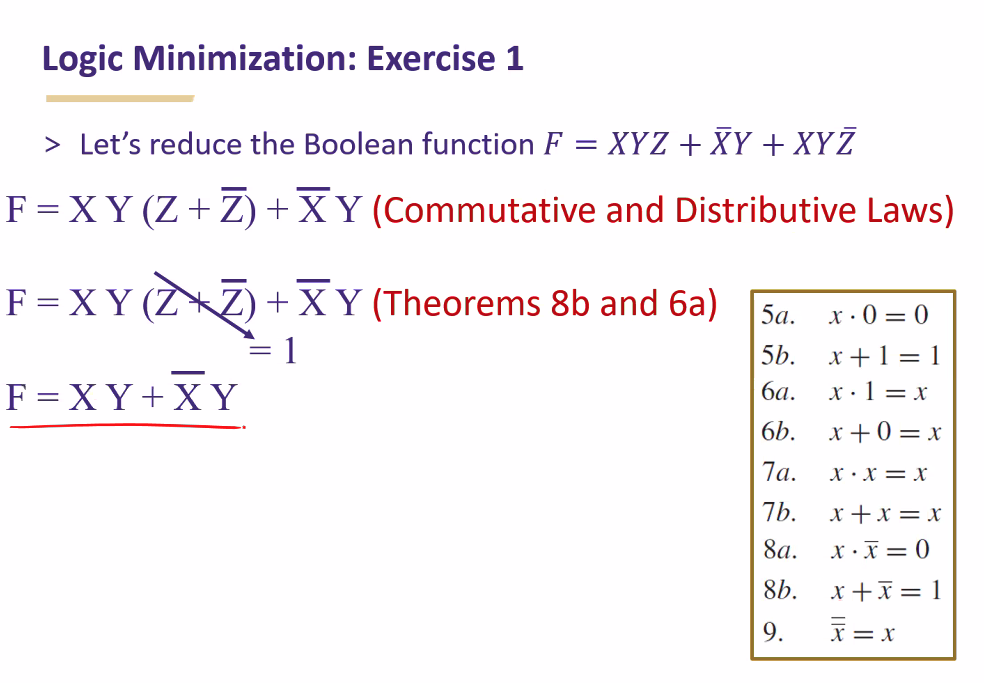

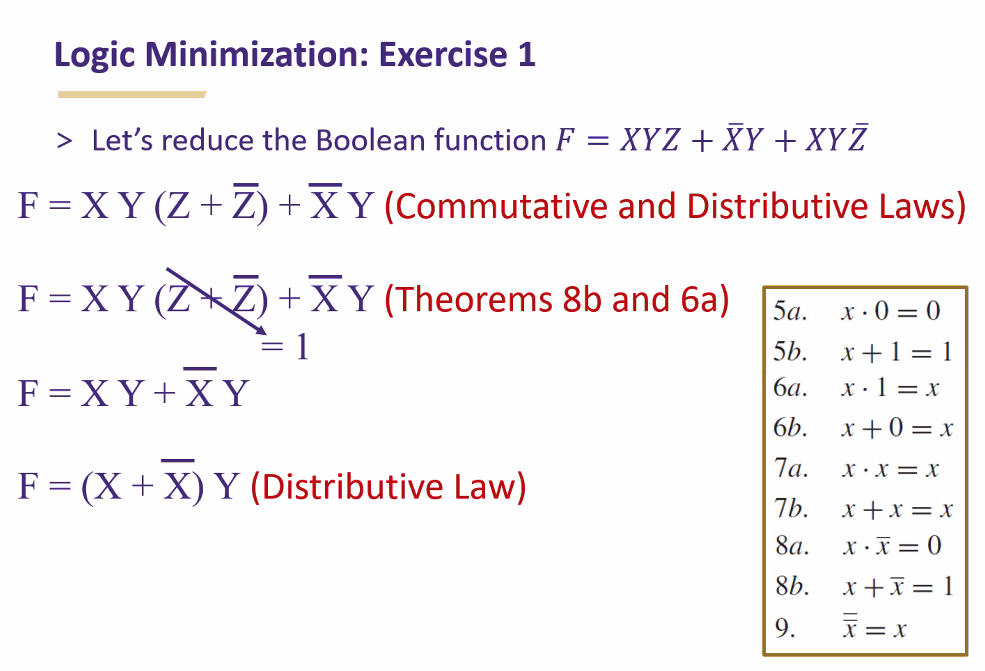

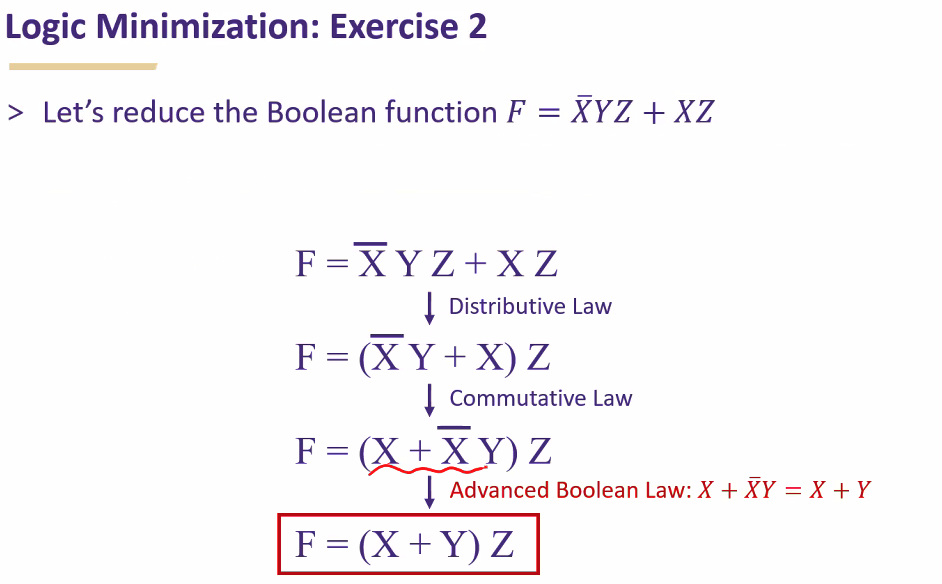

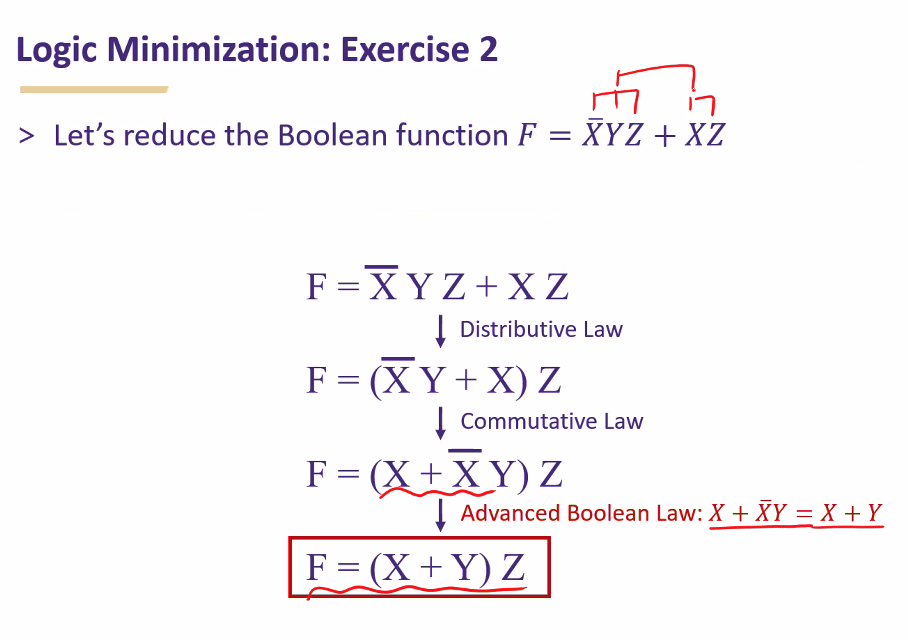

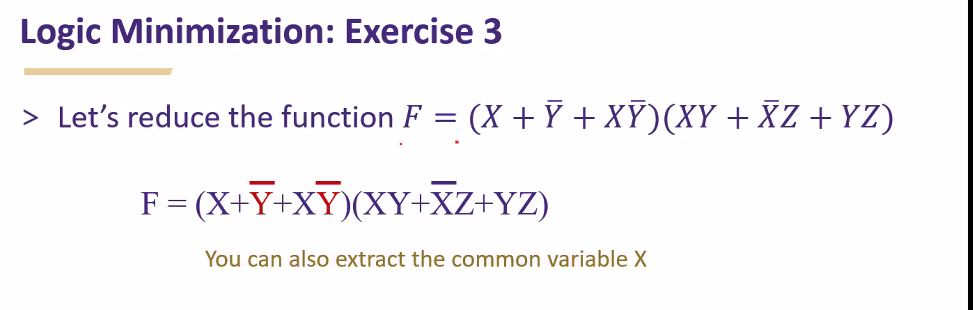

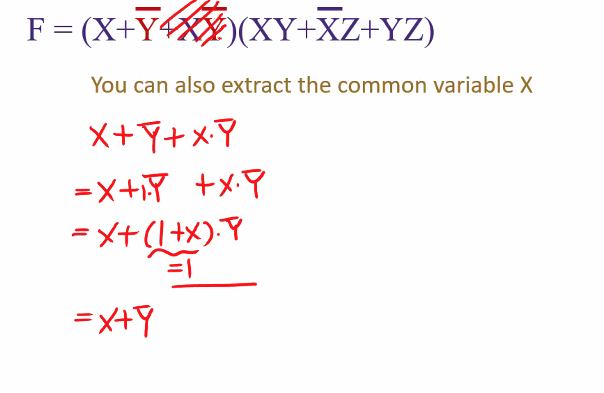

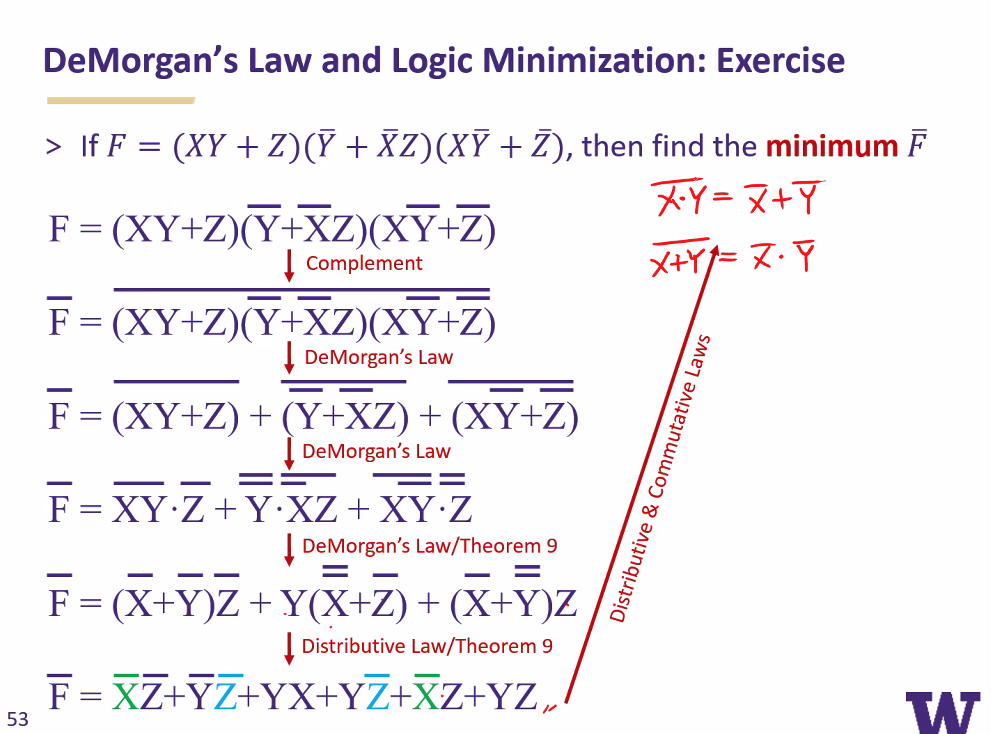

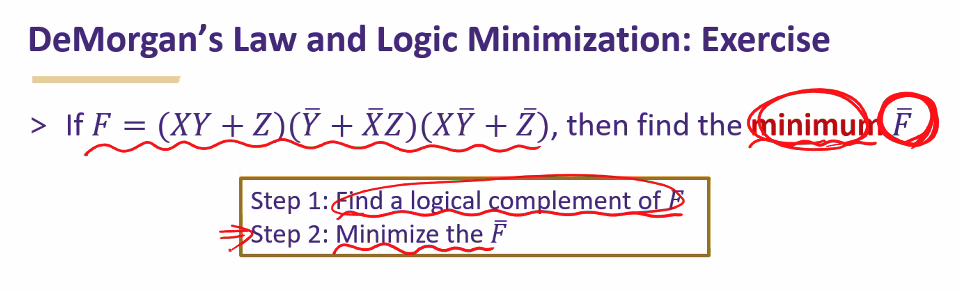

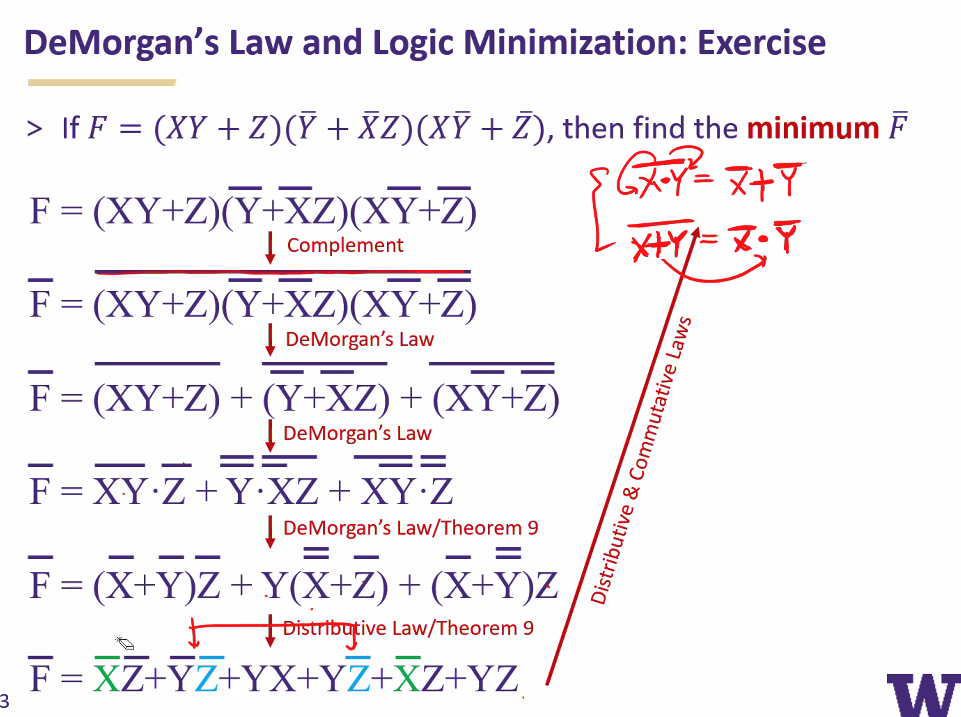

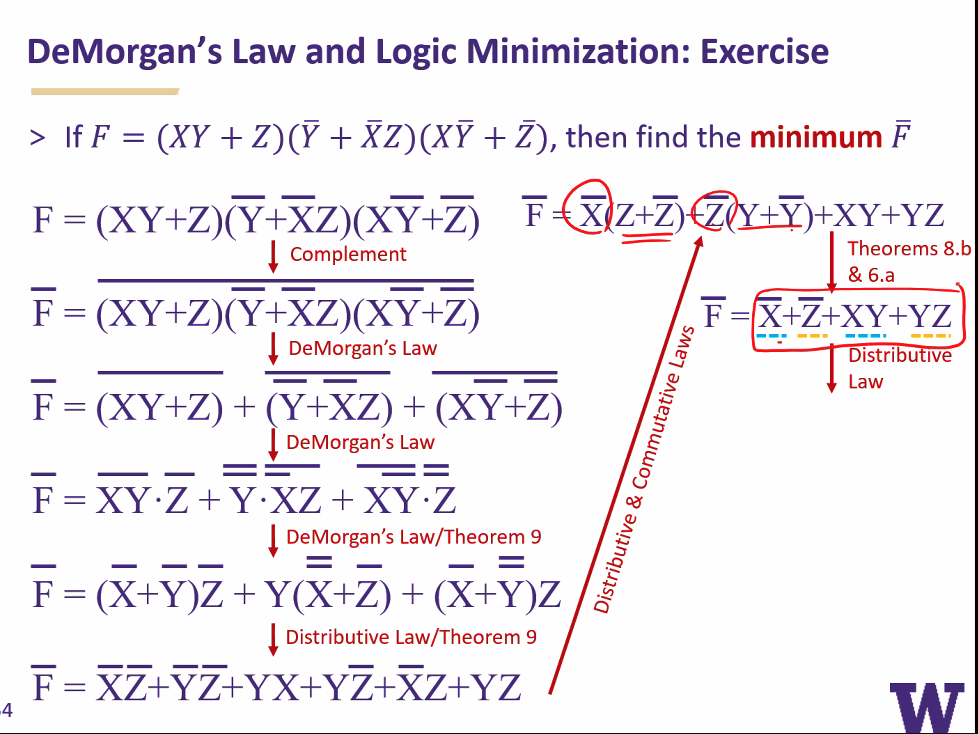

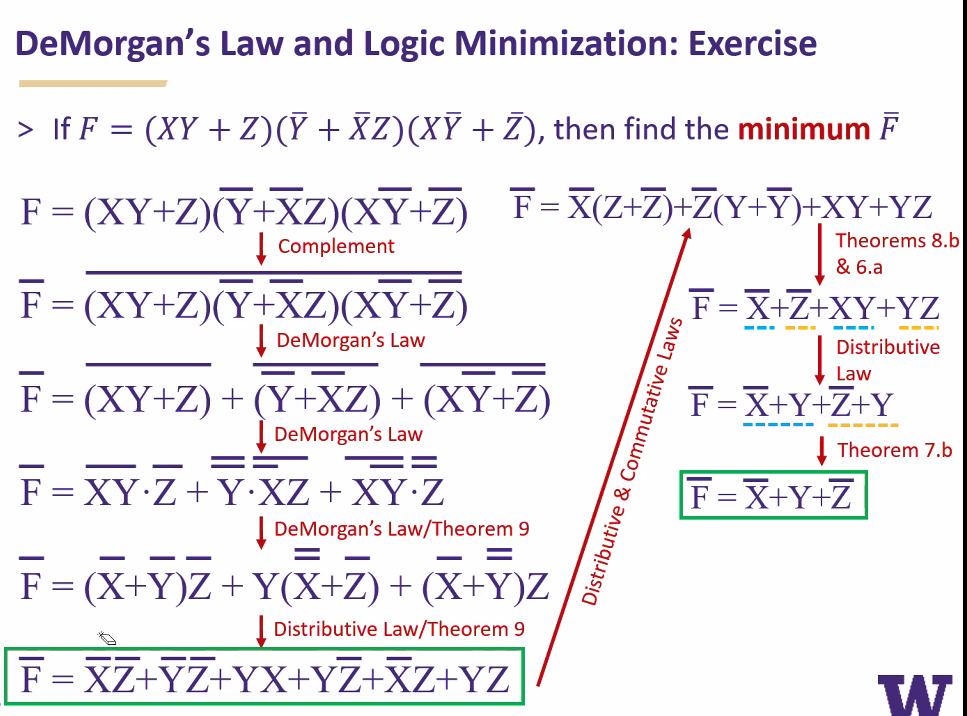

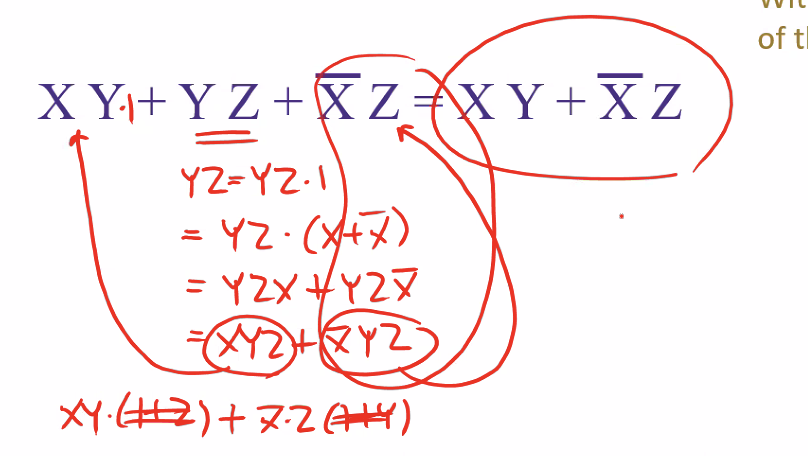

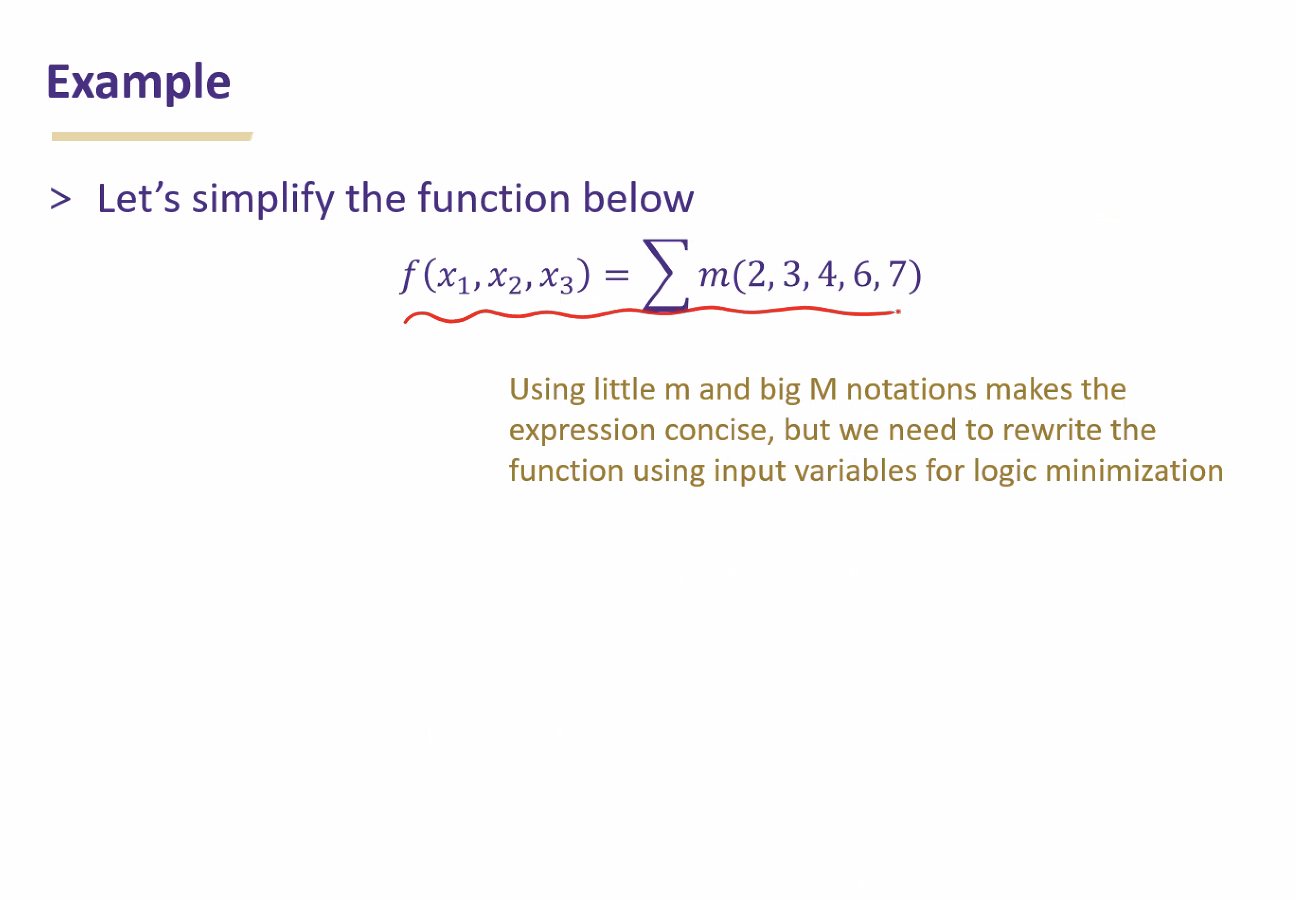

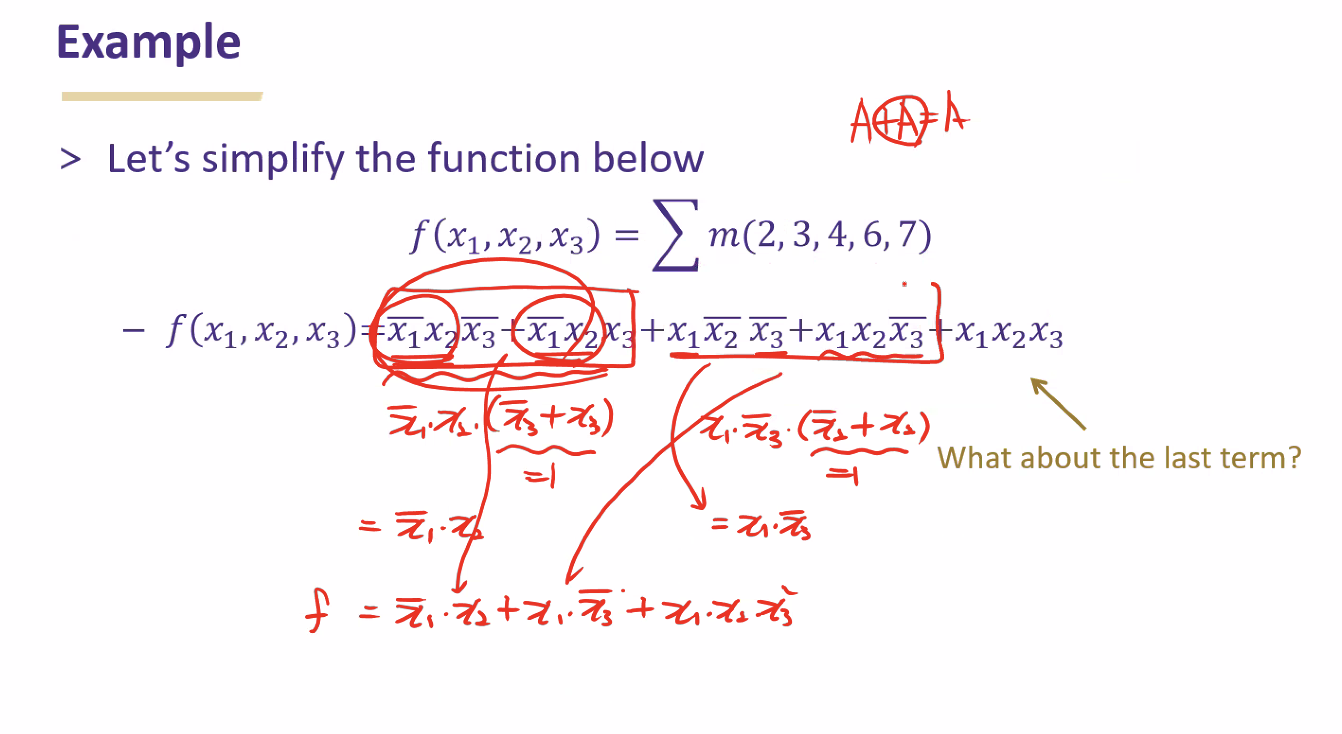

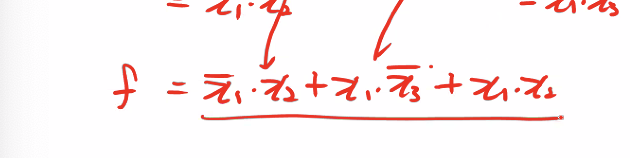

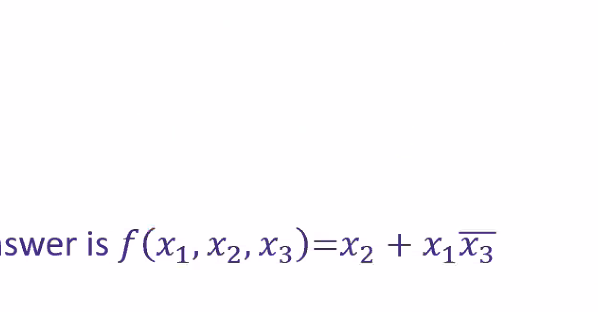

Boolean Algebra and Logic Minimization

Day 2

Review

Symbols and notation

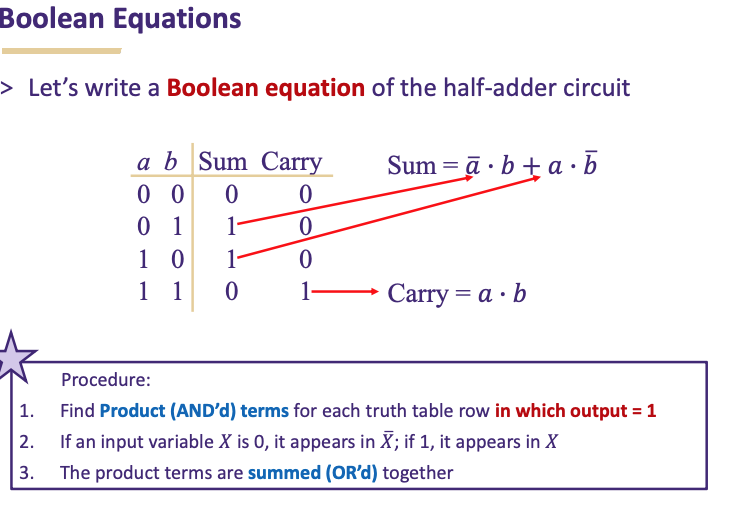

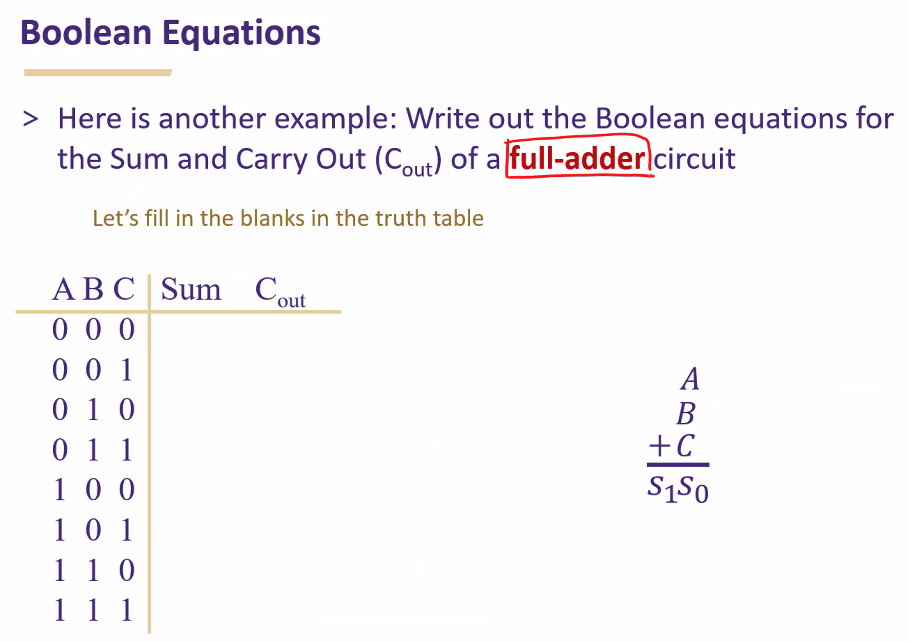

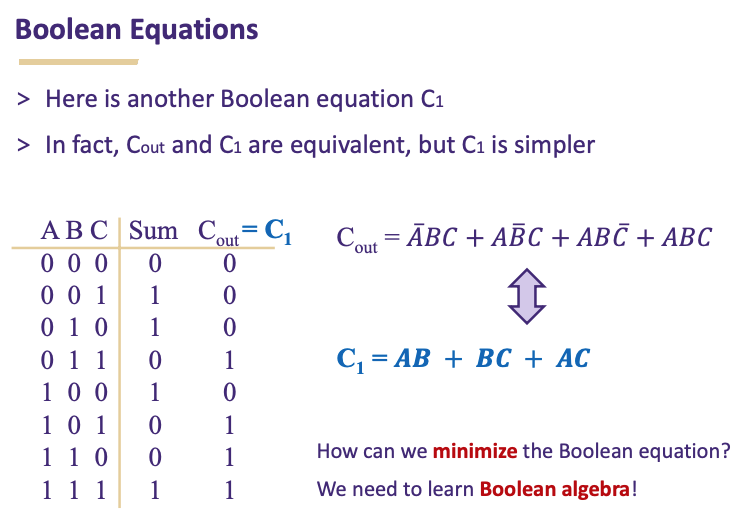

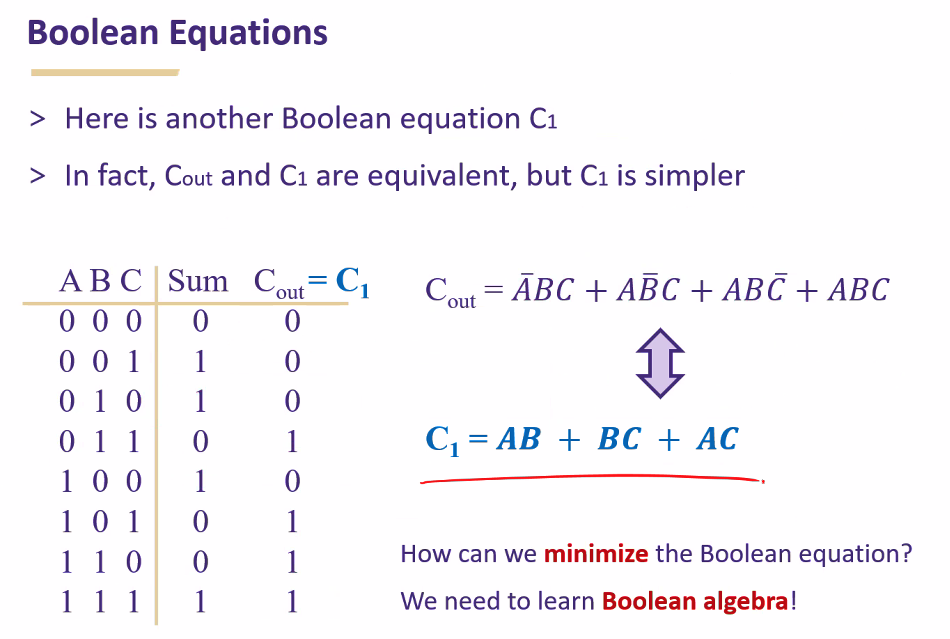

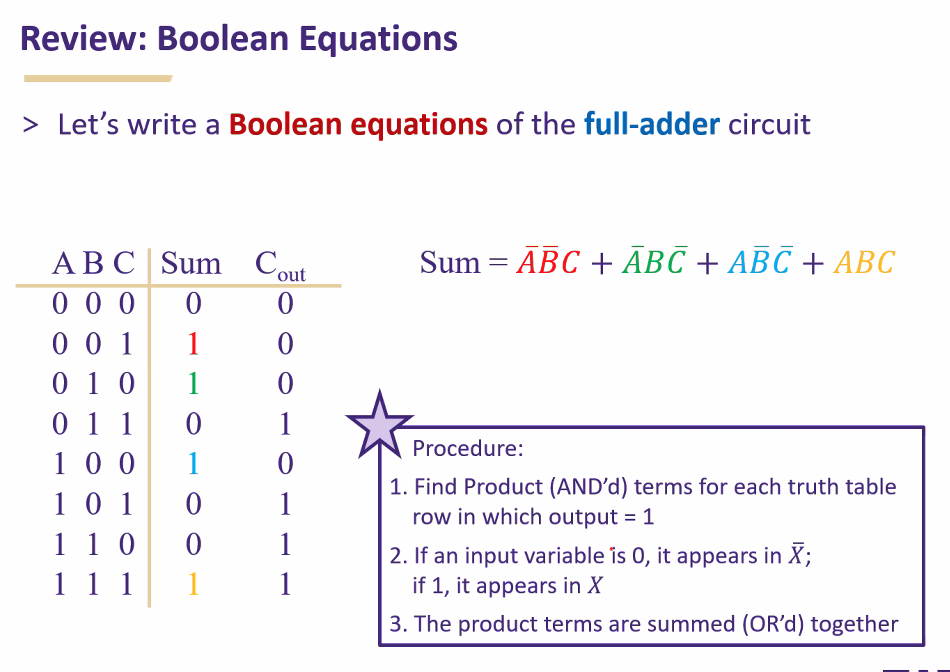

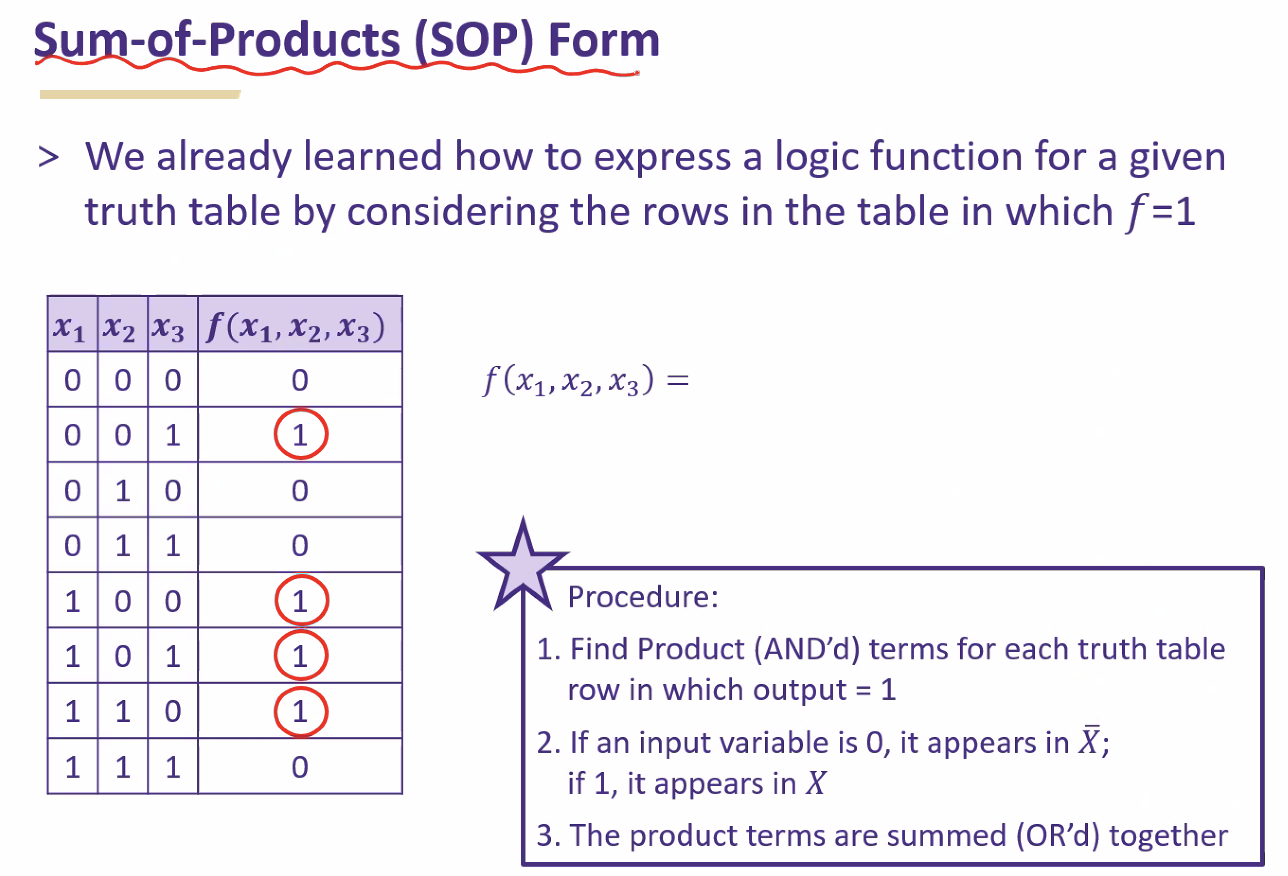

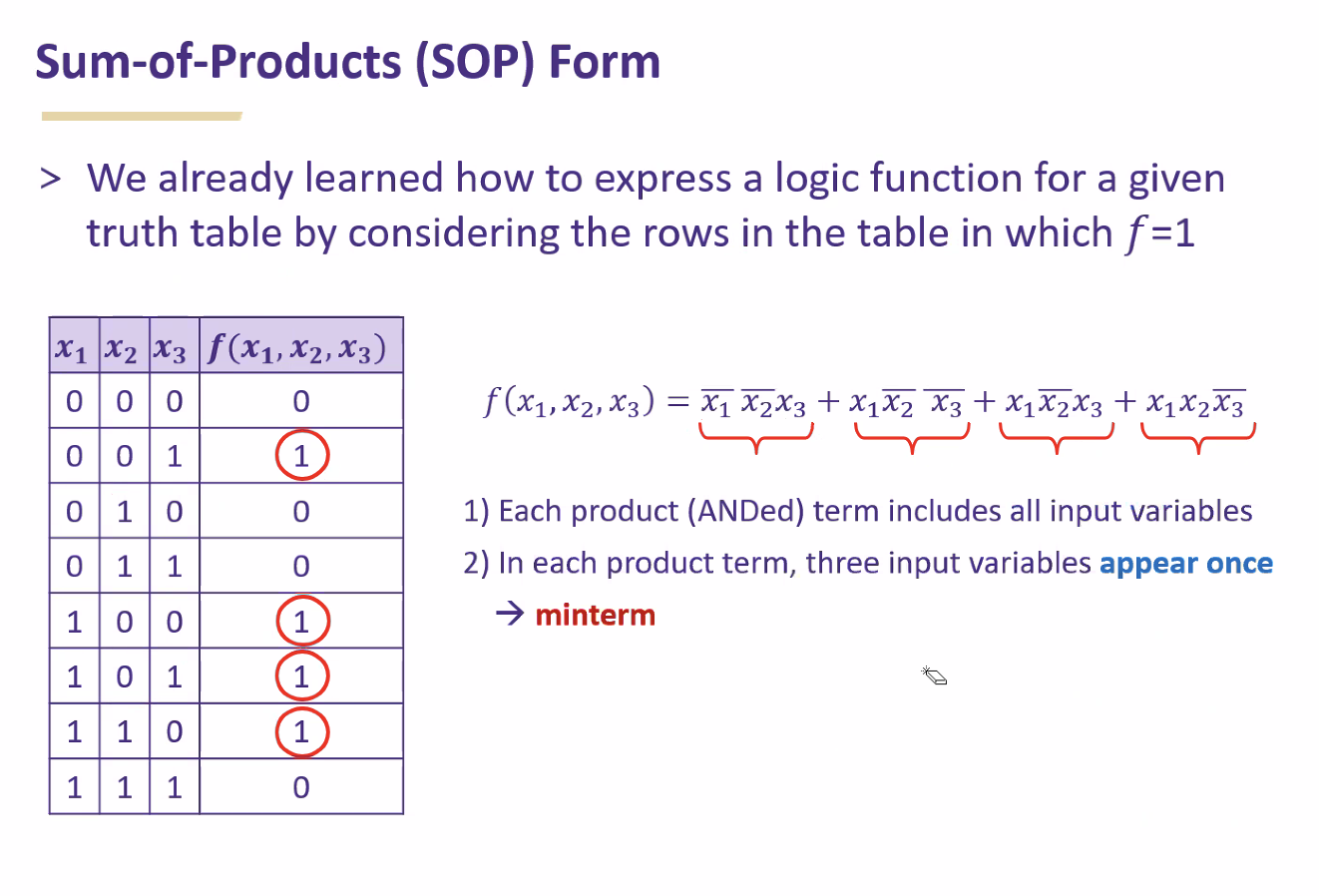

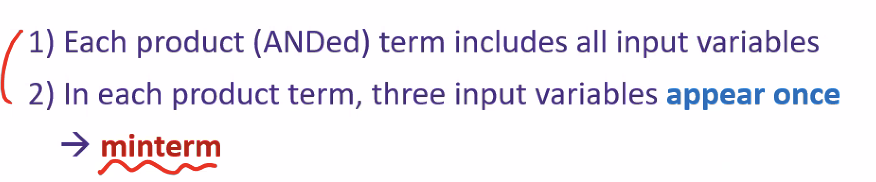

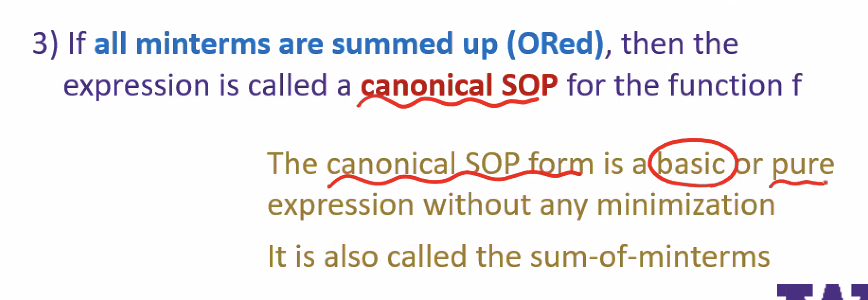

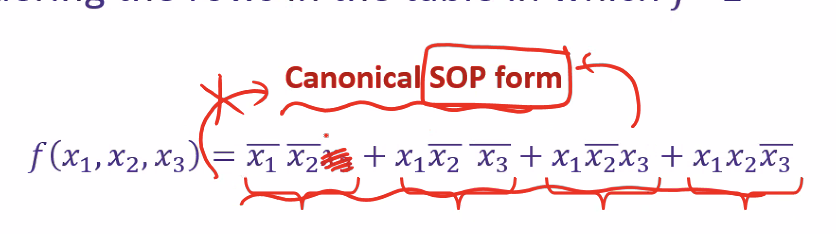

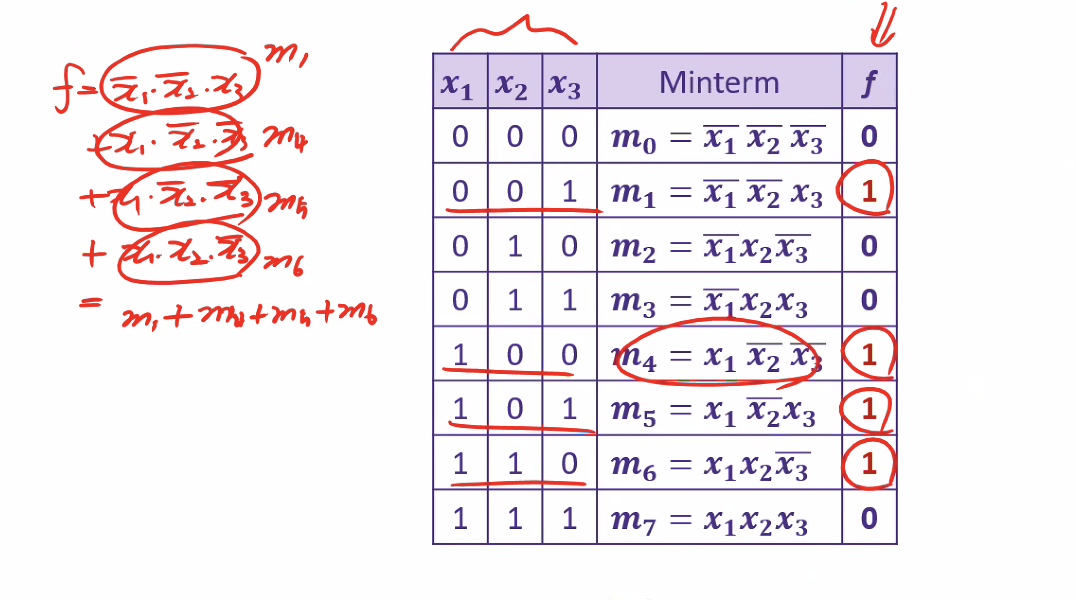

Boolean Equations from a truth table

C1 is equivelent to Cout

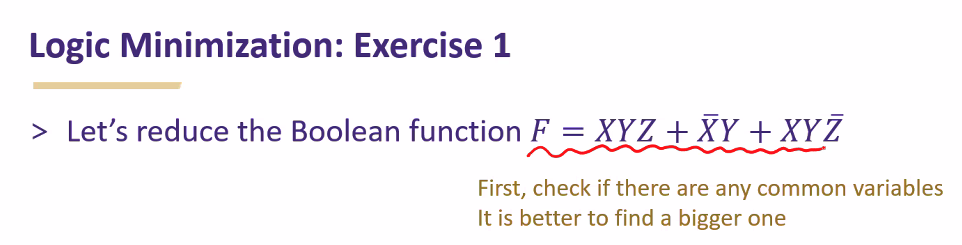

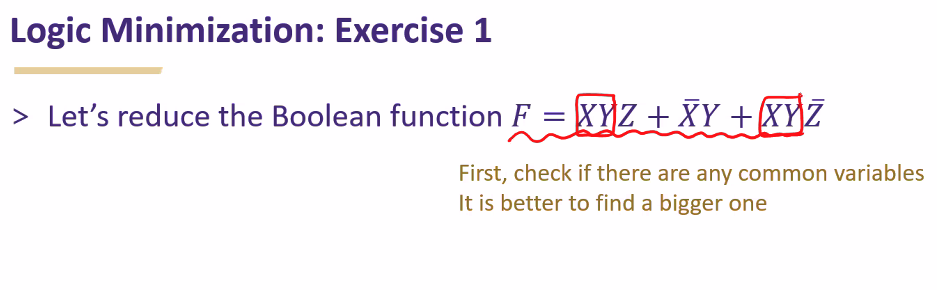

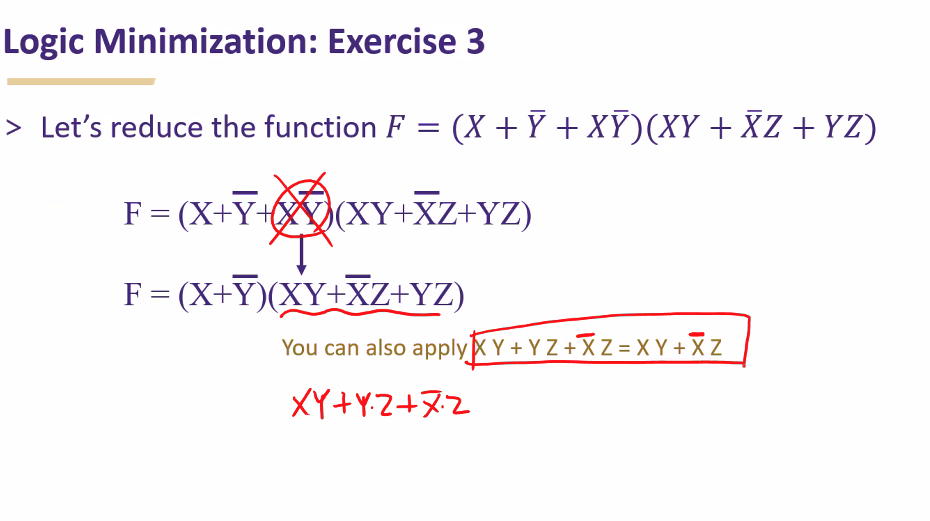

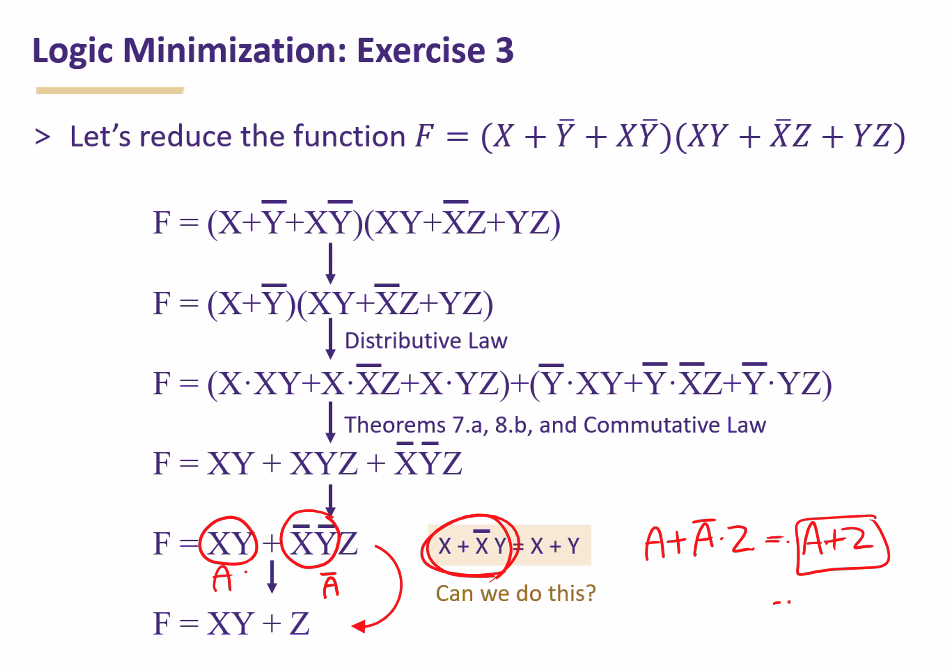

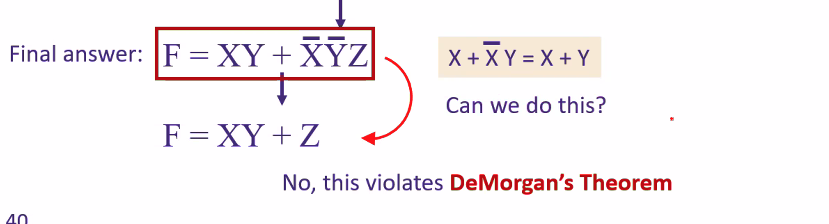

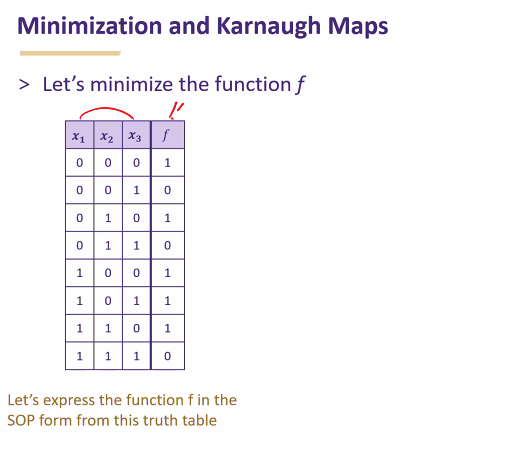

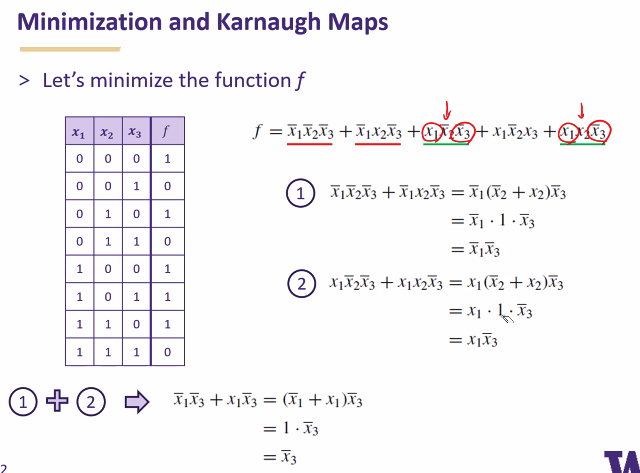

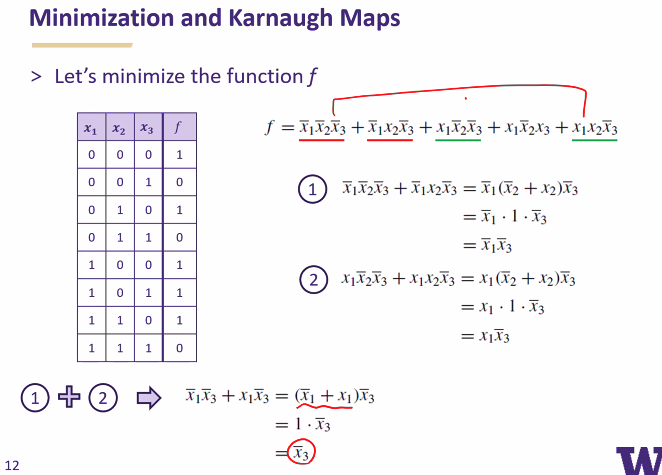

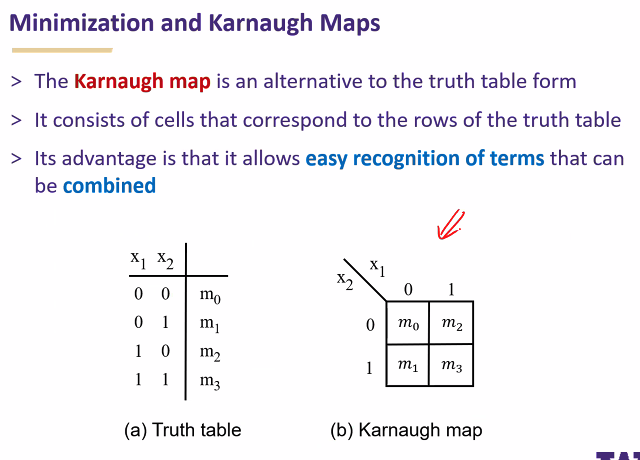

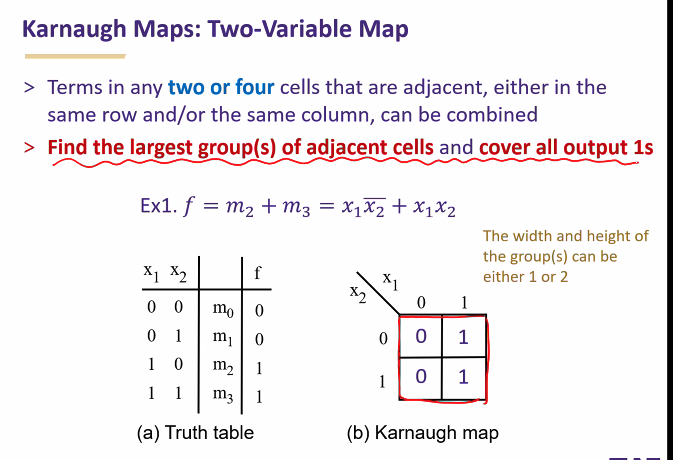

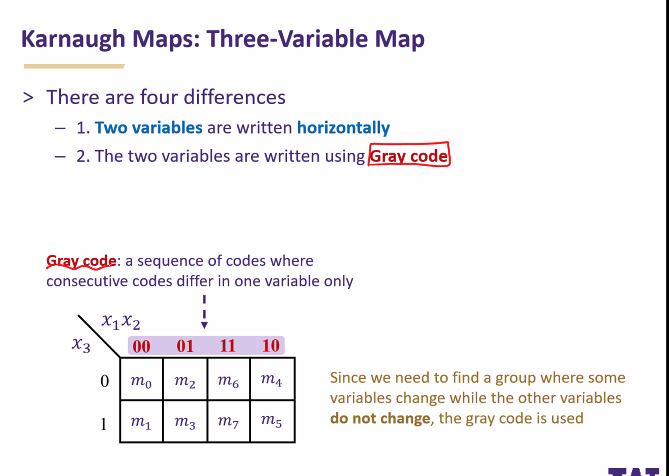

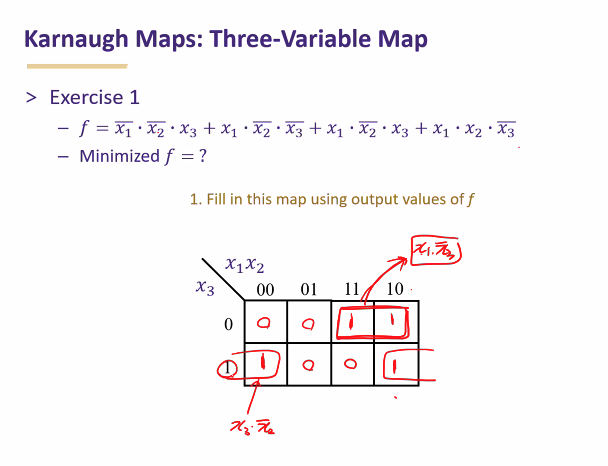

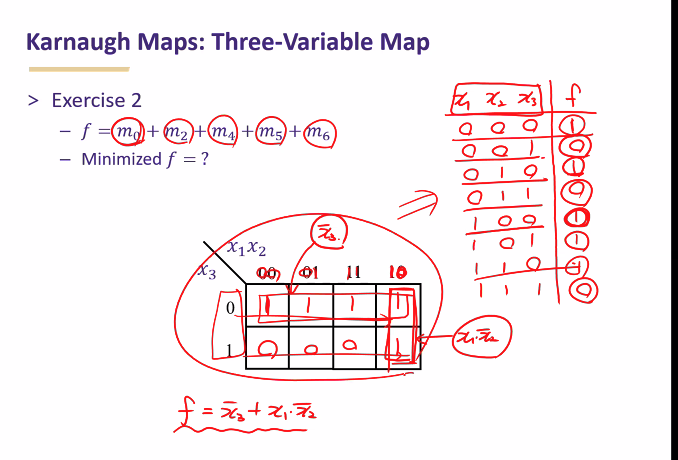

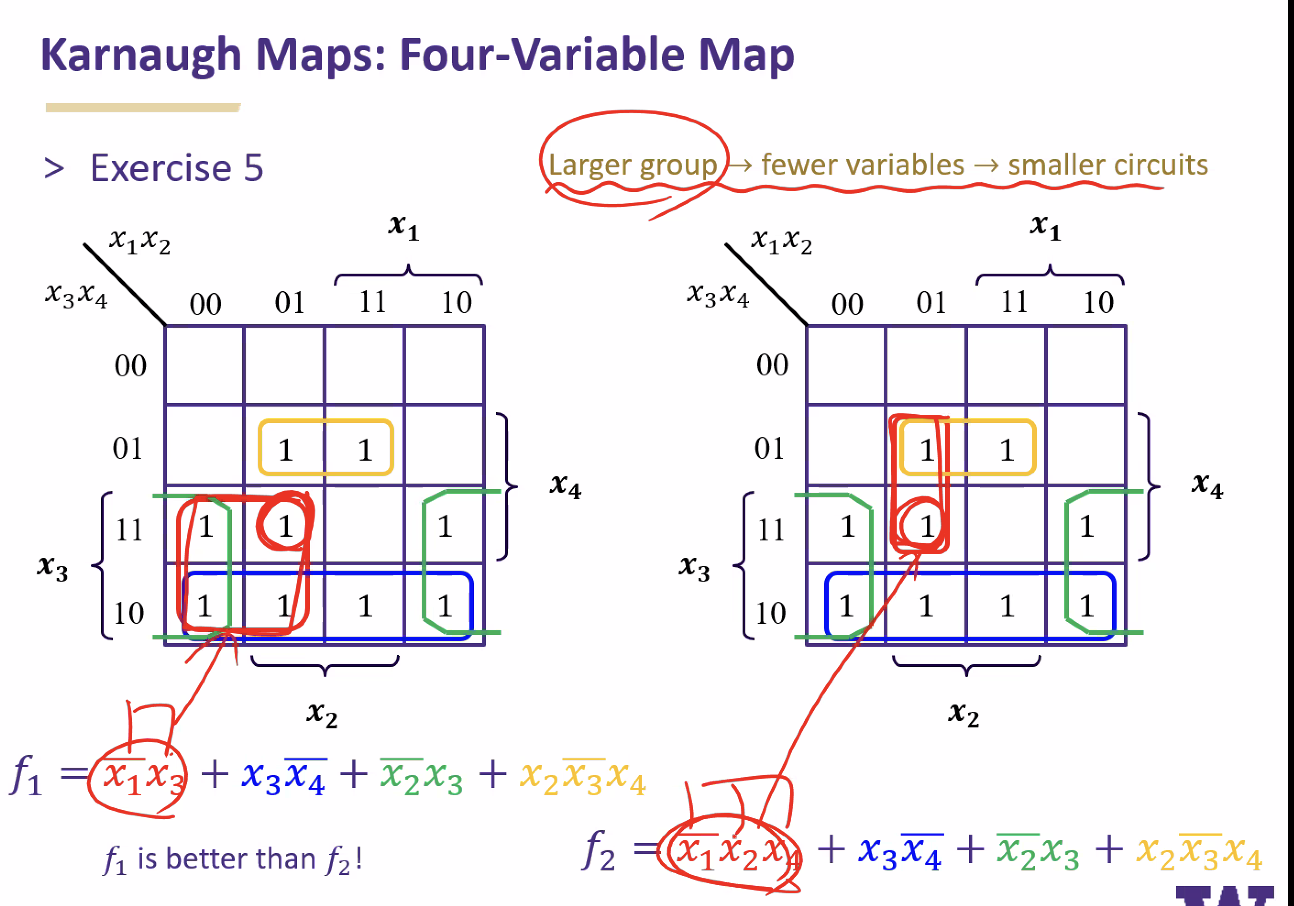

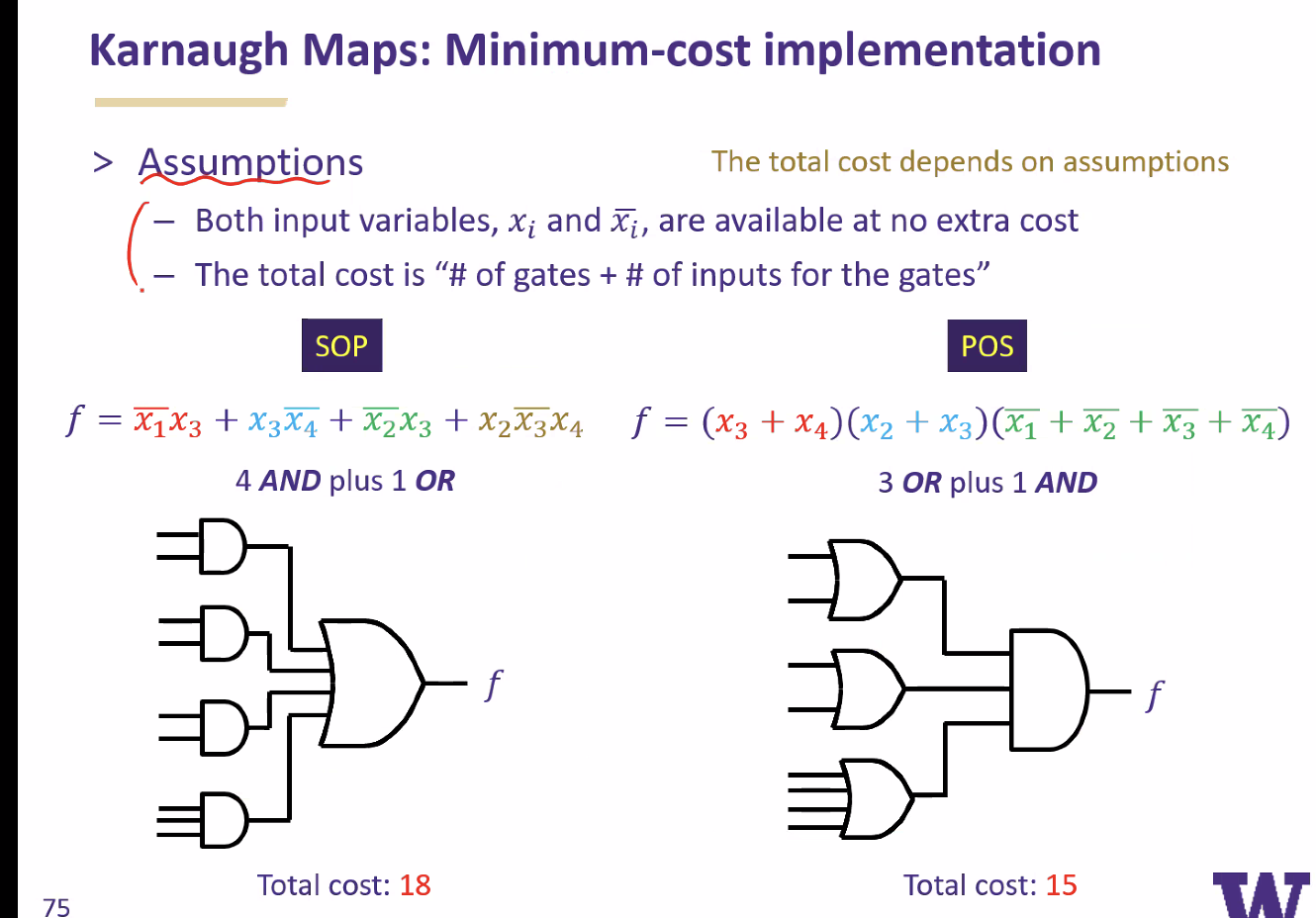

How can we minimize the boolean equation?

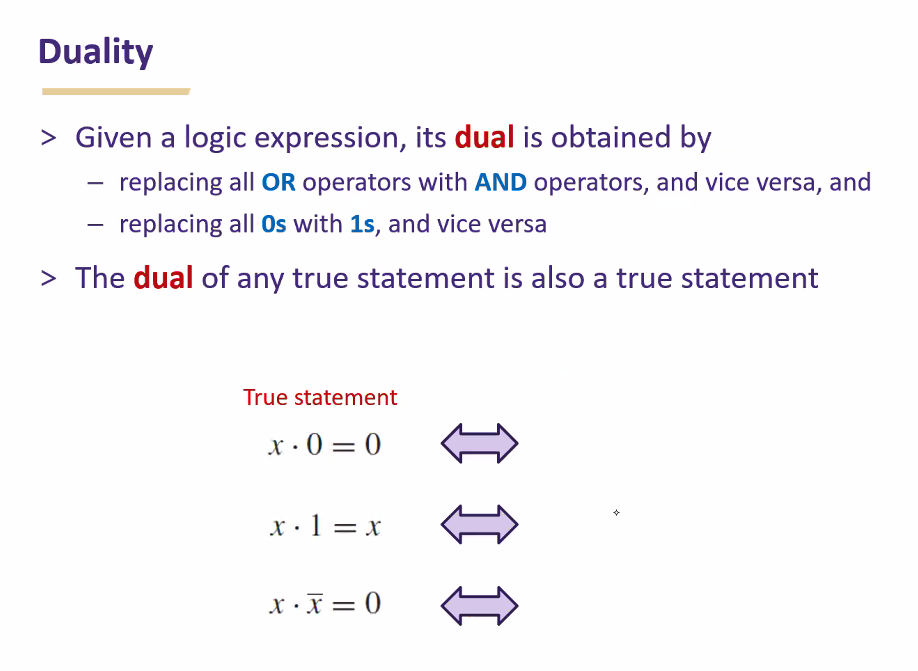

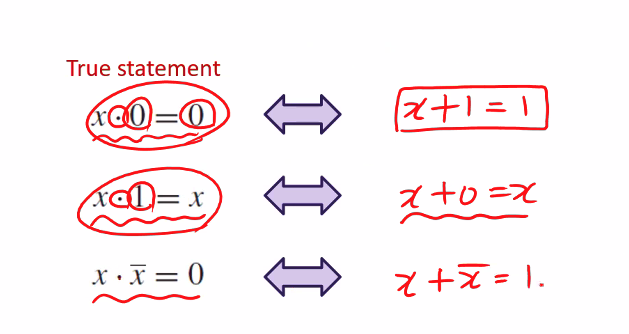

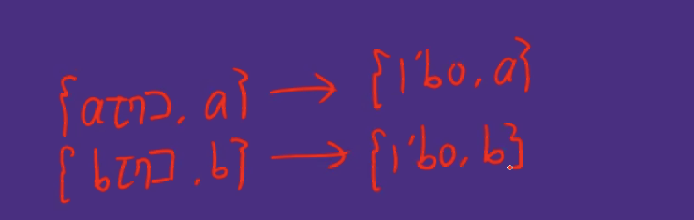

Duality

given a logical expression, it's dual is obtained by replacing all or operators with and operators and vise versa

repalcing all 0s with 1s

the dual of any true statement is also a true statement

if a statment is true, it's dual is also true

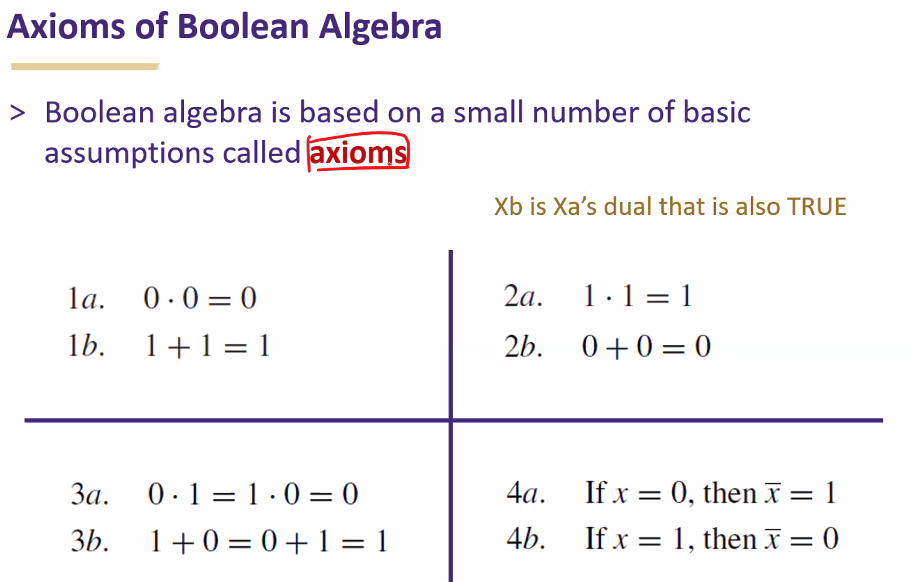

Axioms of boolean algebra

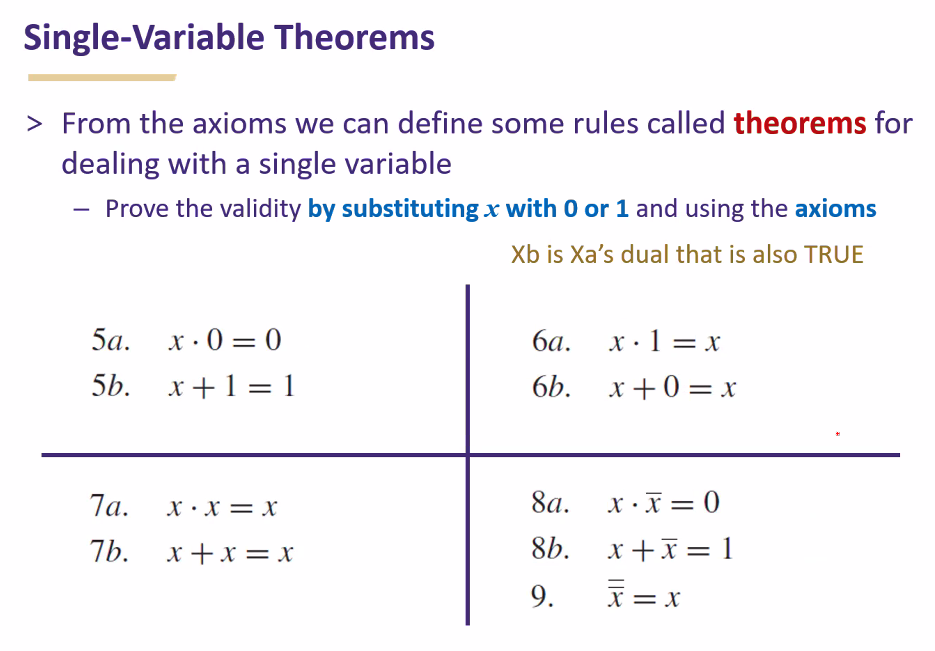

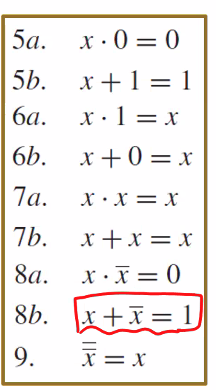

Single variable theorums

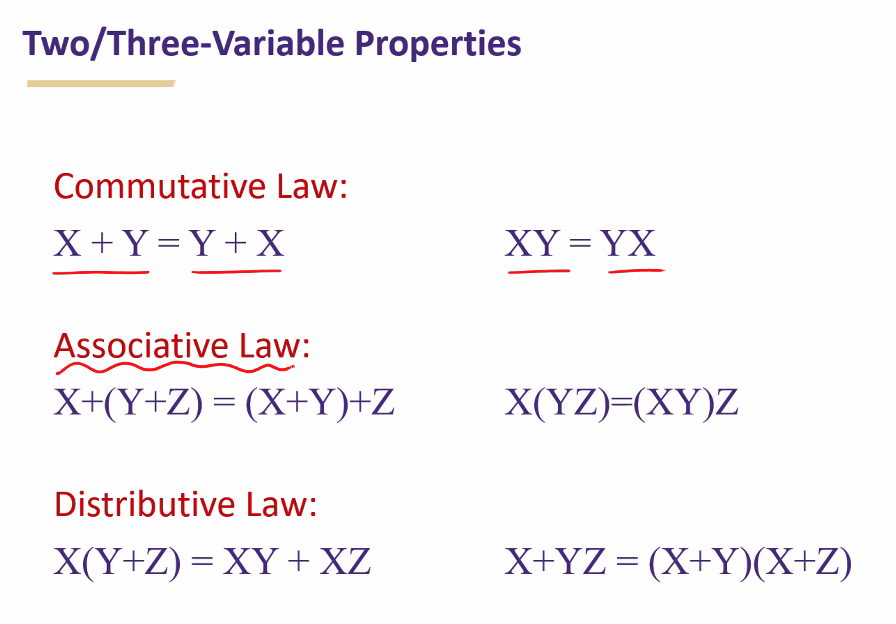

Two/Three Variable Properties

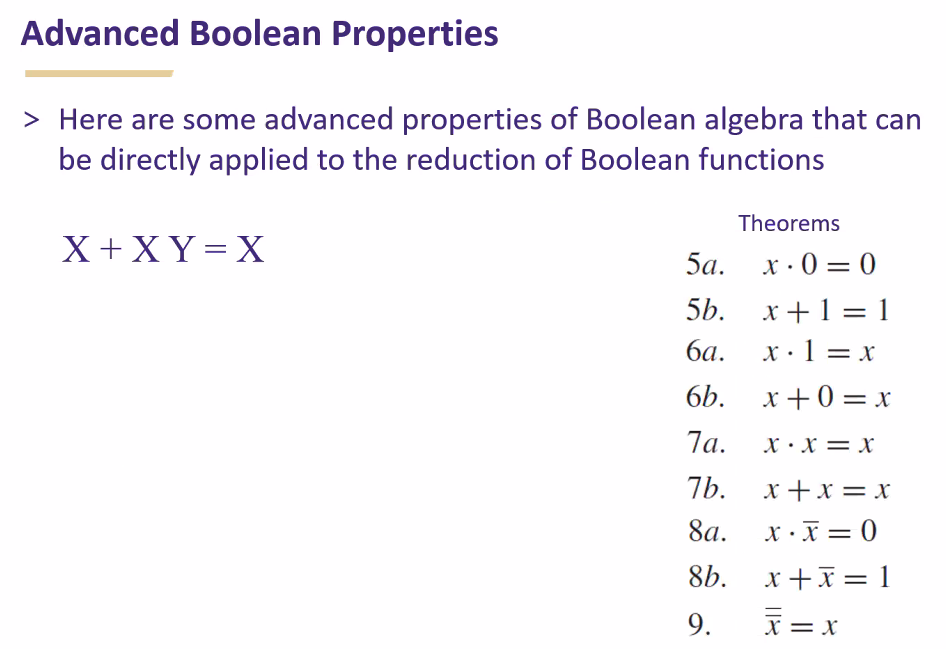

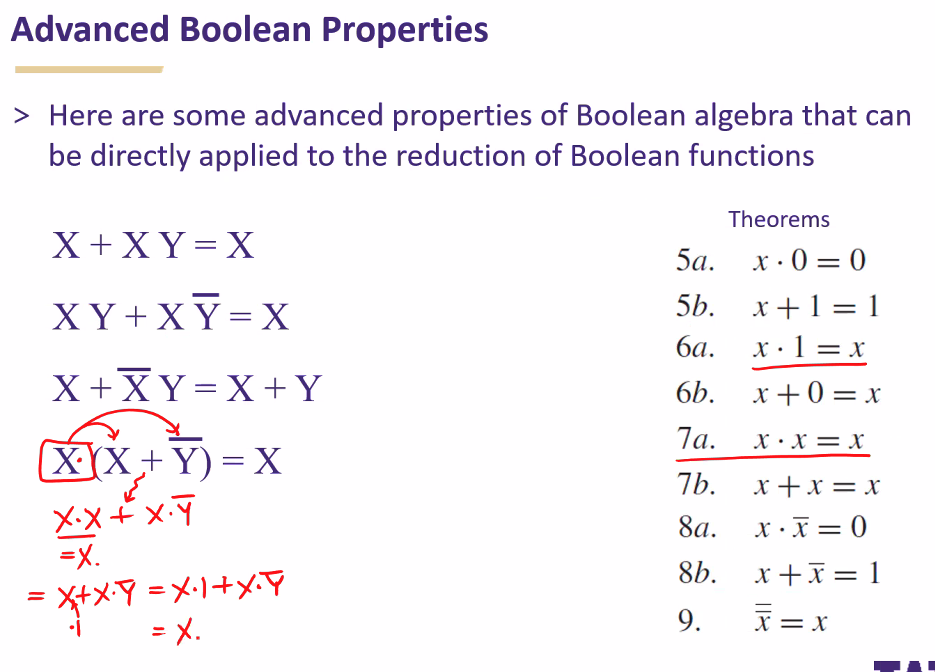

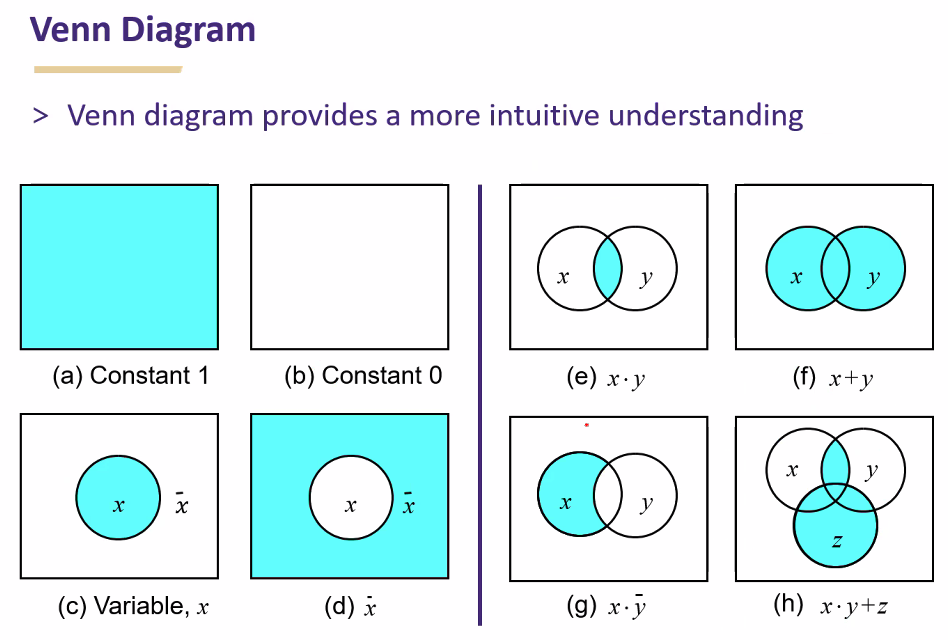

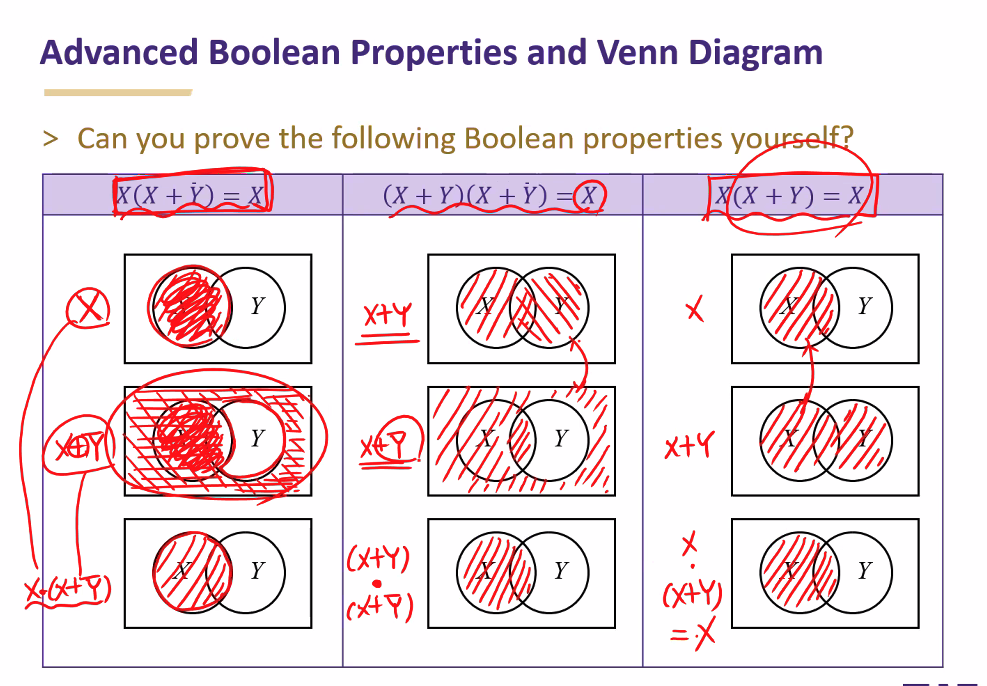

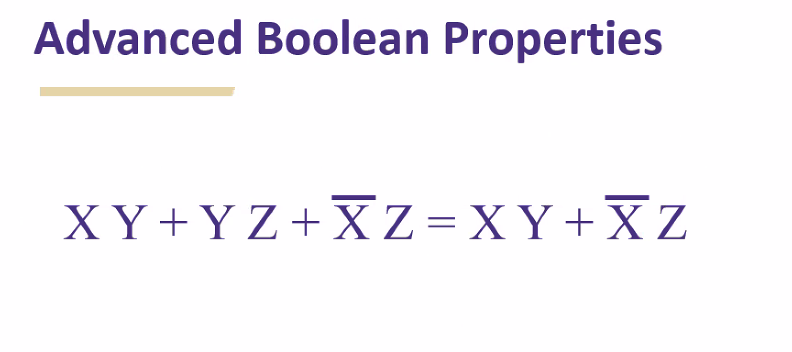

Advancd boolean properties

sometimes you may need to add "and 1" to be able to factor

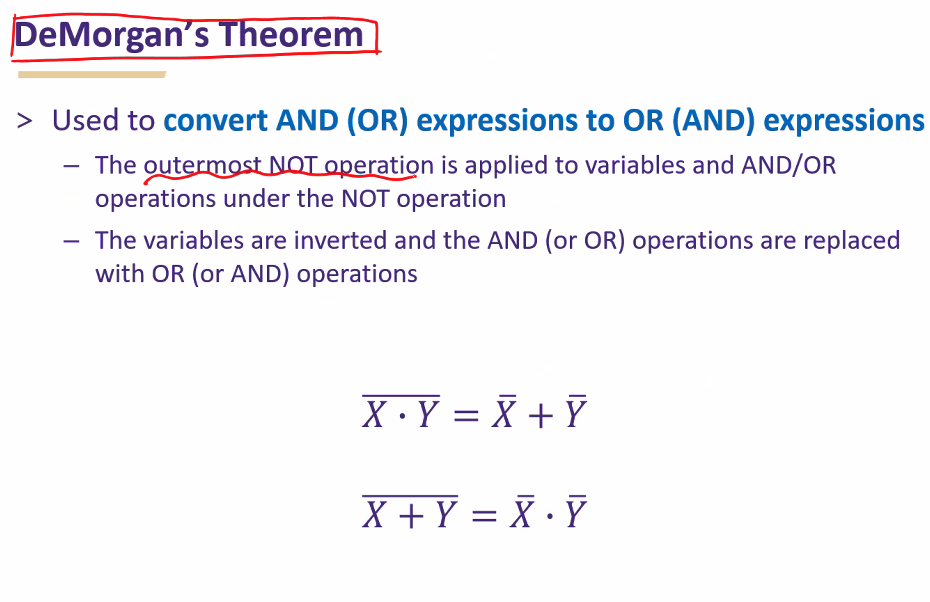

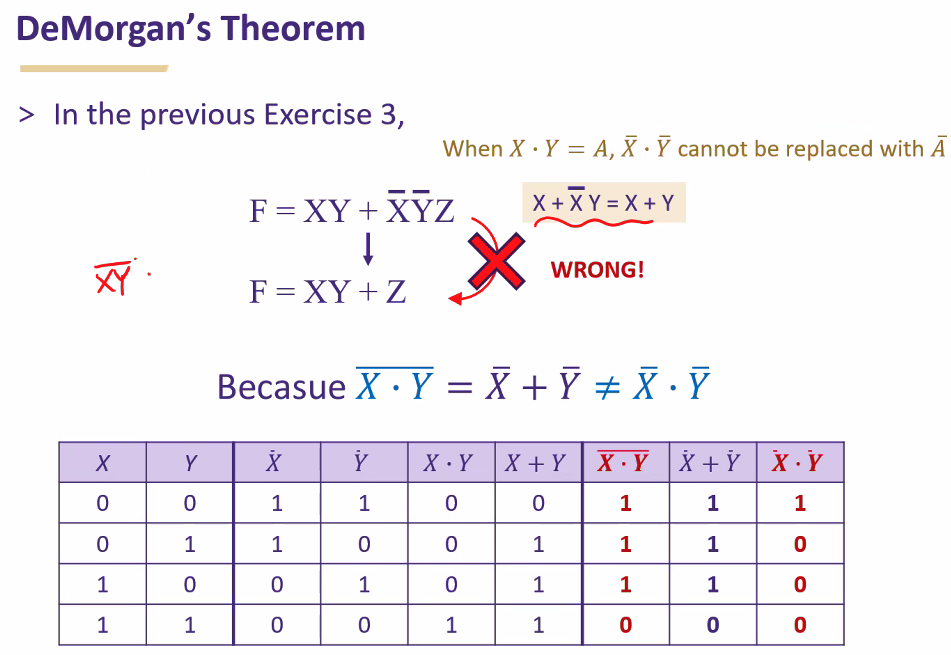

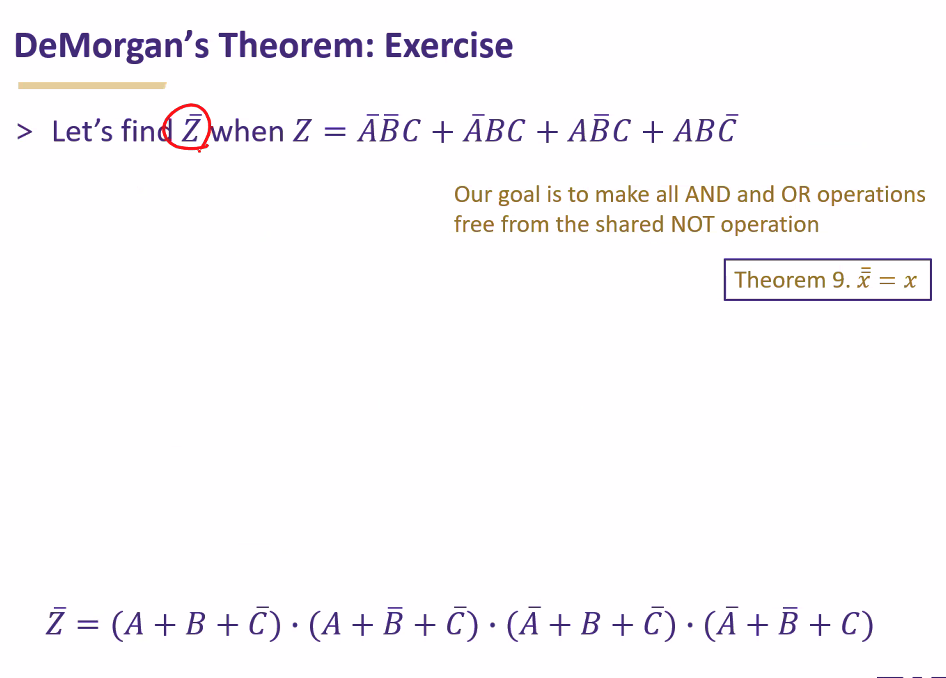

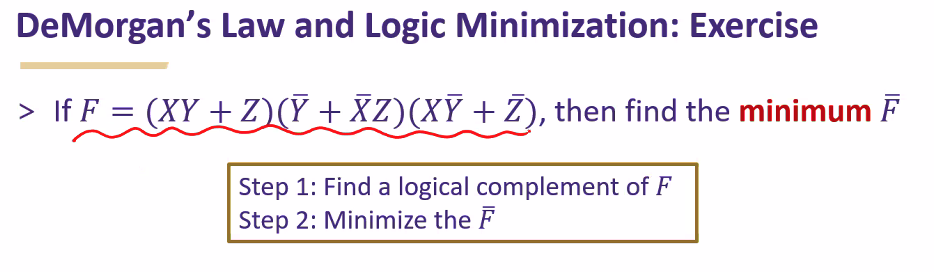

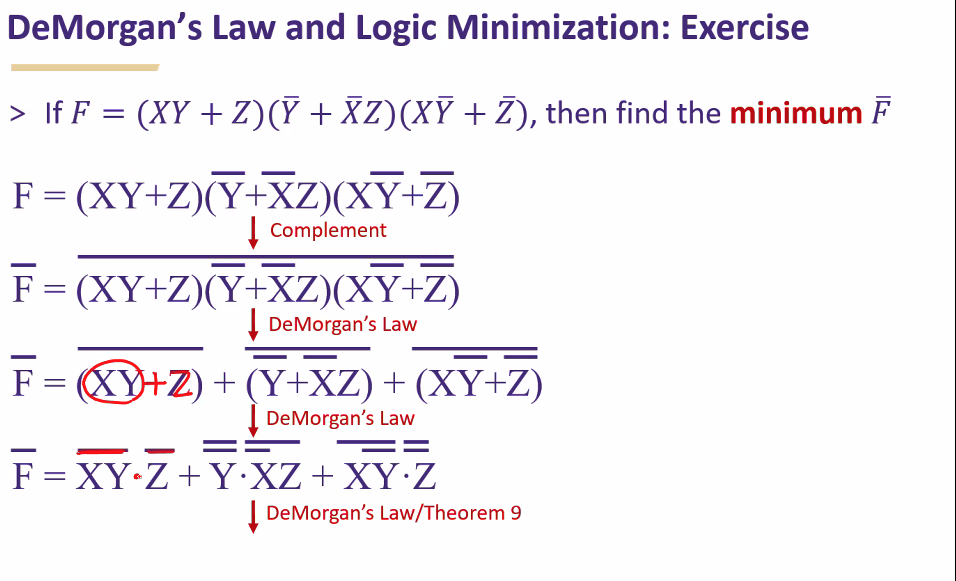

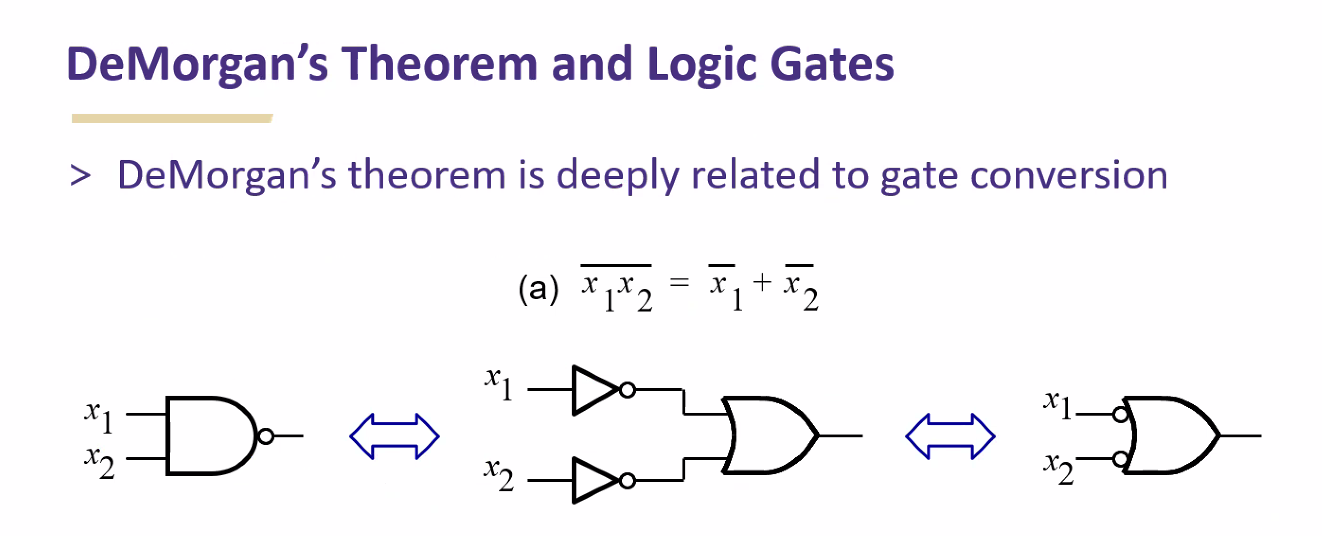

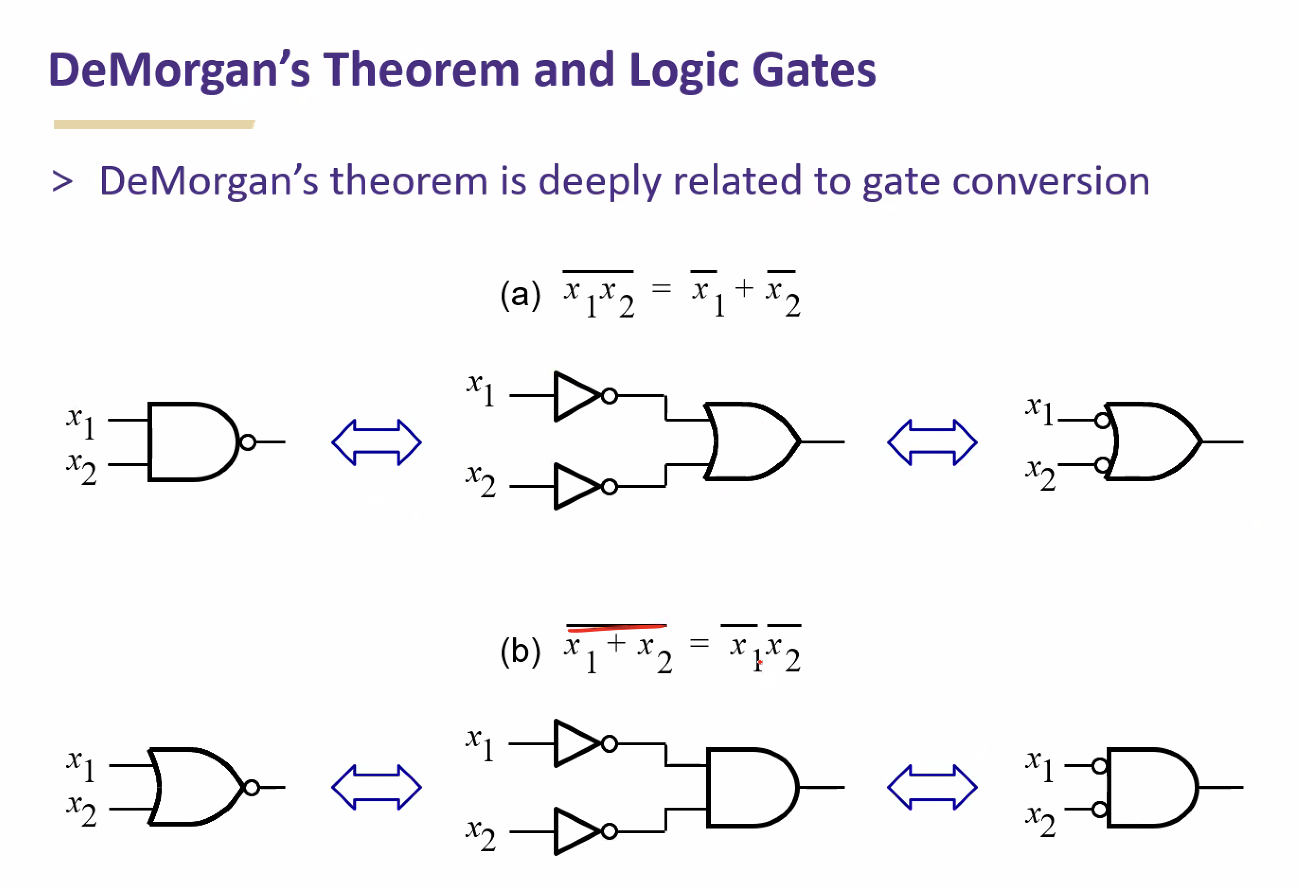

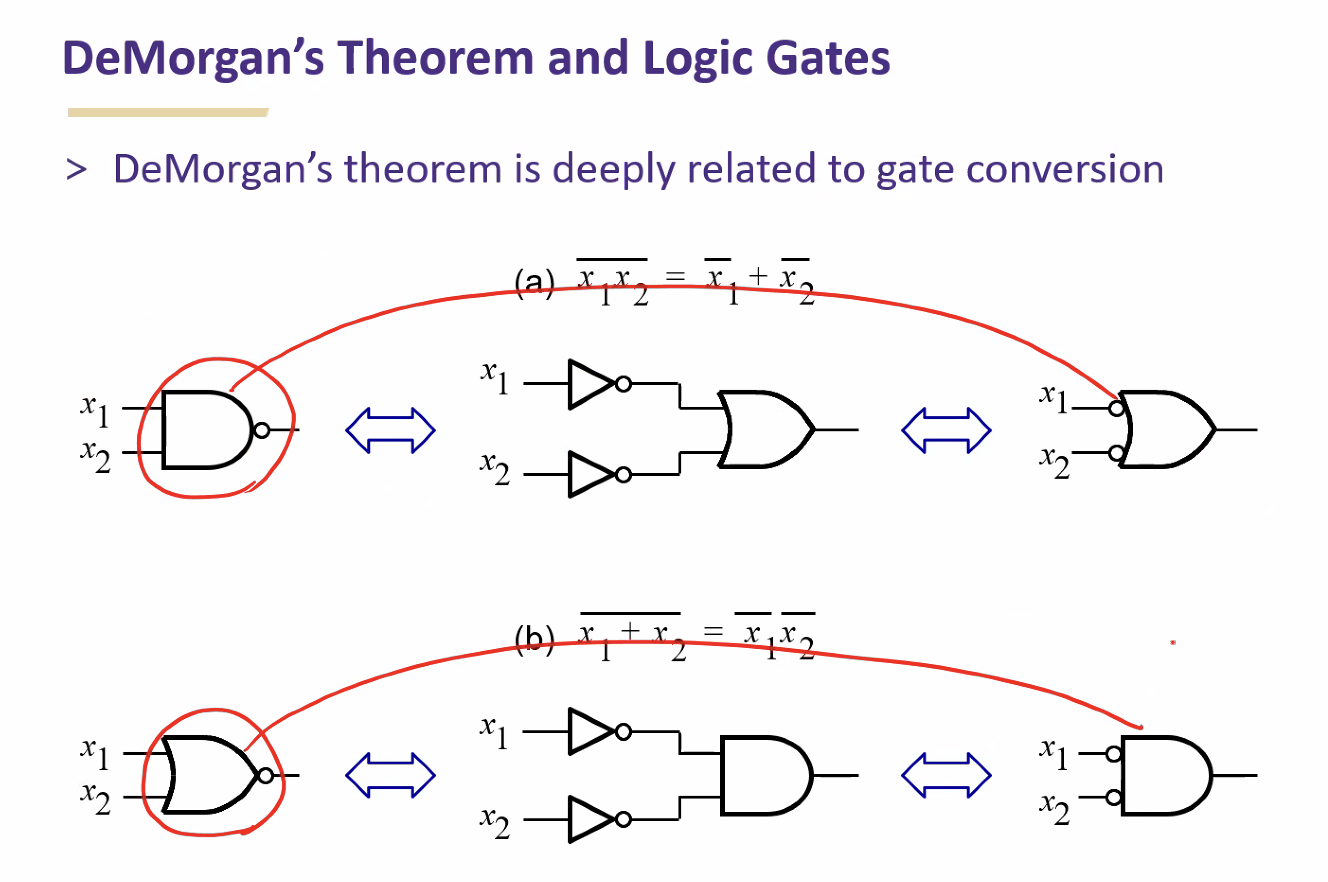

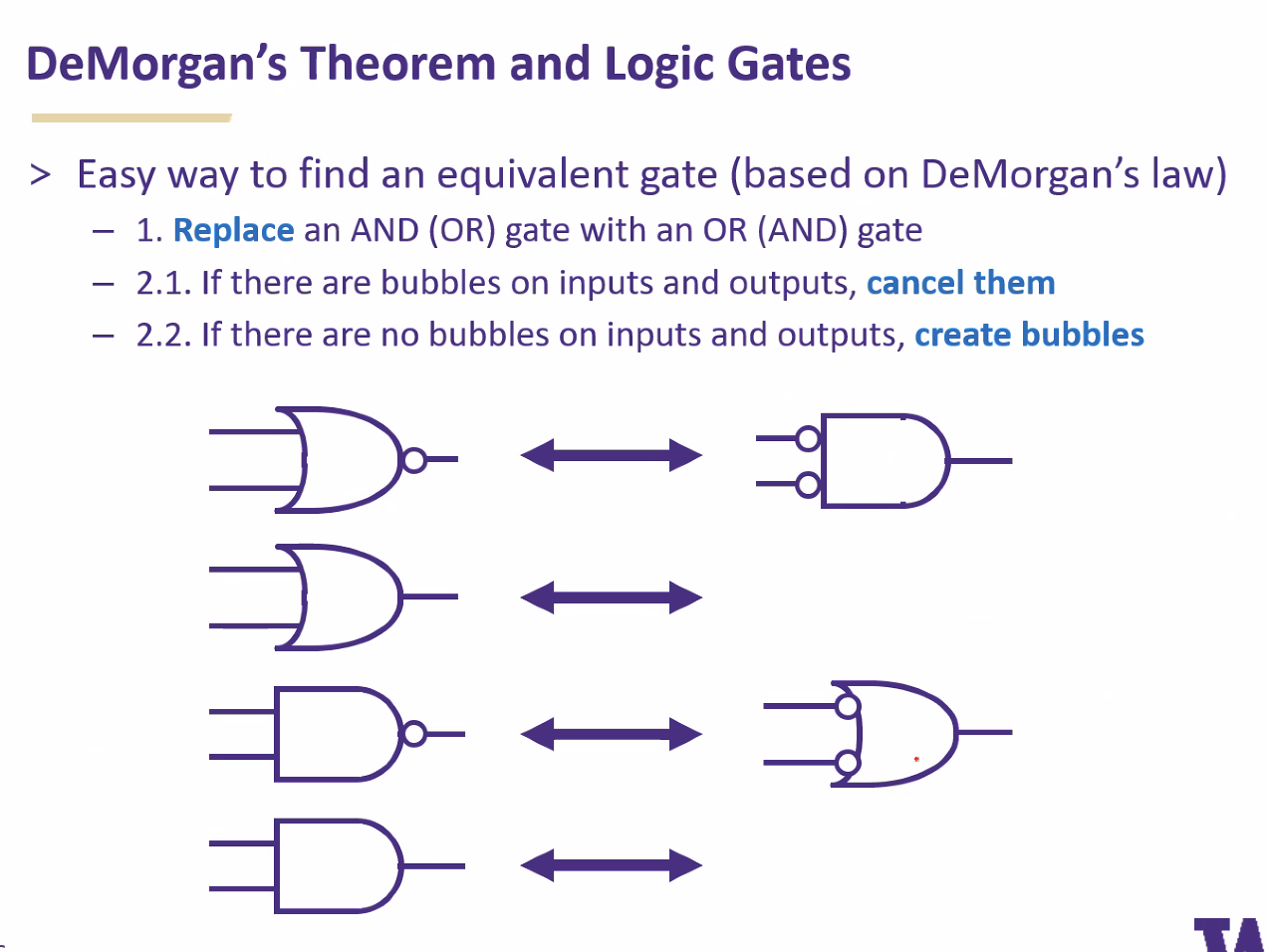

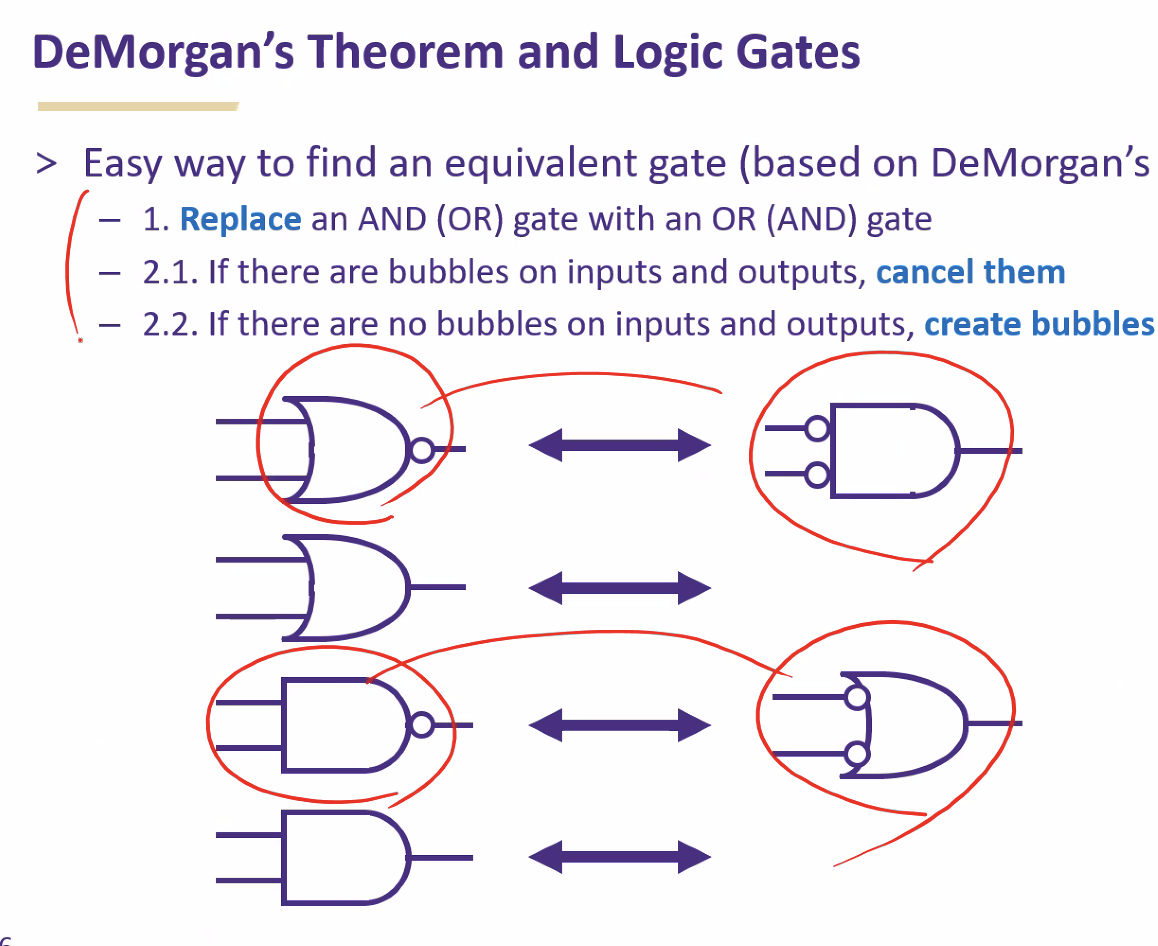

DeMoregan's Theorum is used to convert AND (or) to OR (and)

Day 3

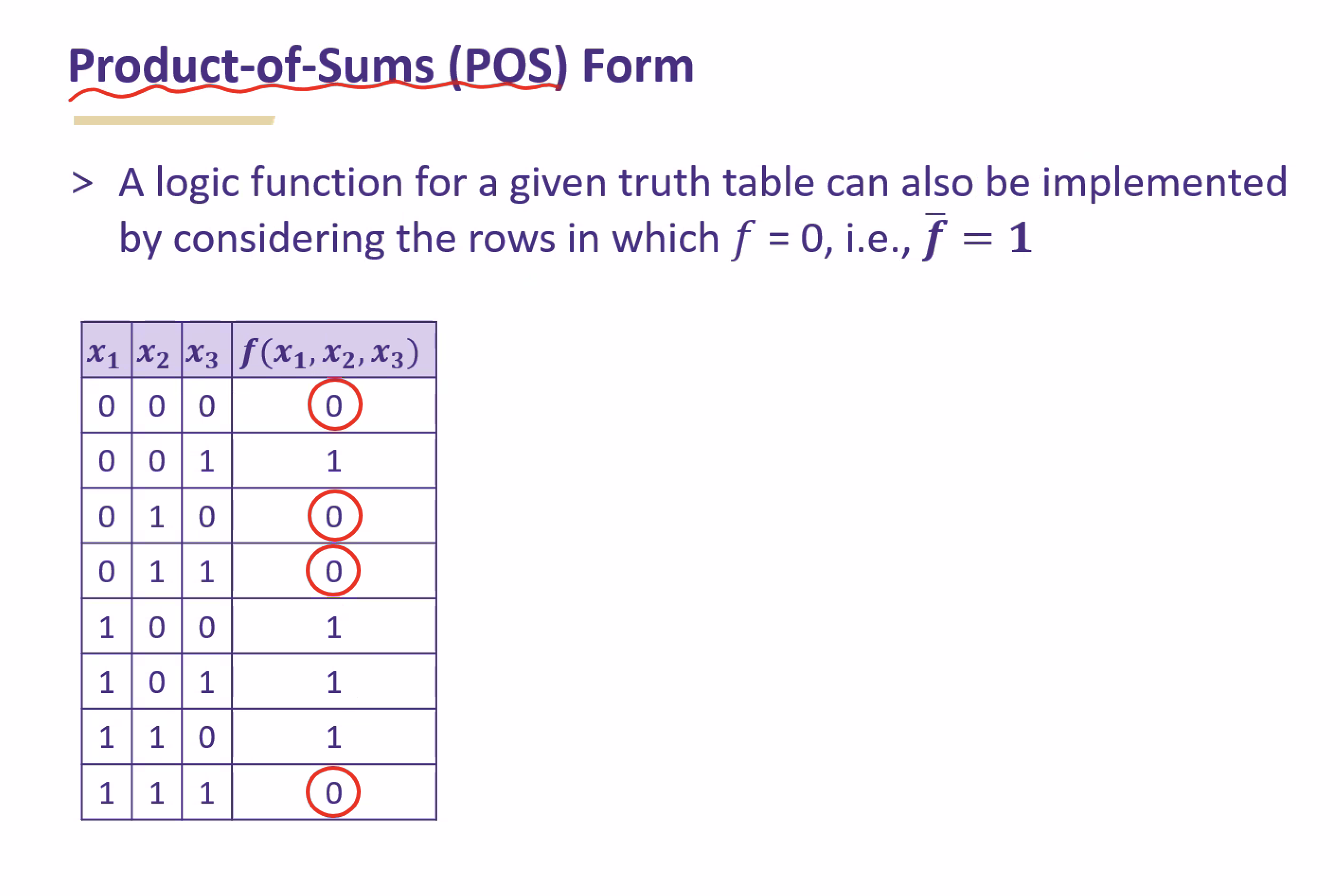

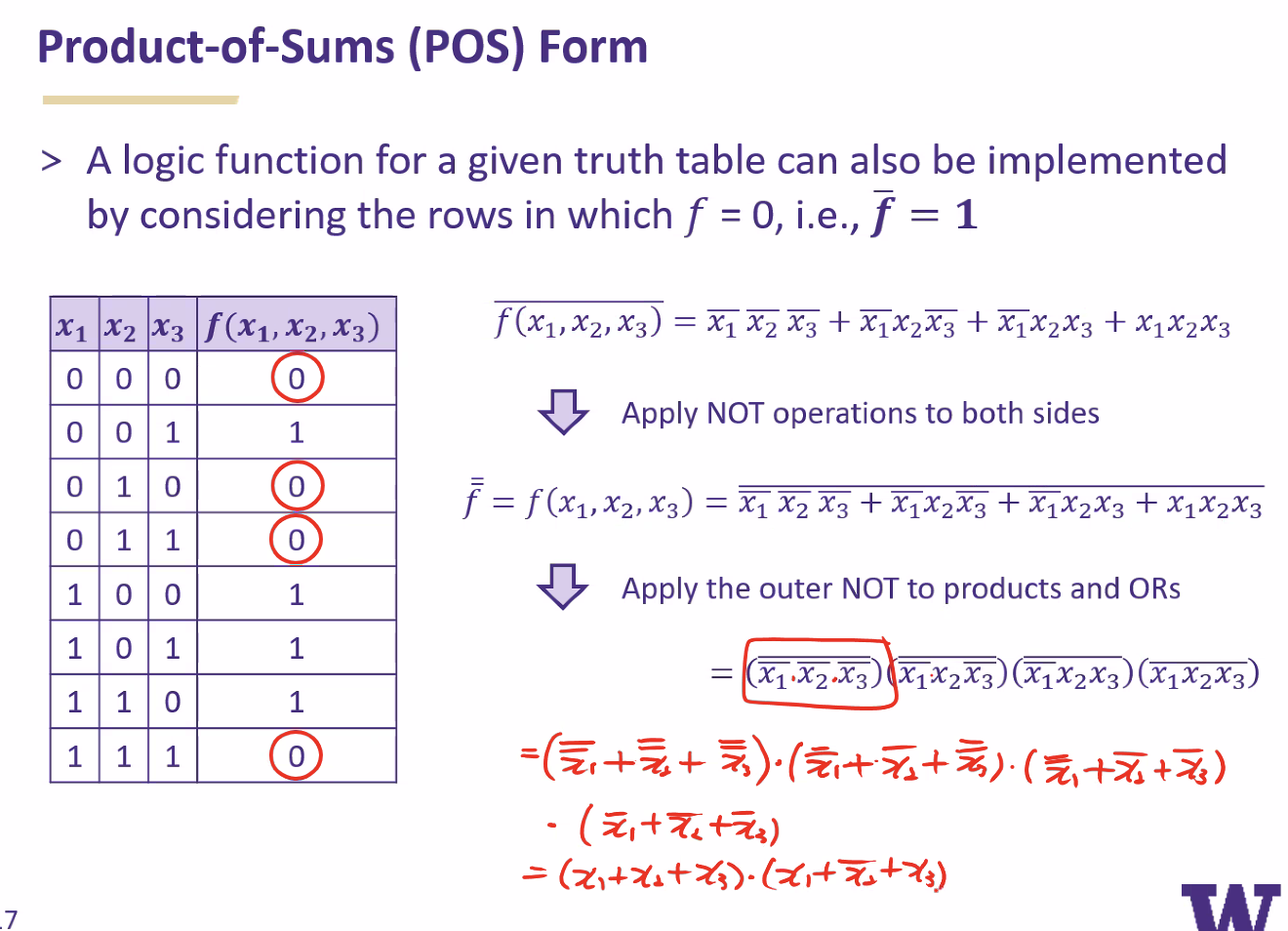

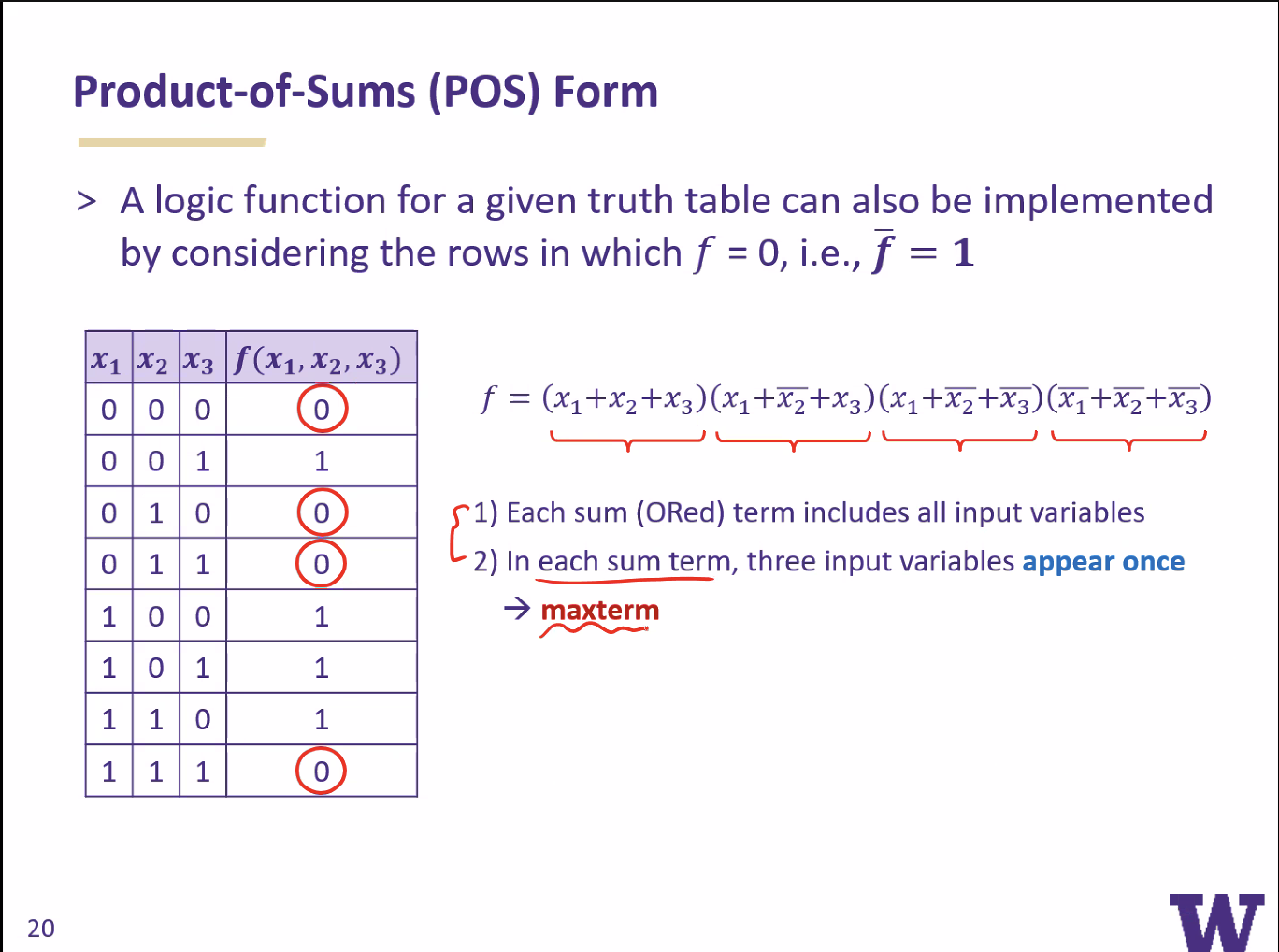

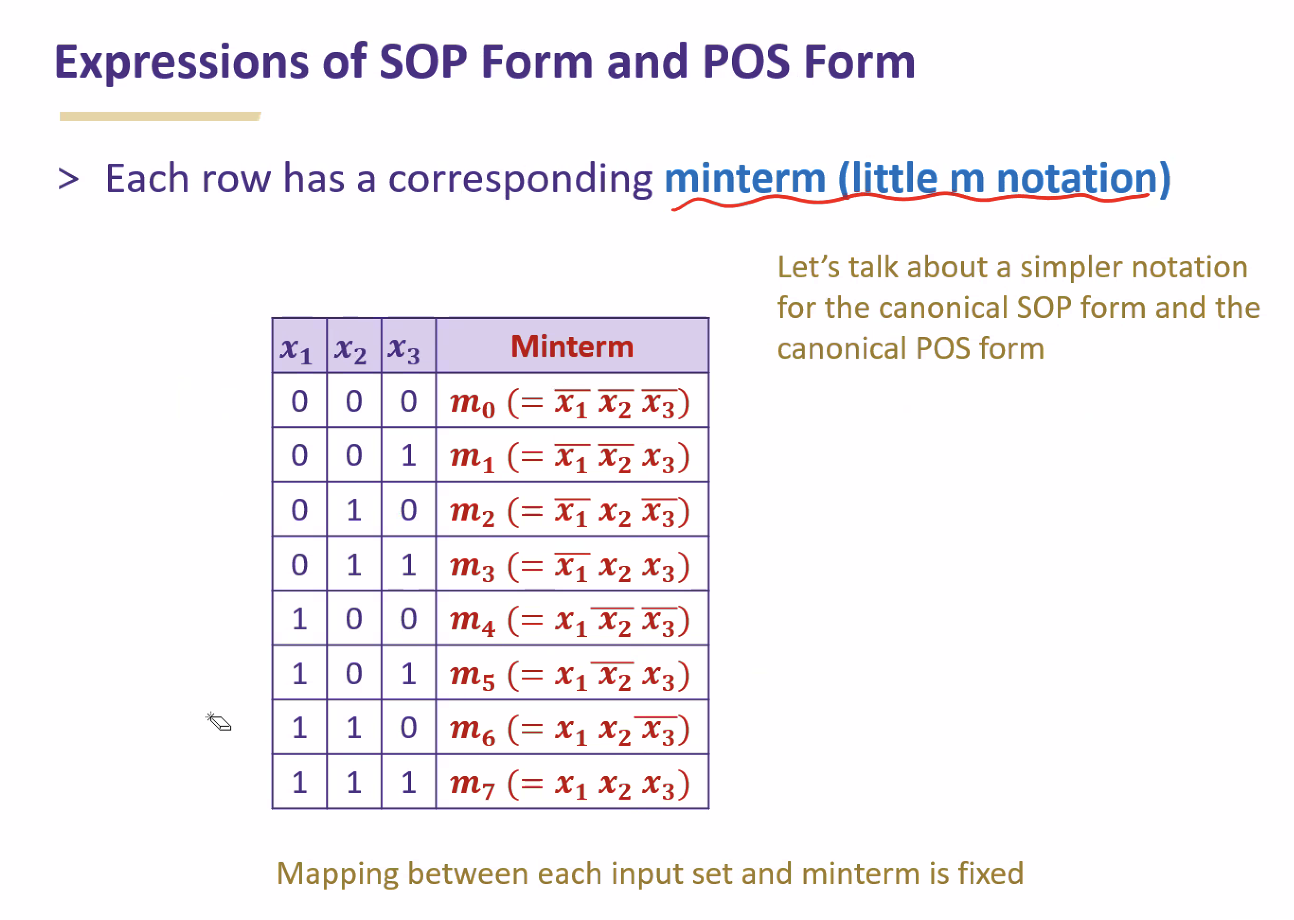

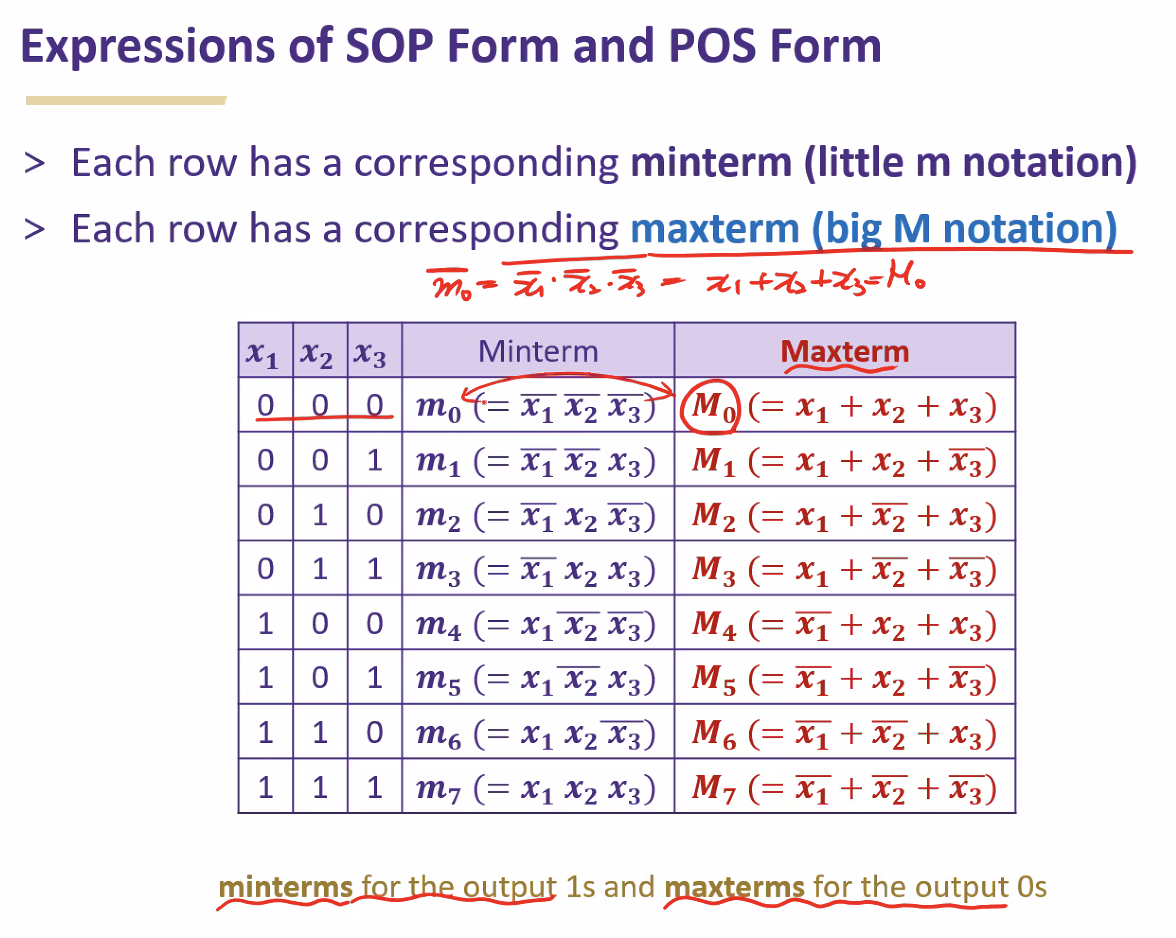

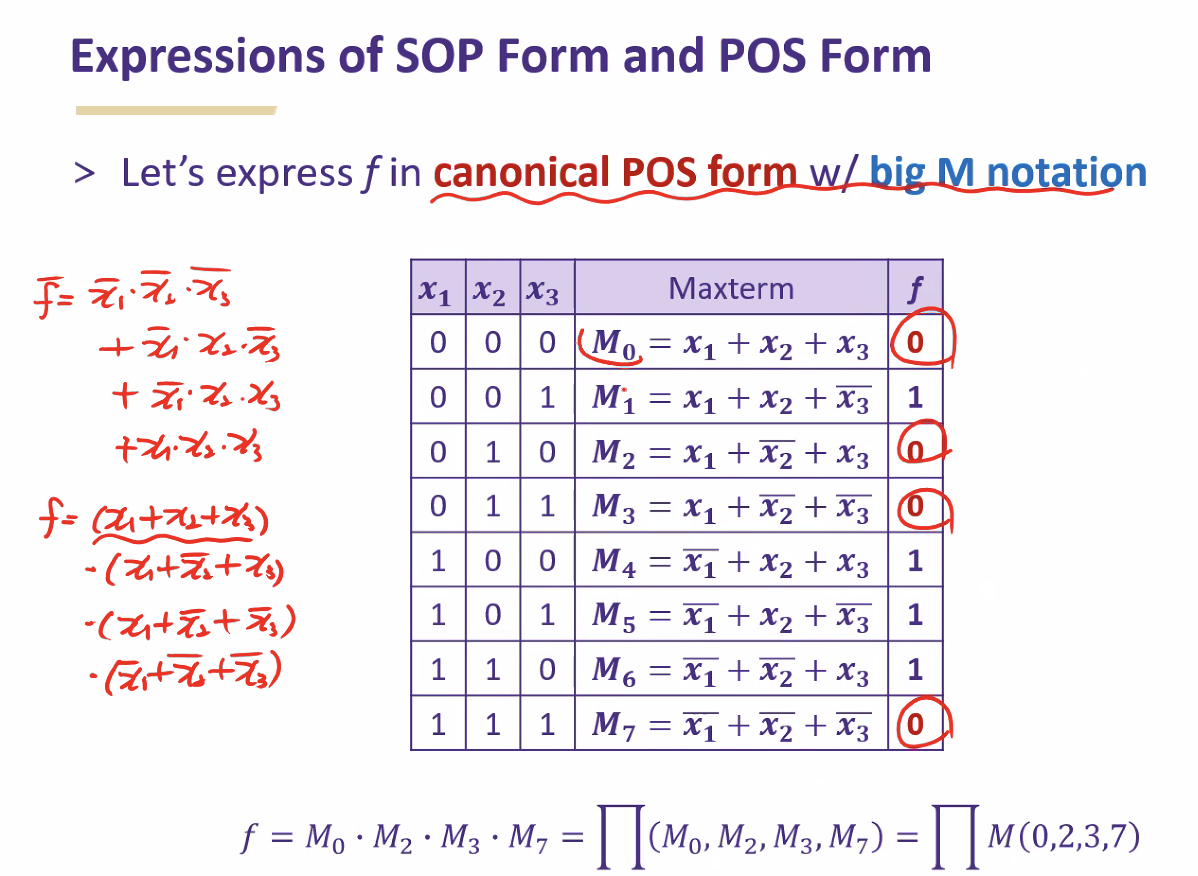

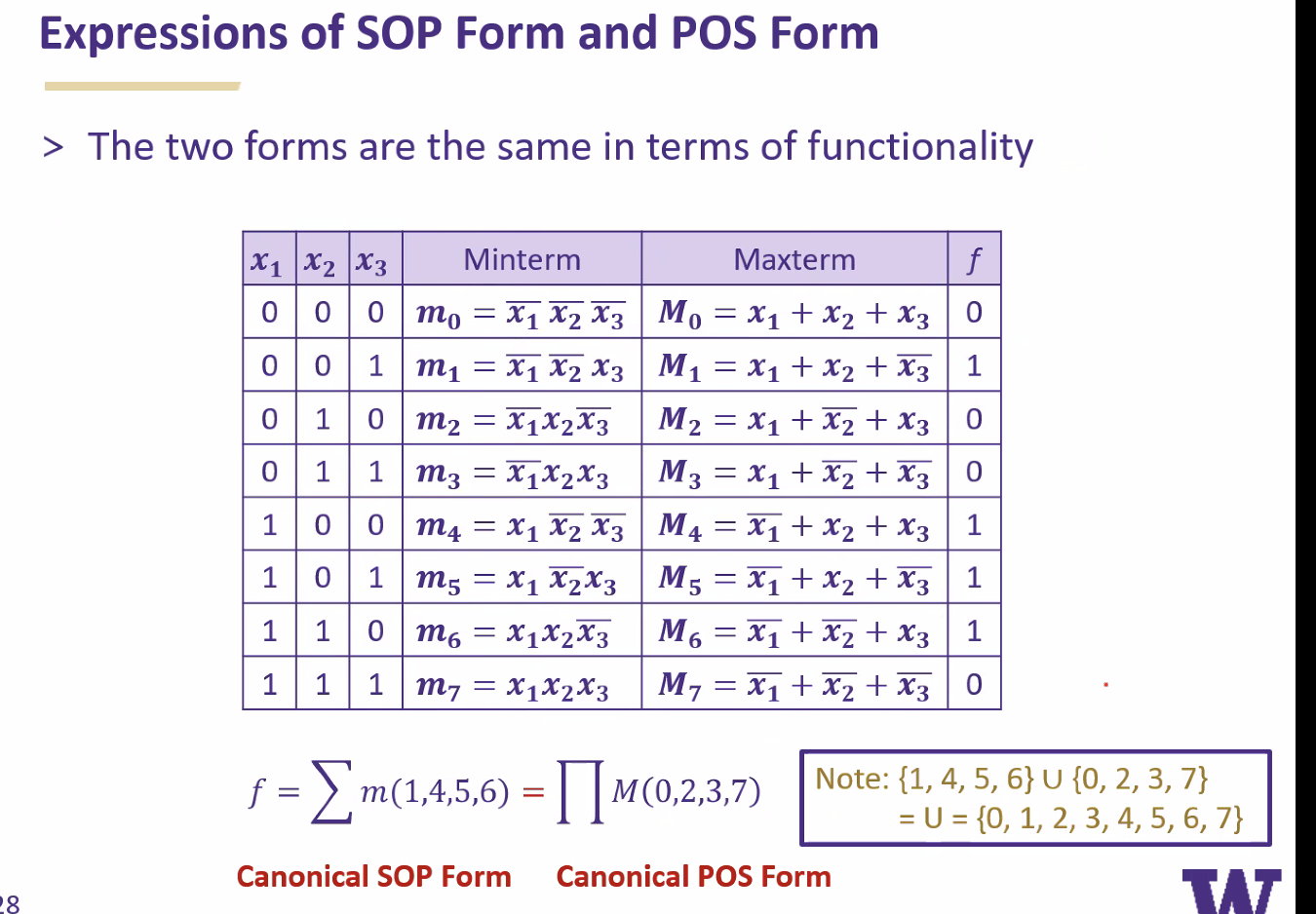

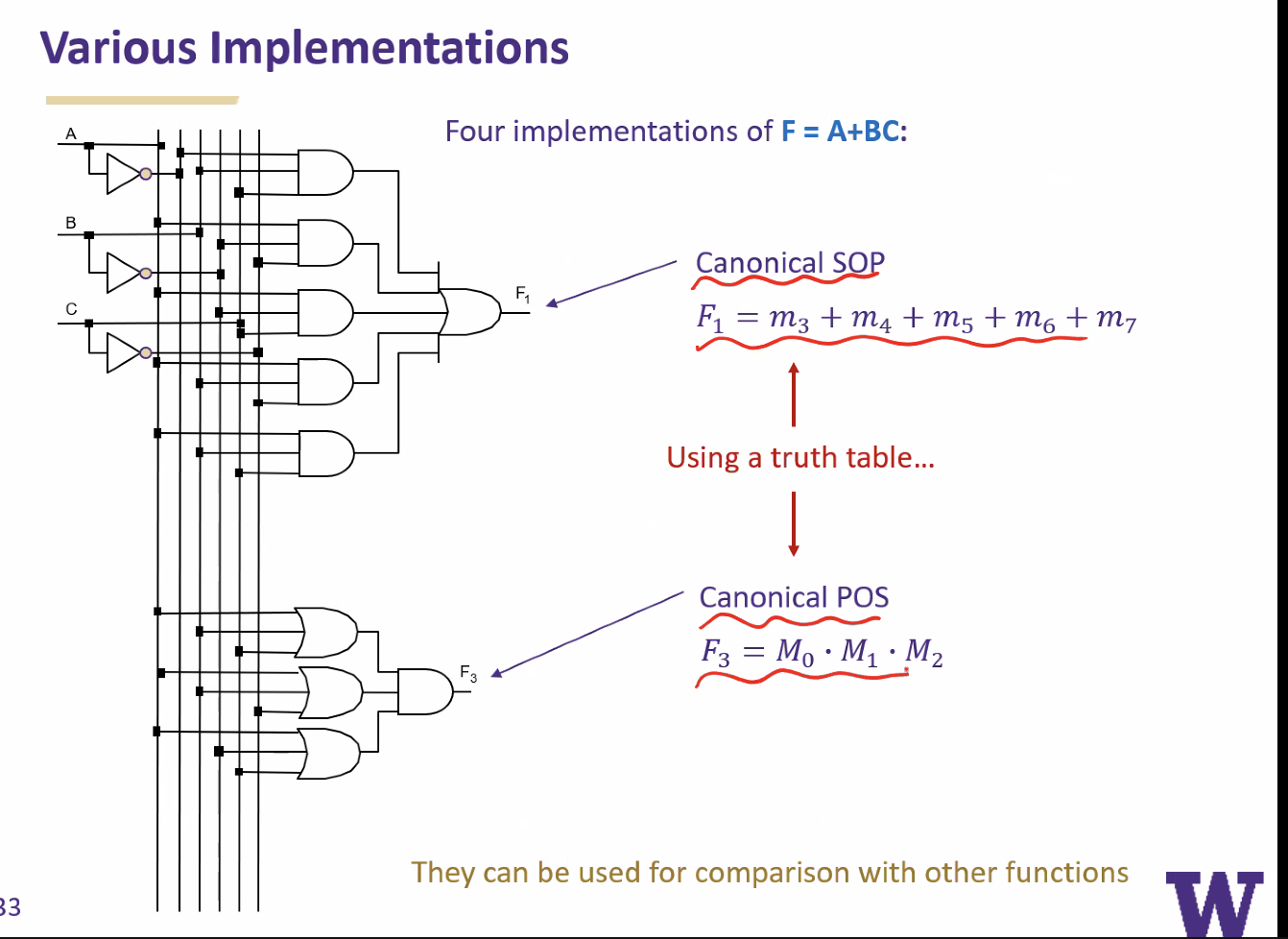

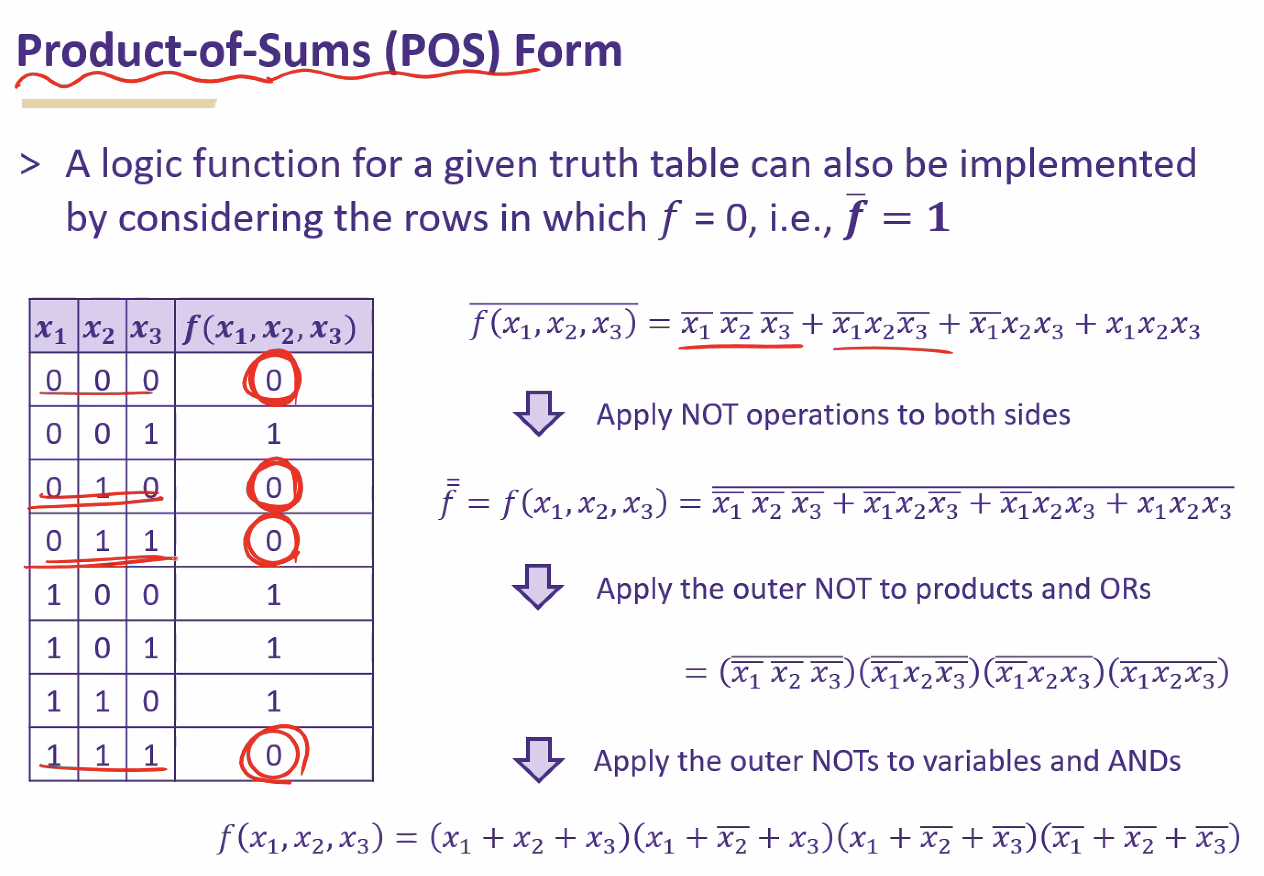

(4 maxterms)

Truth tables are always in the same order, think binary numbers

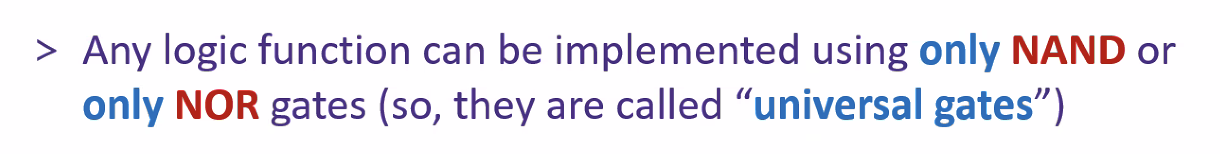

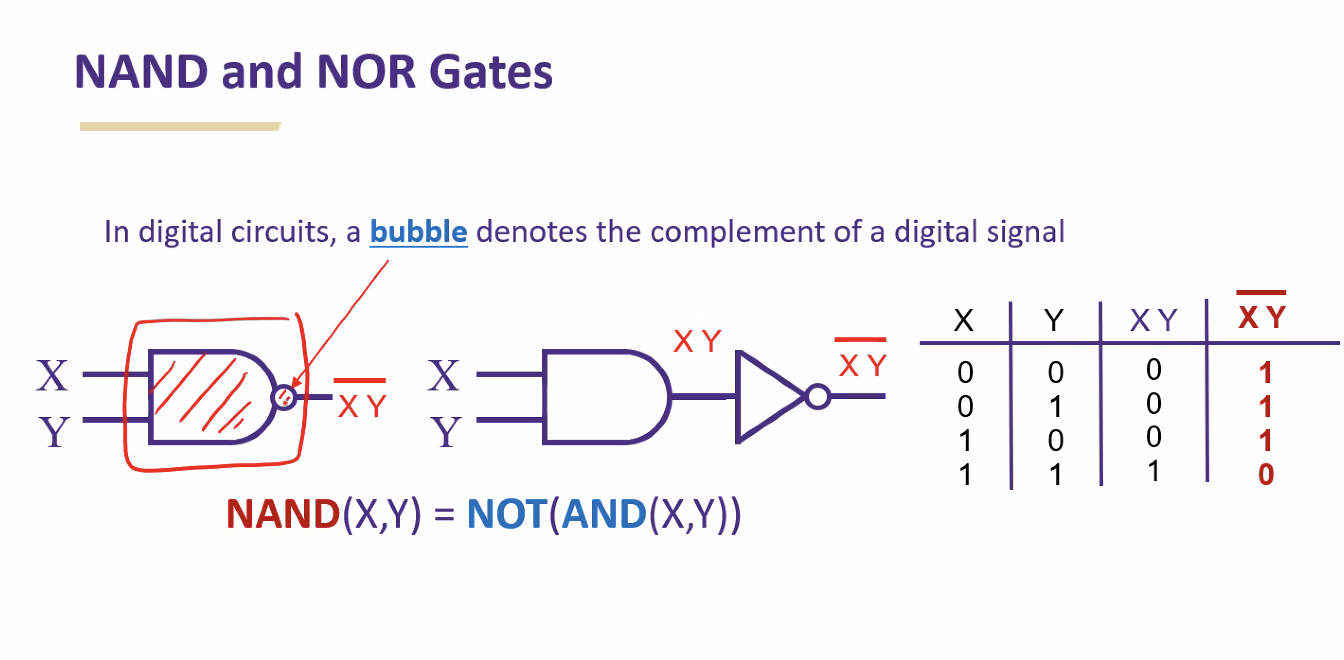

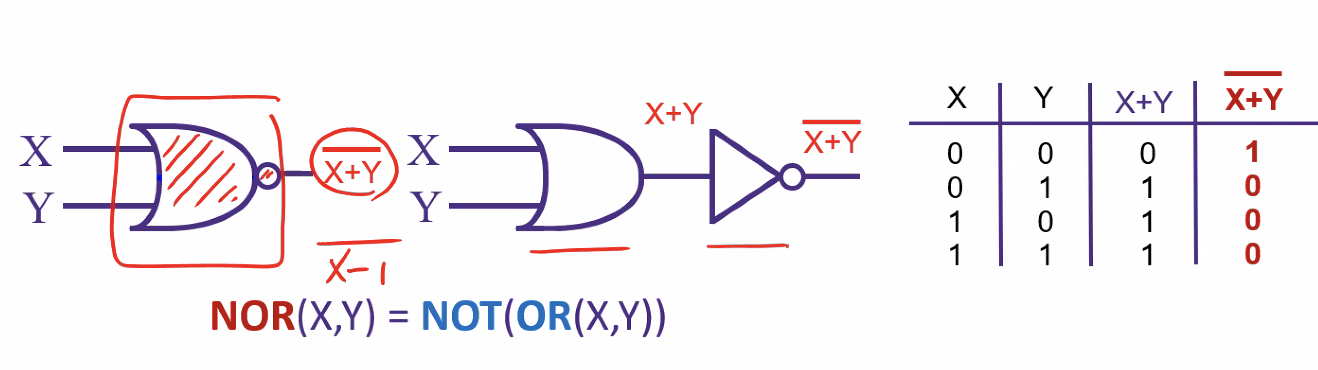

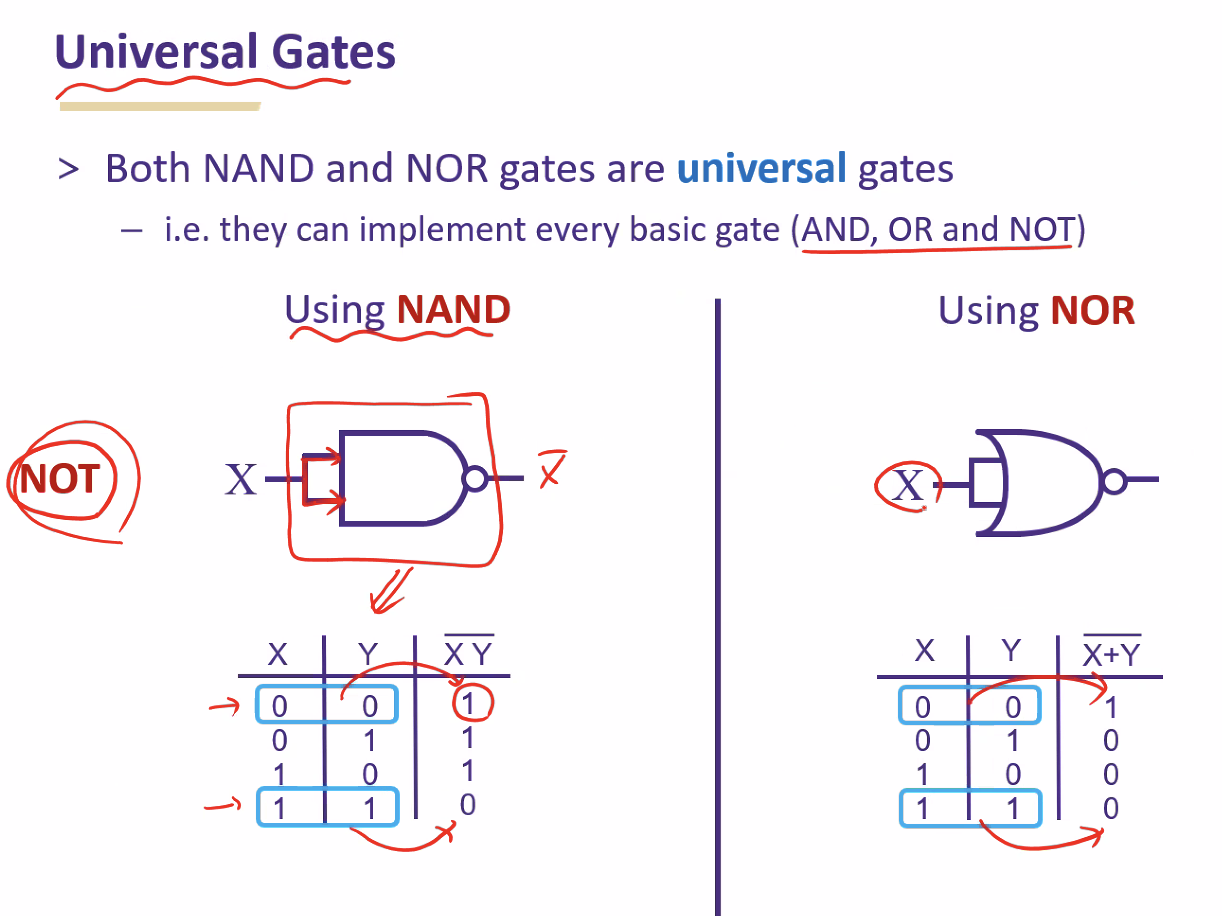

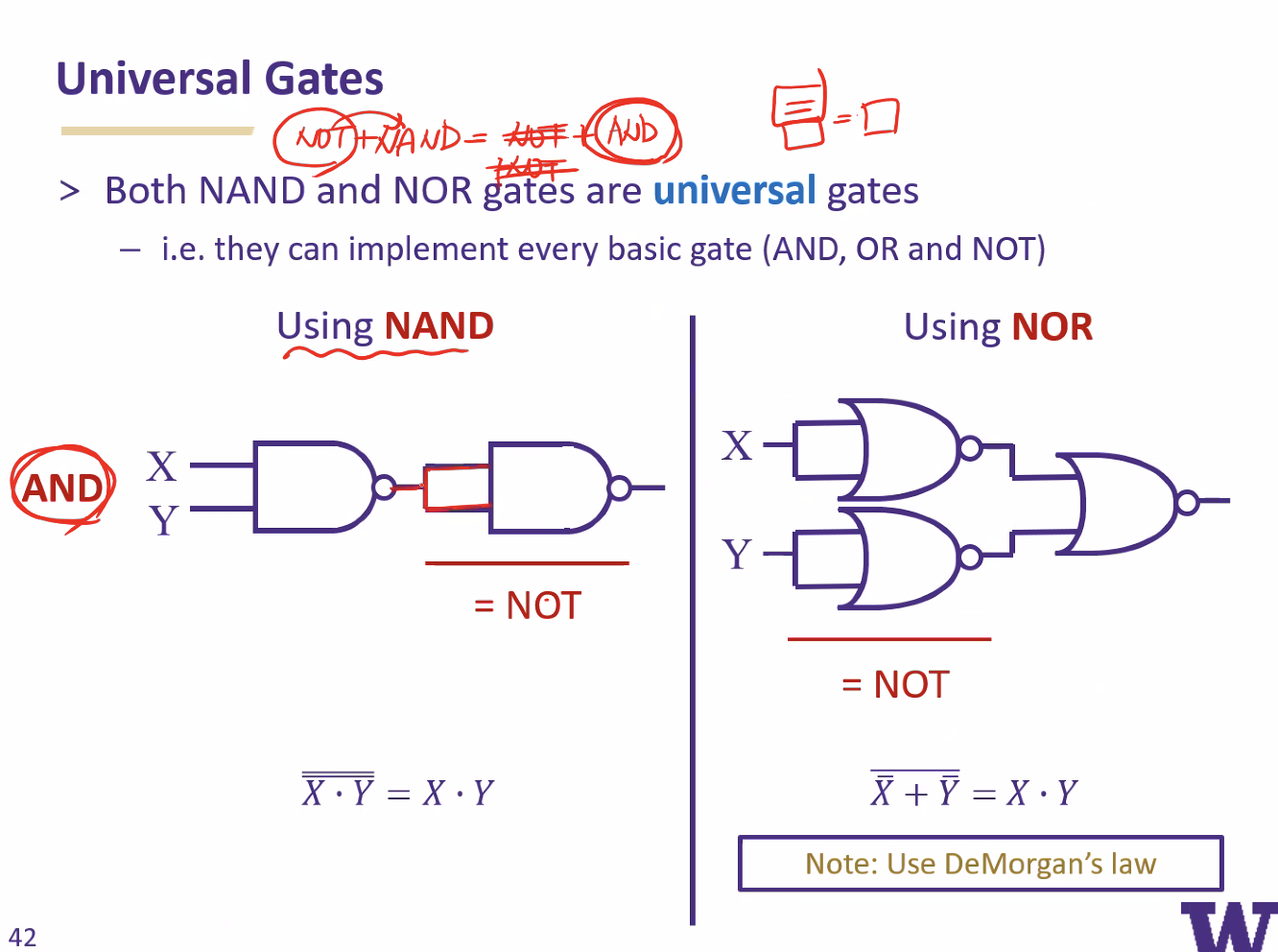

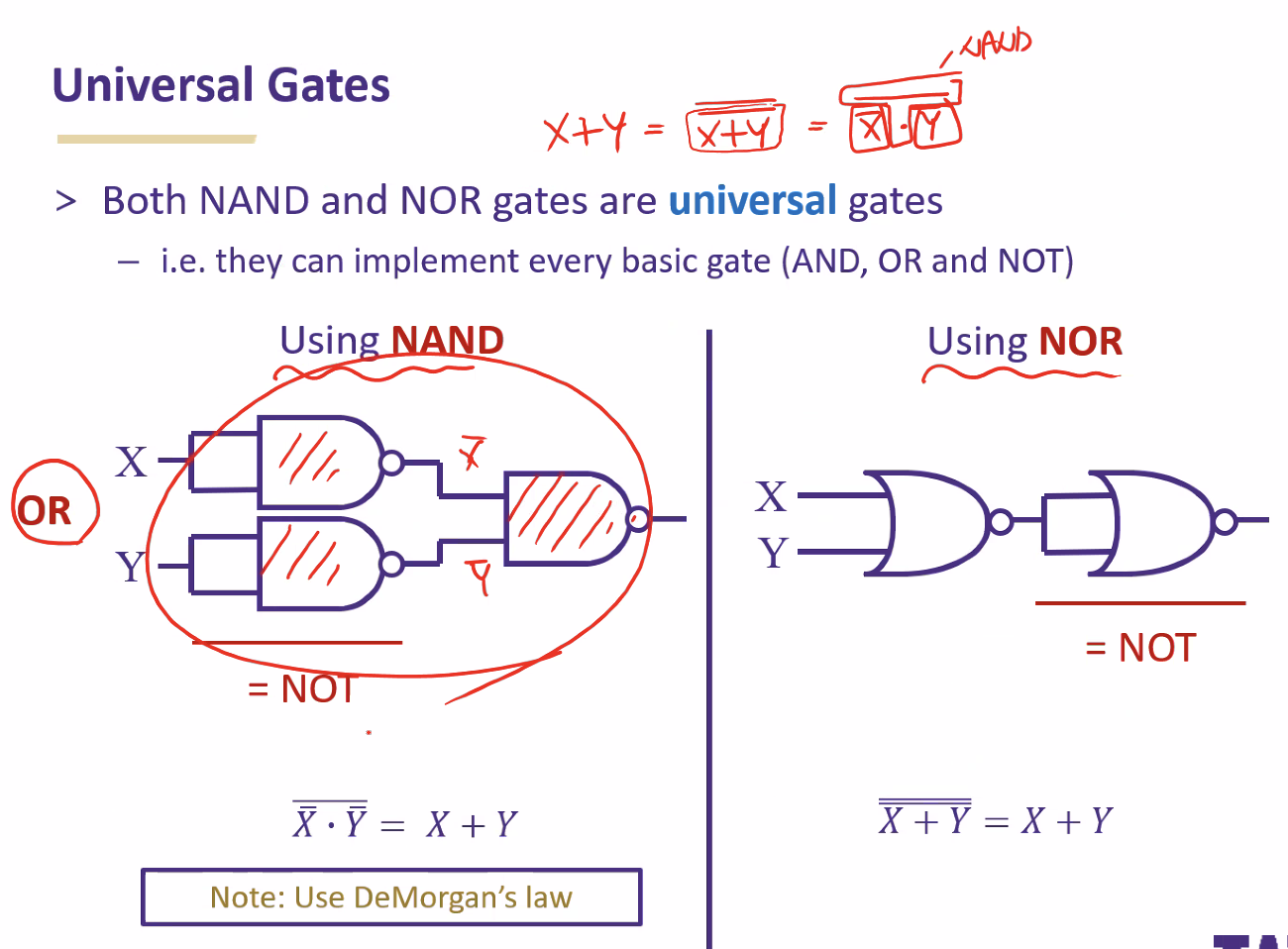

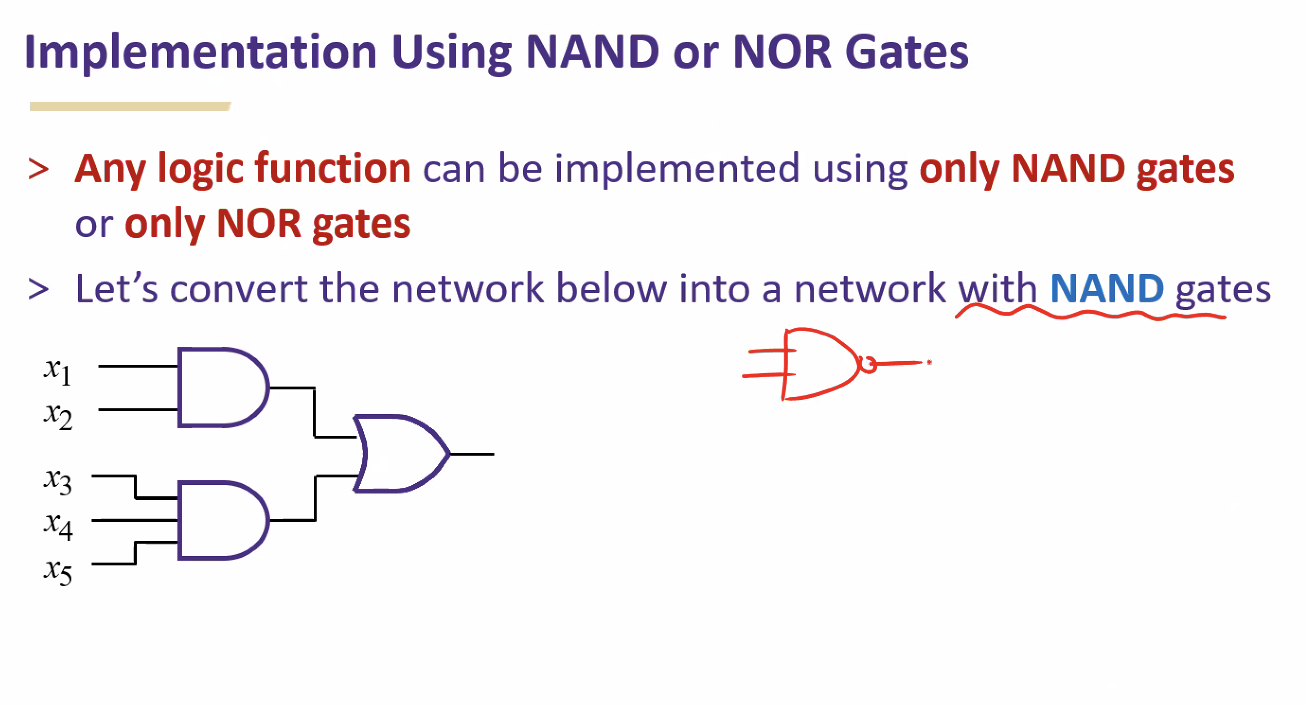

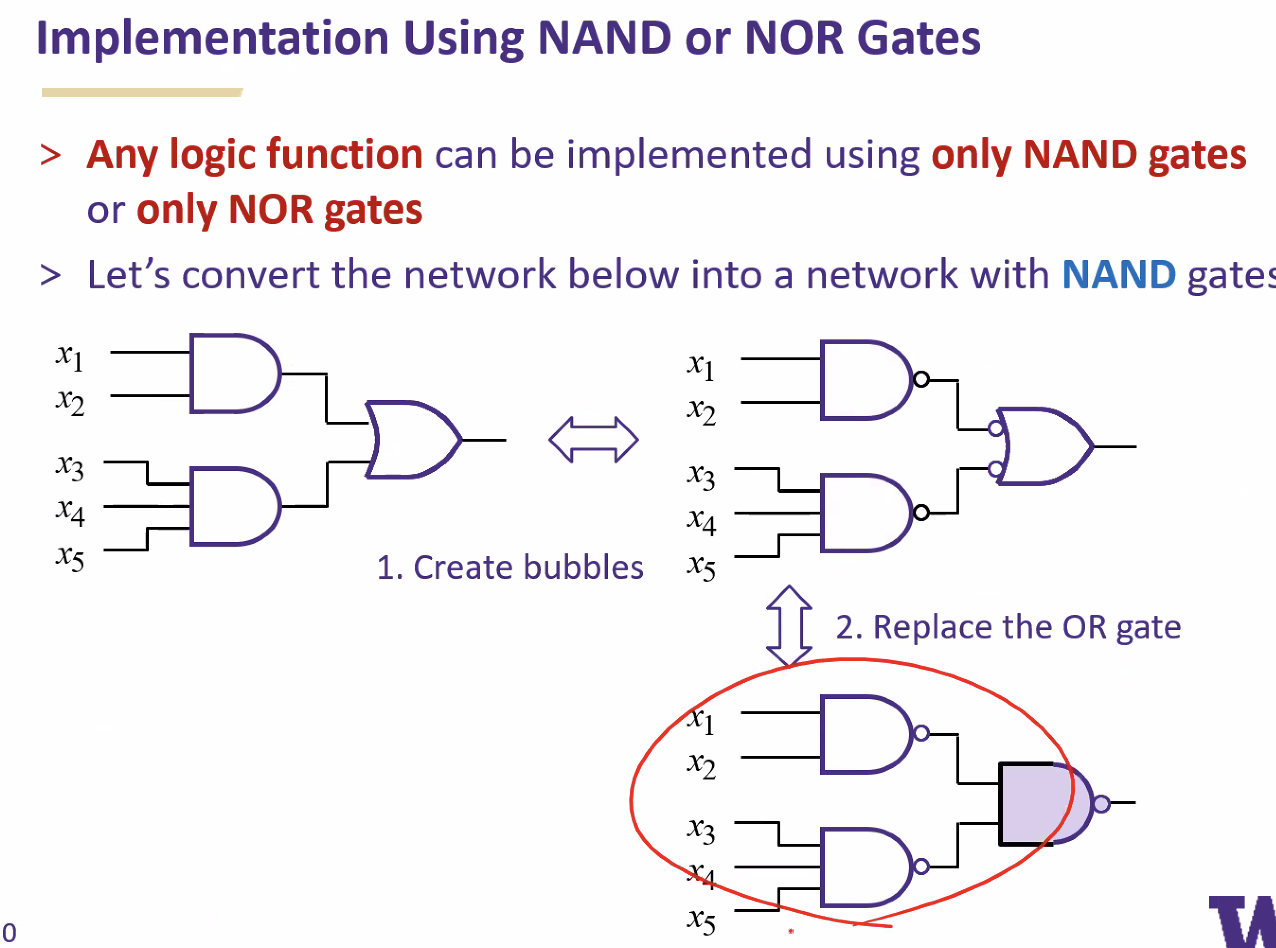

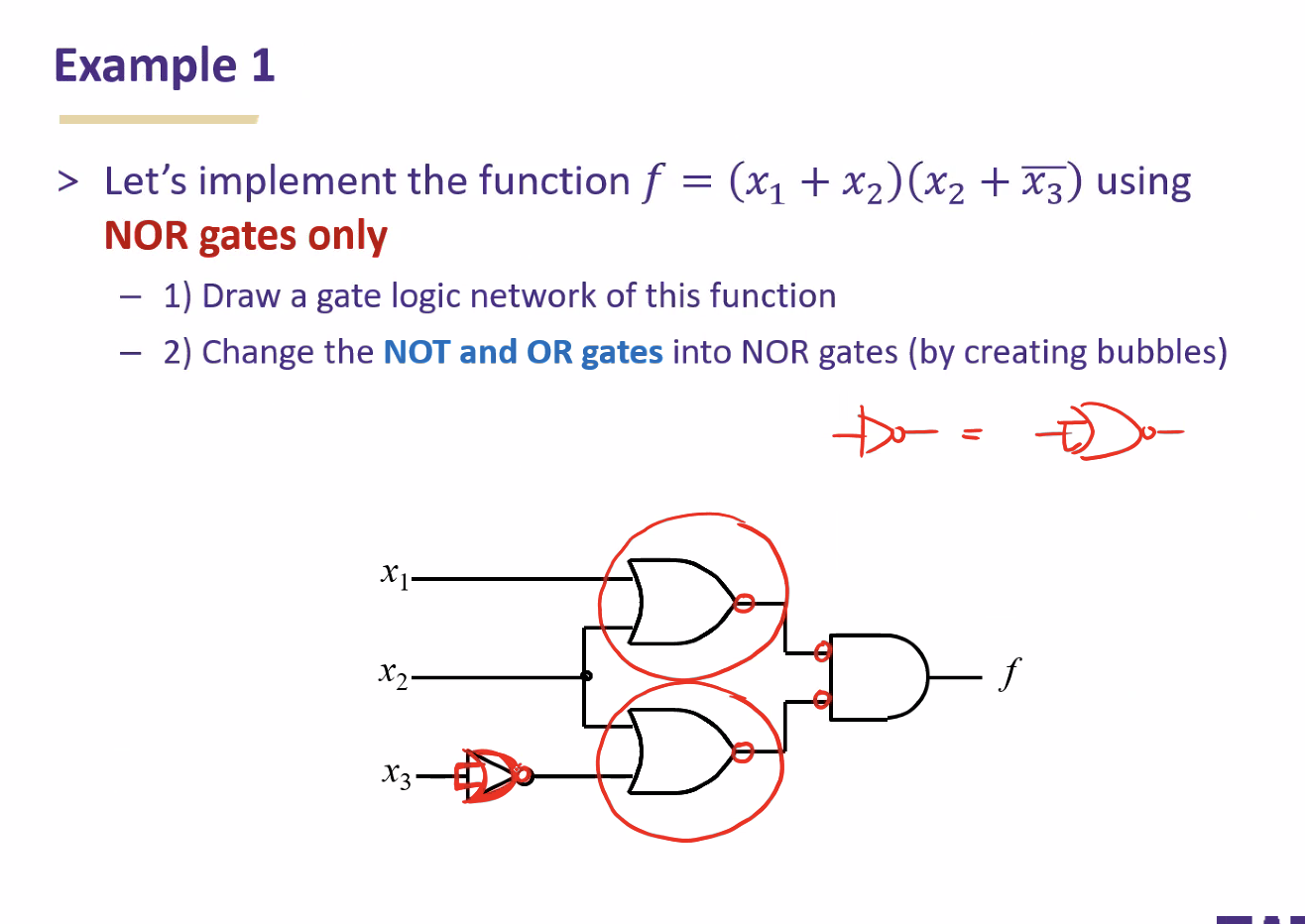

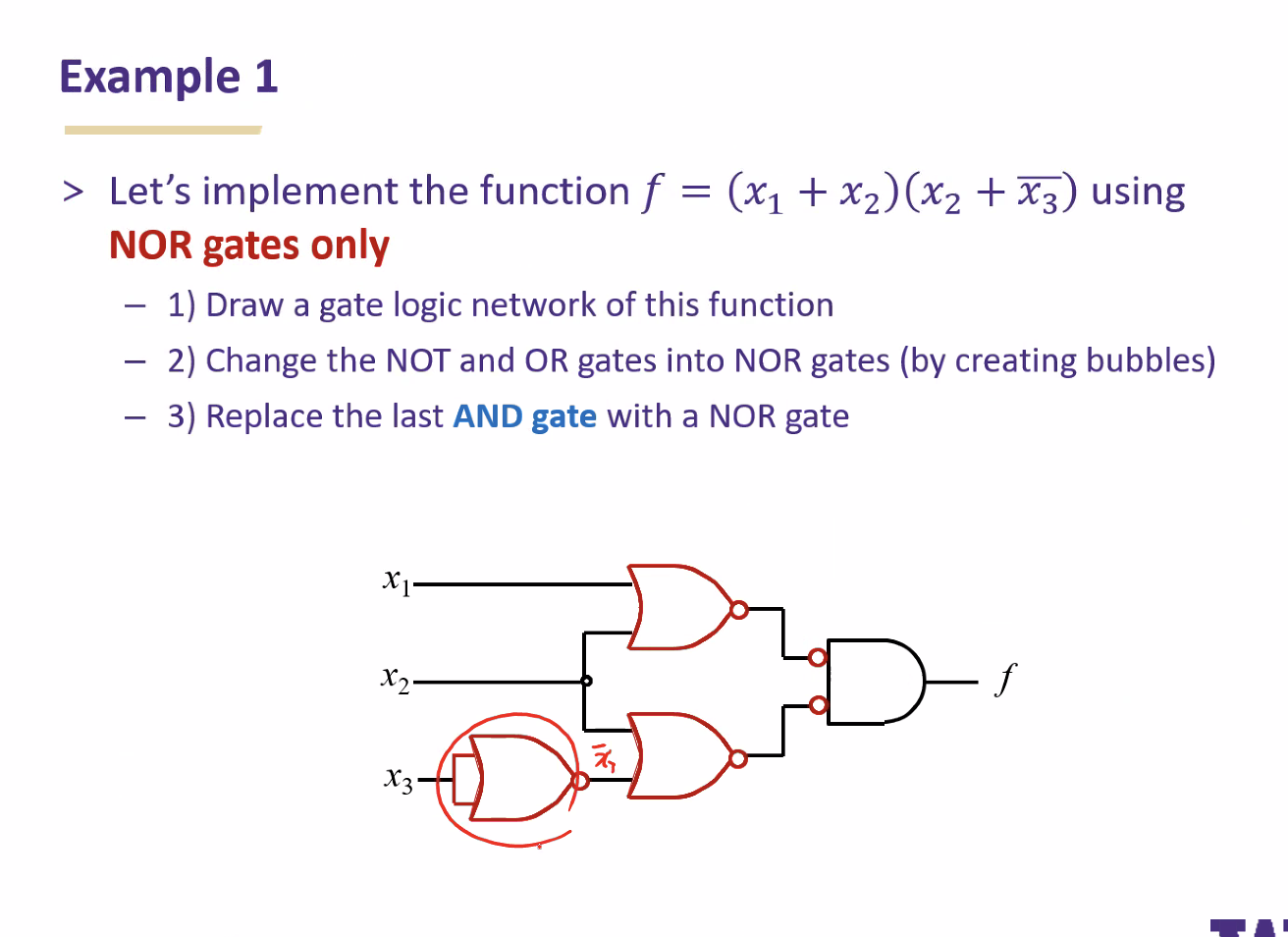

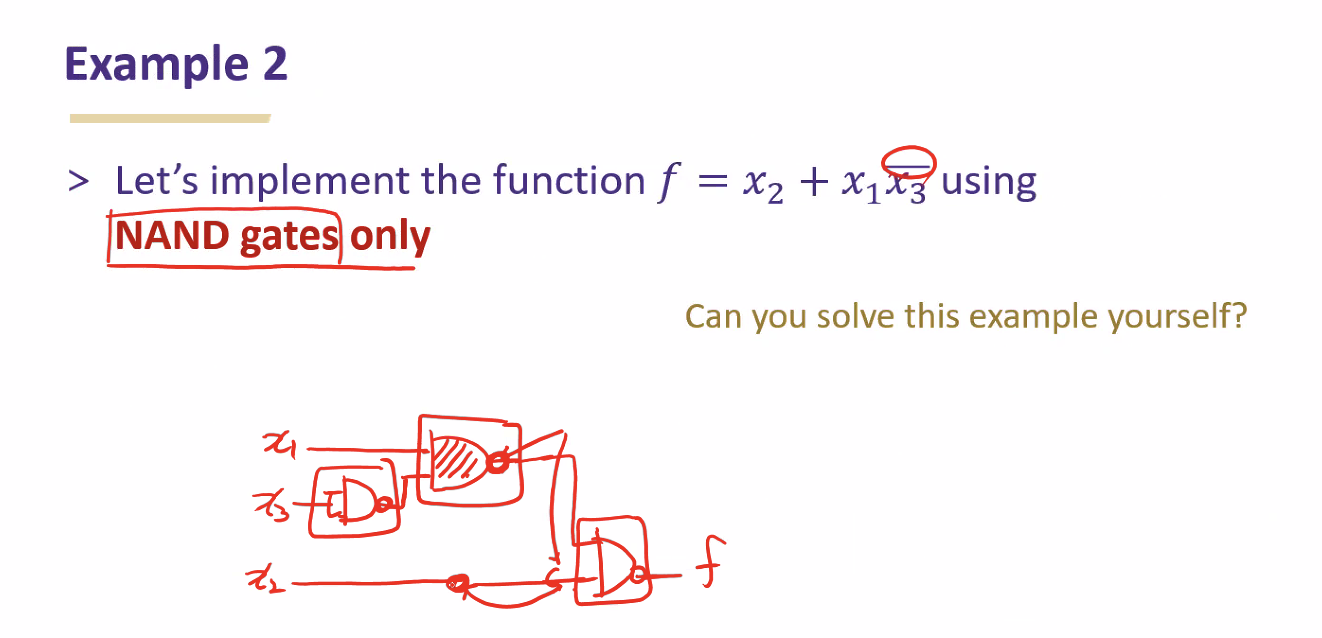

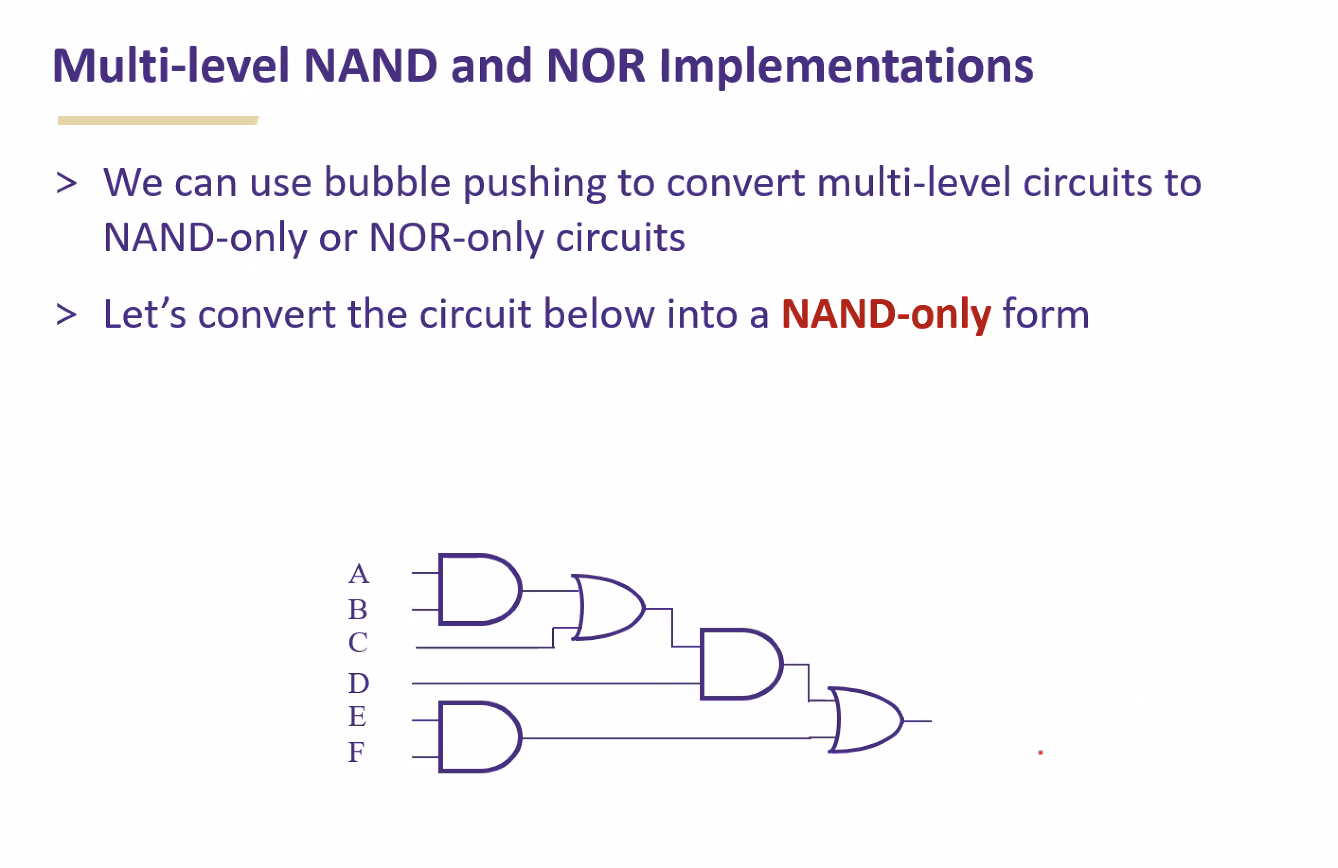

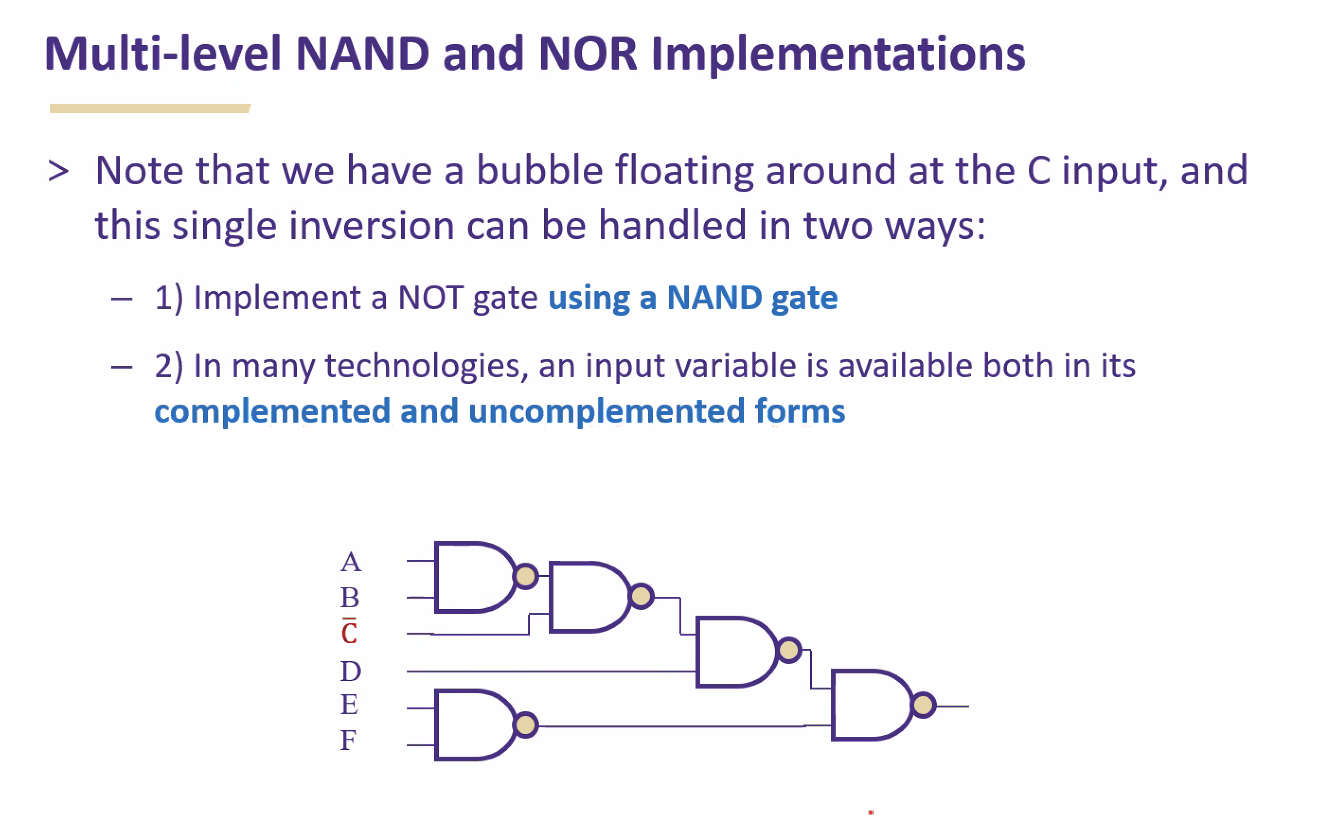

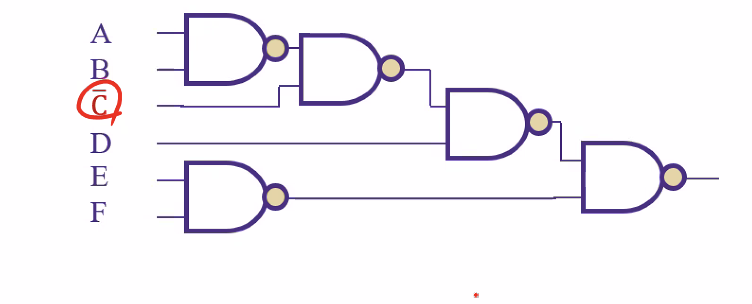

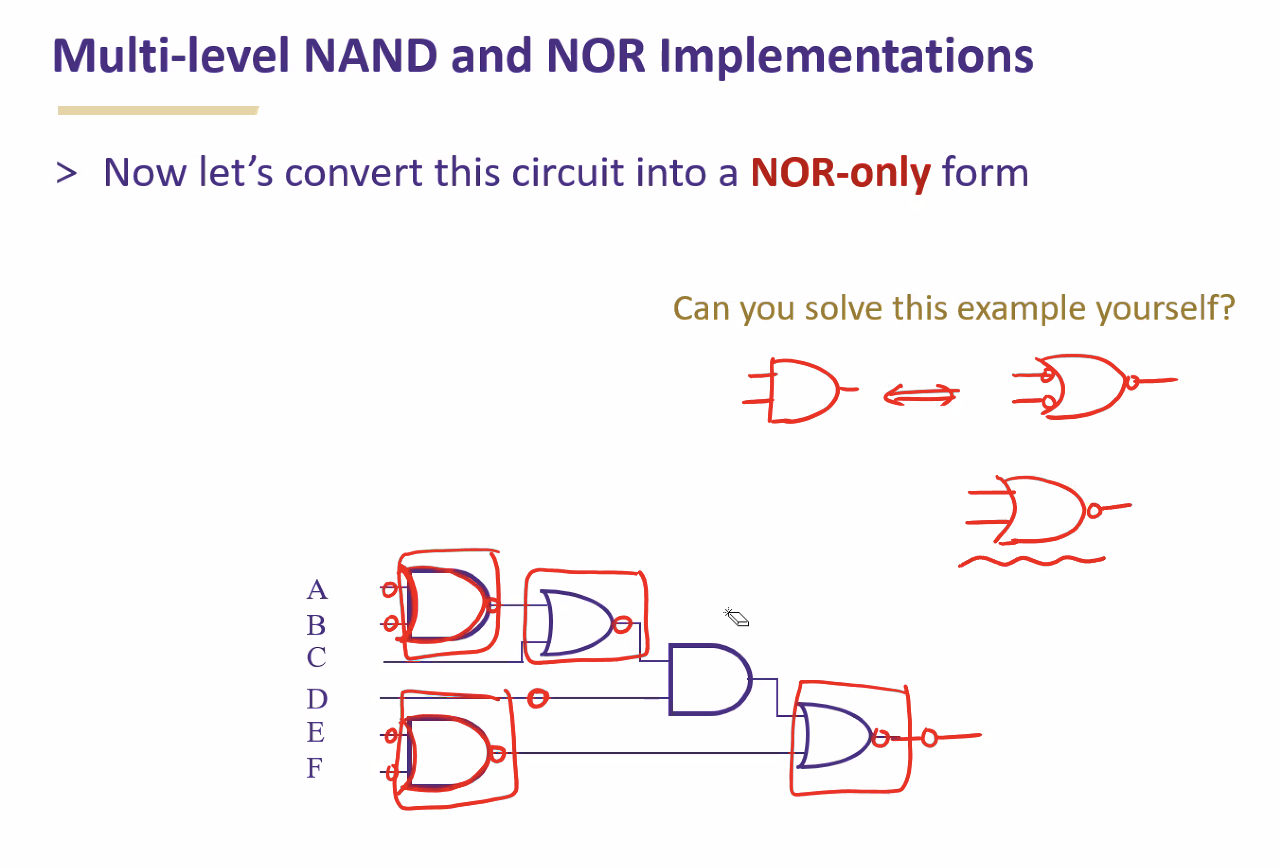

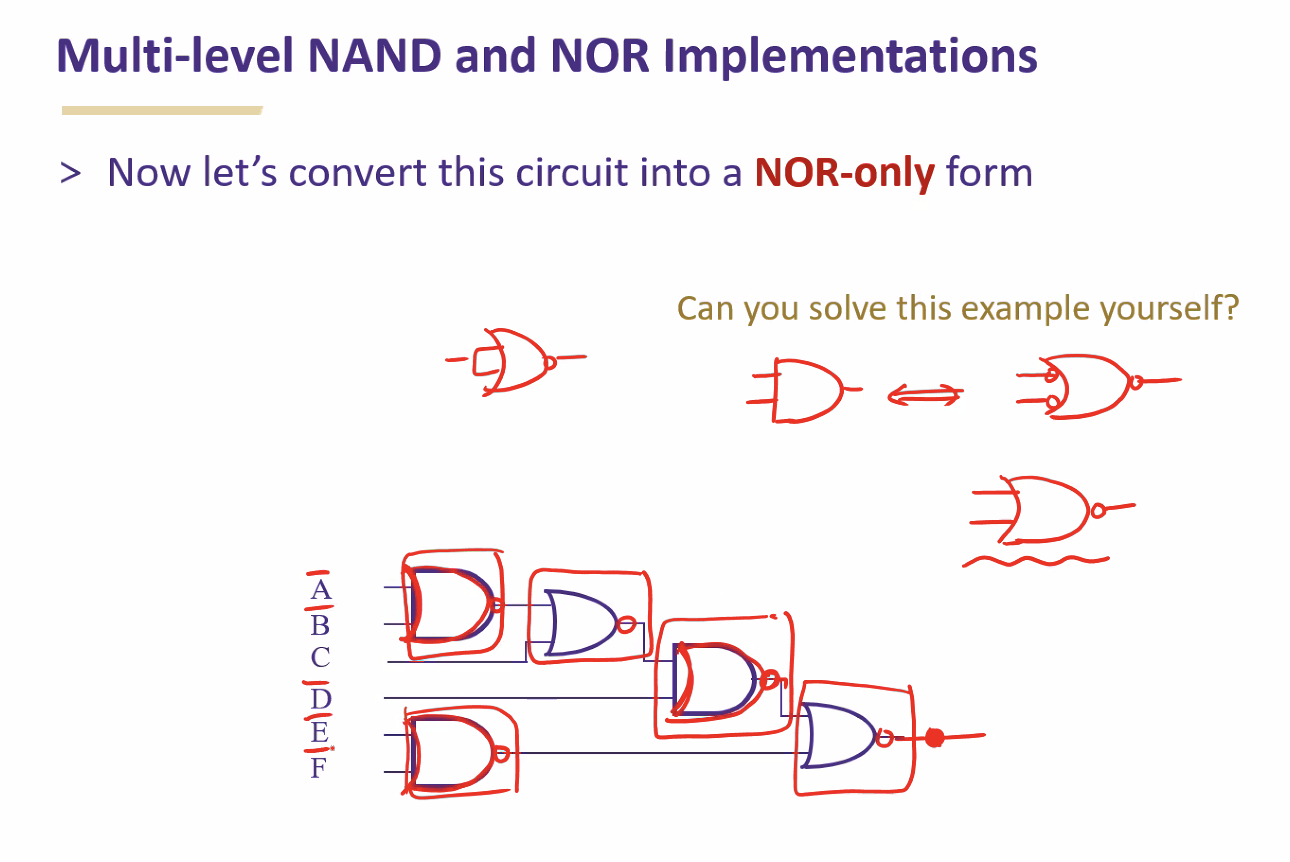

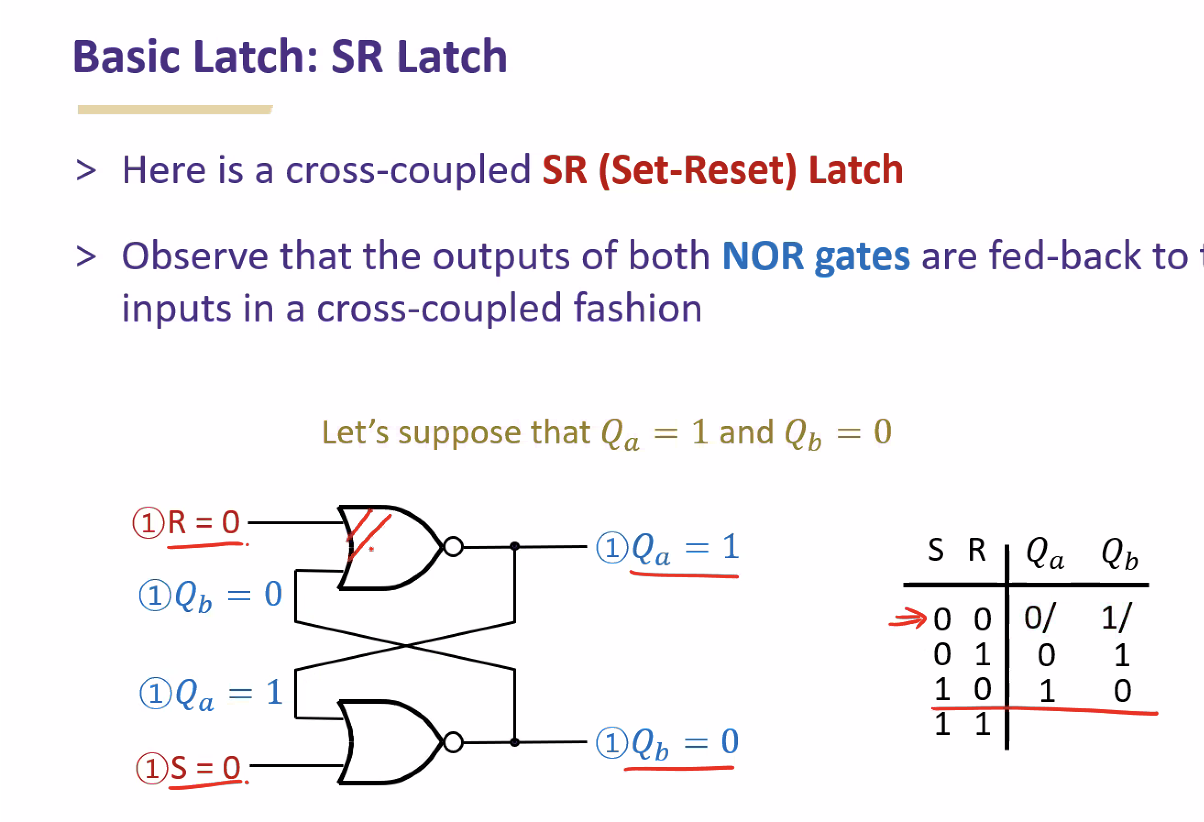

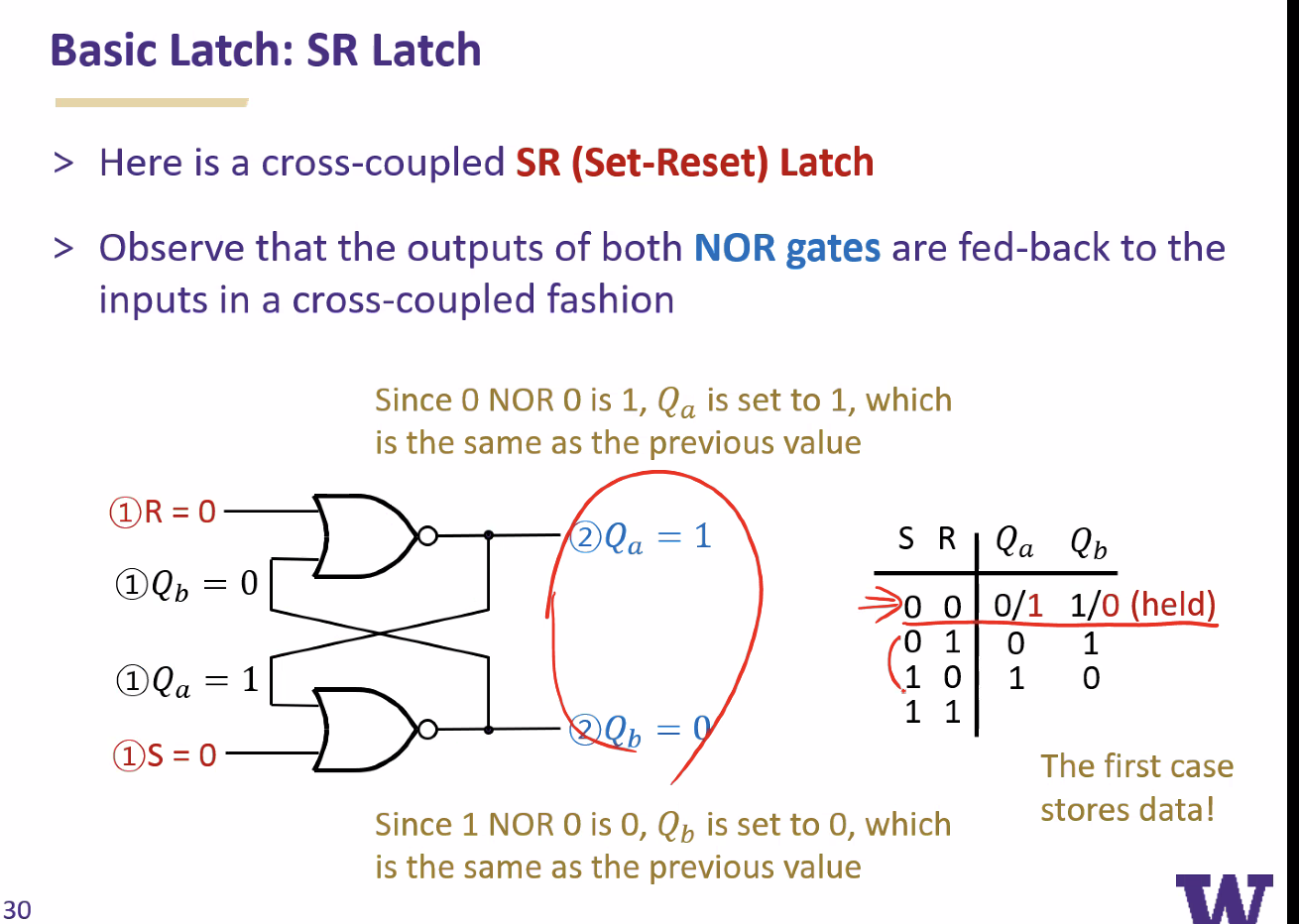

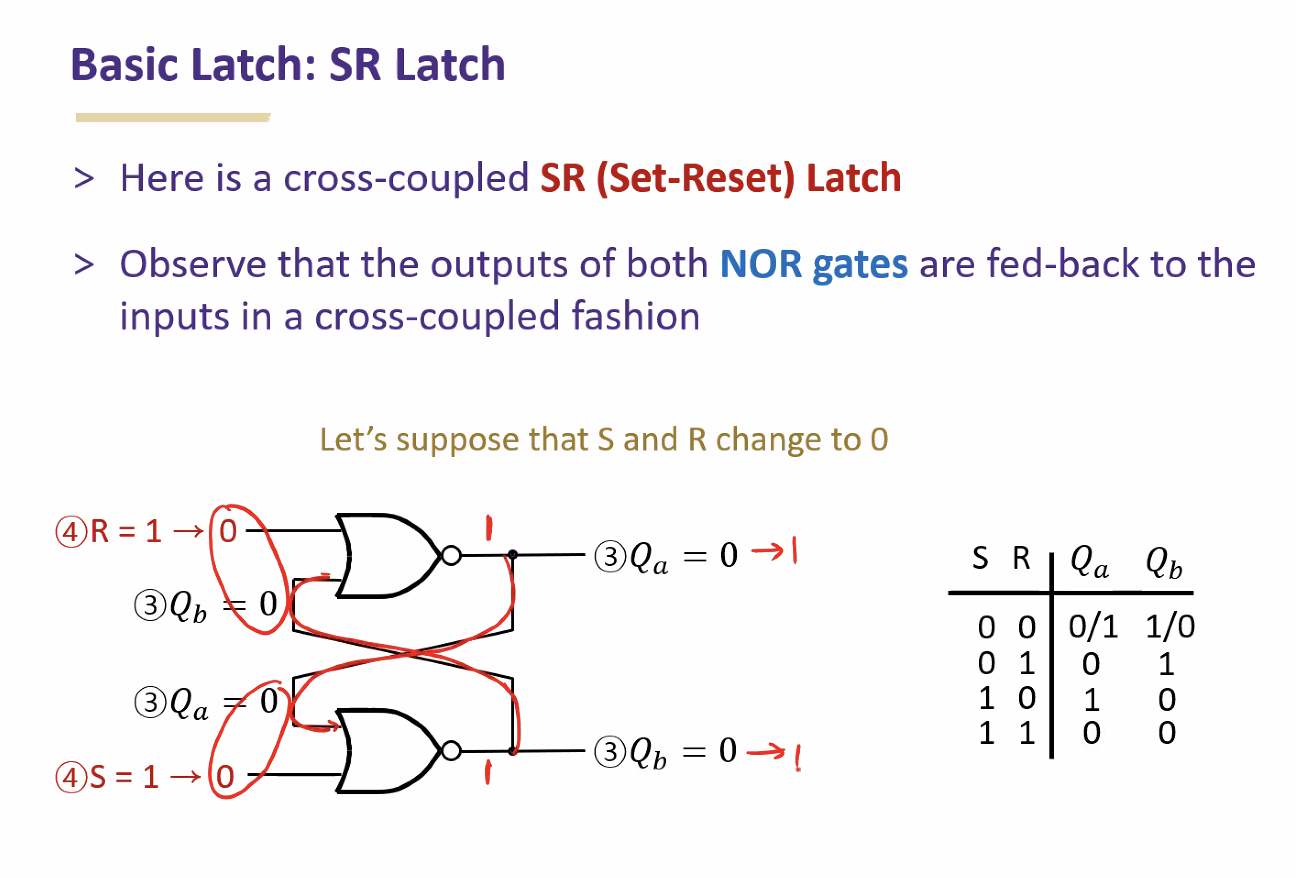

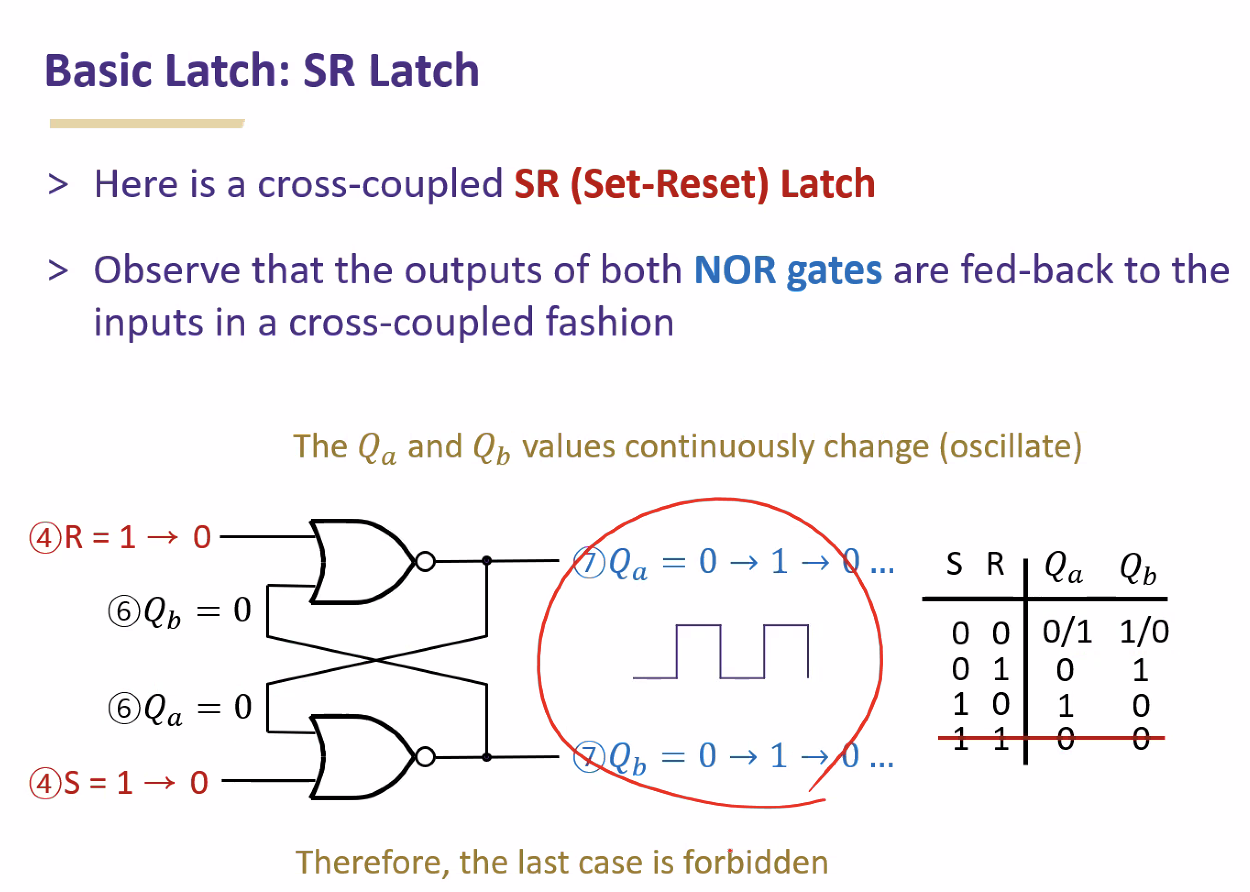

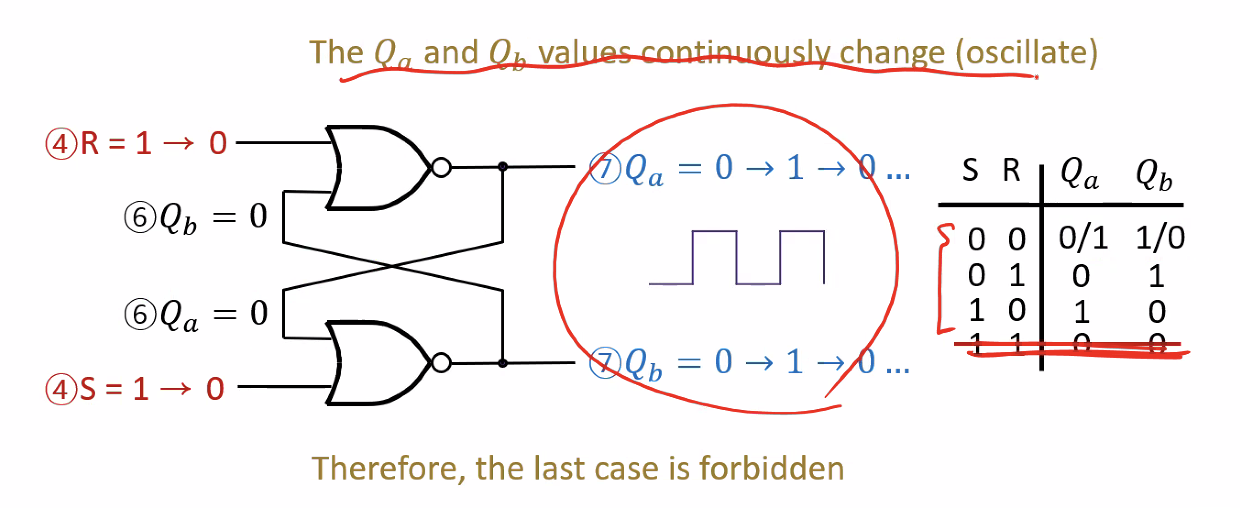

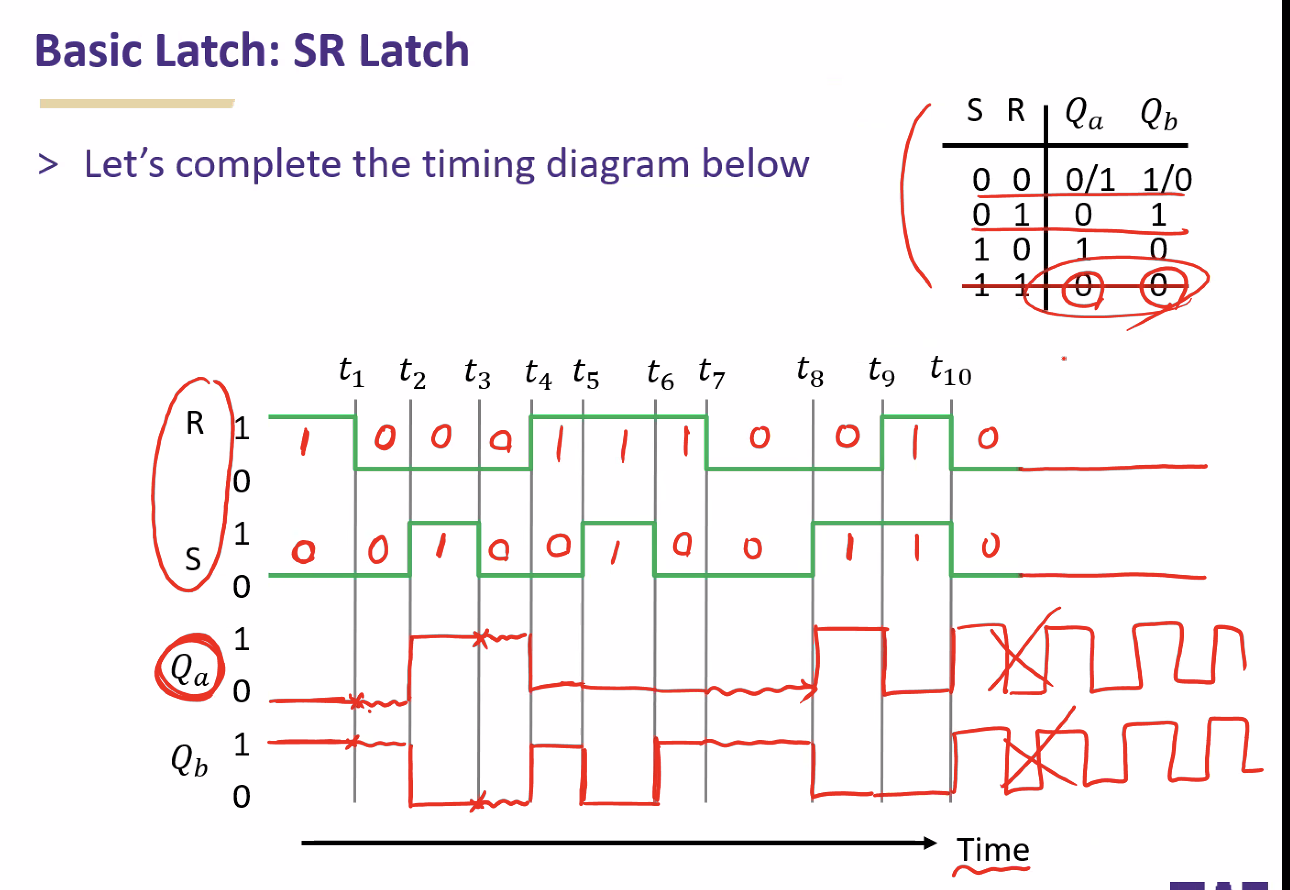

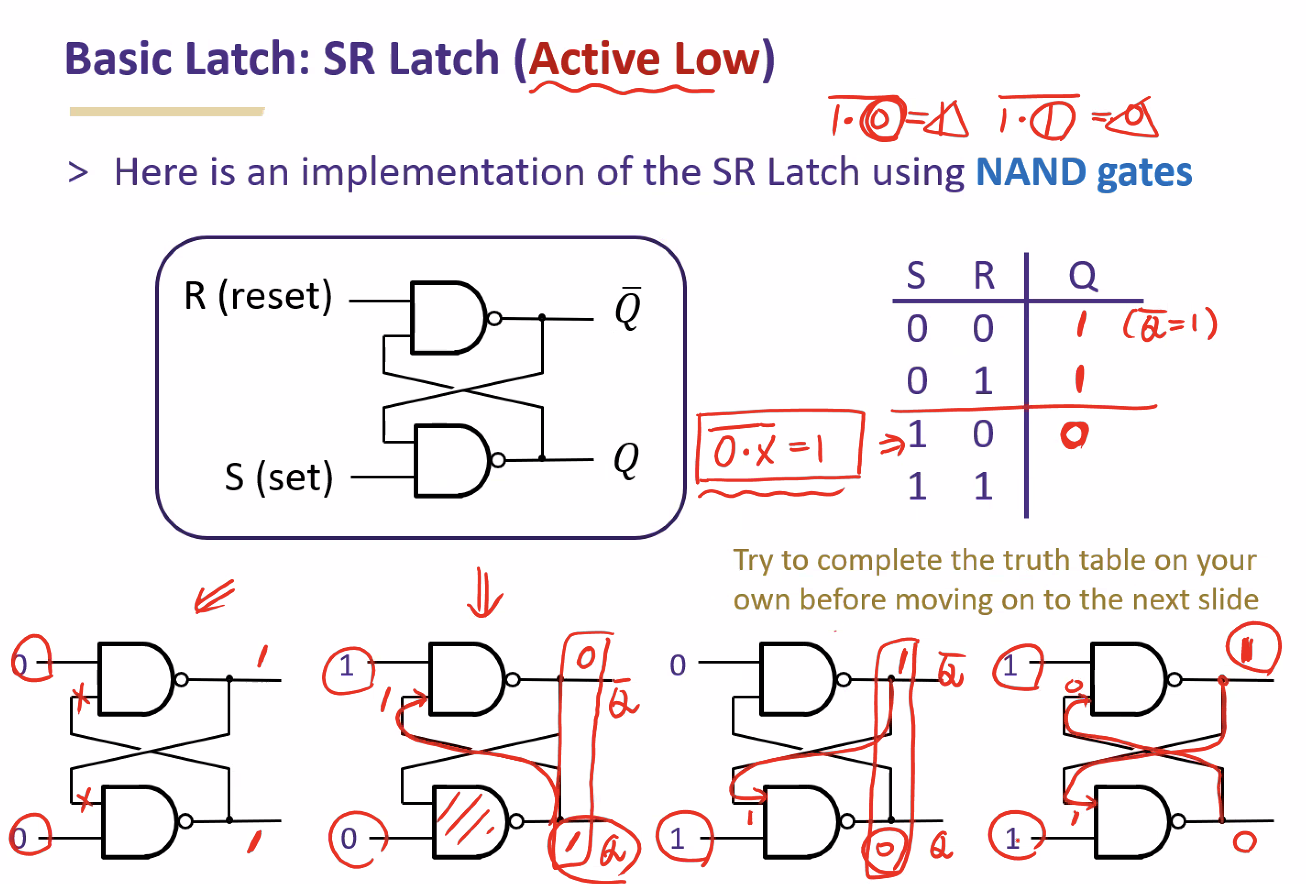

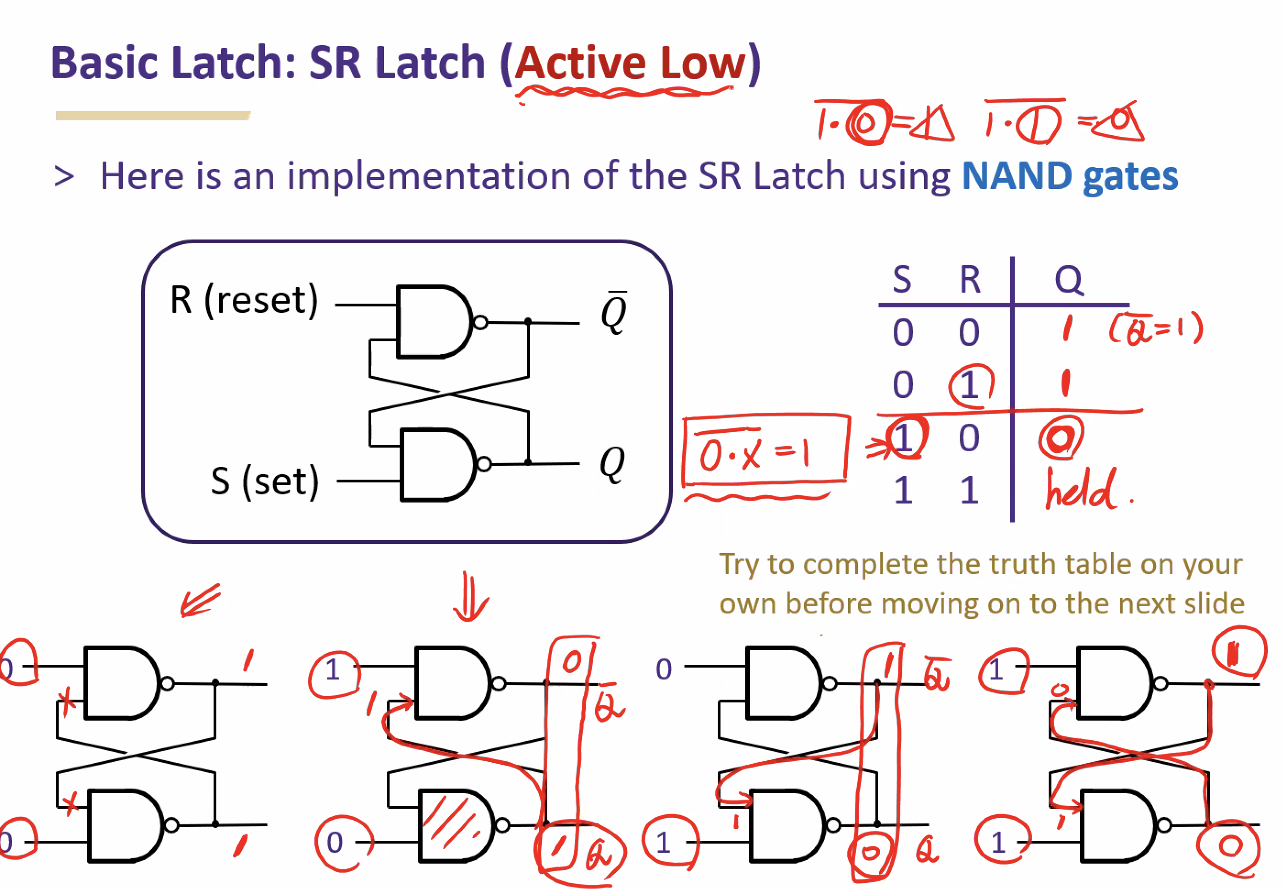

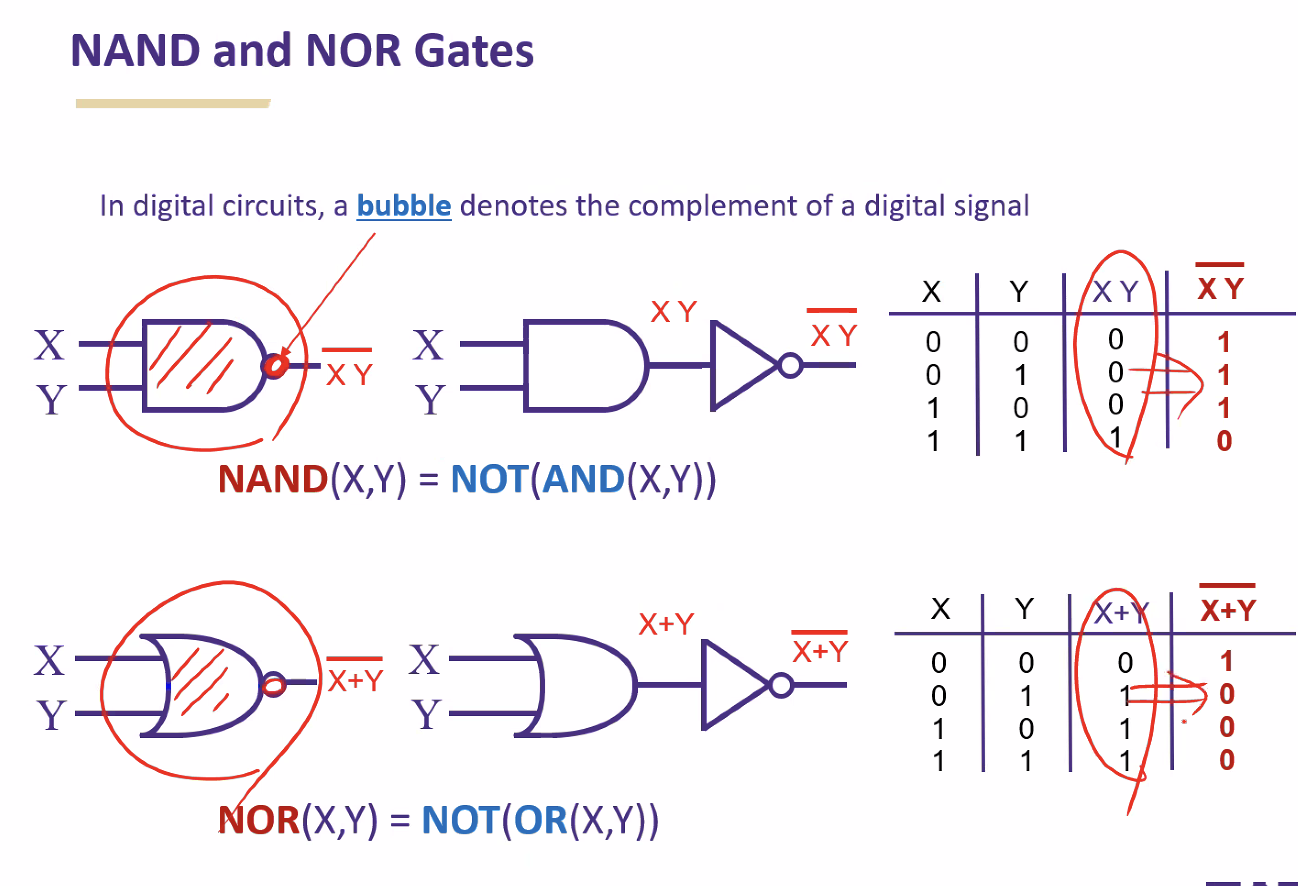

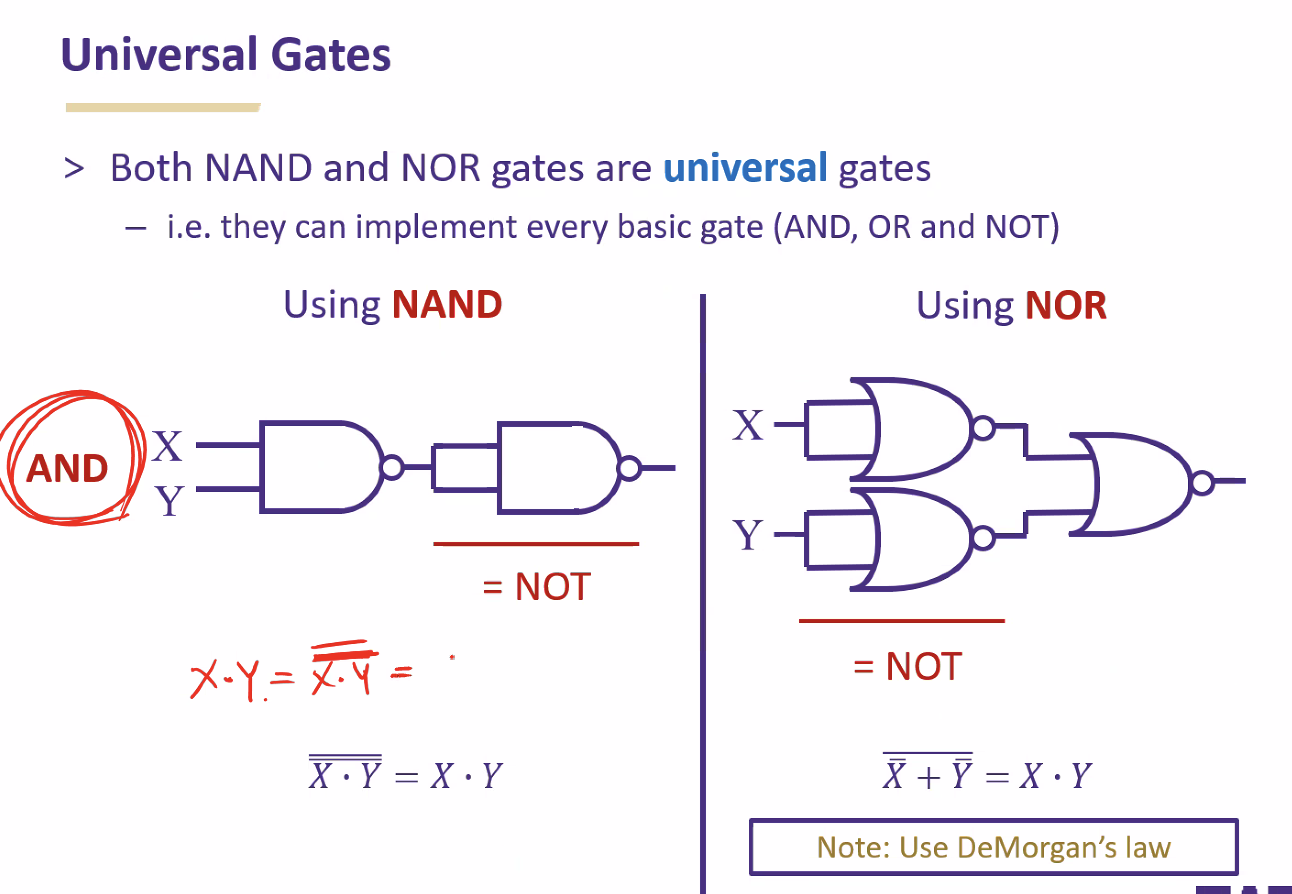

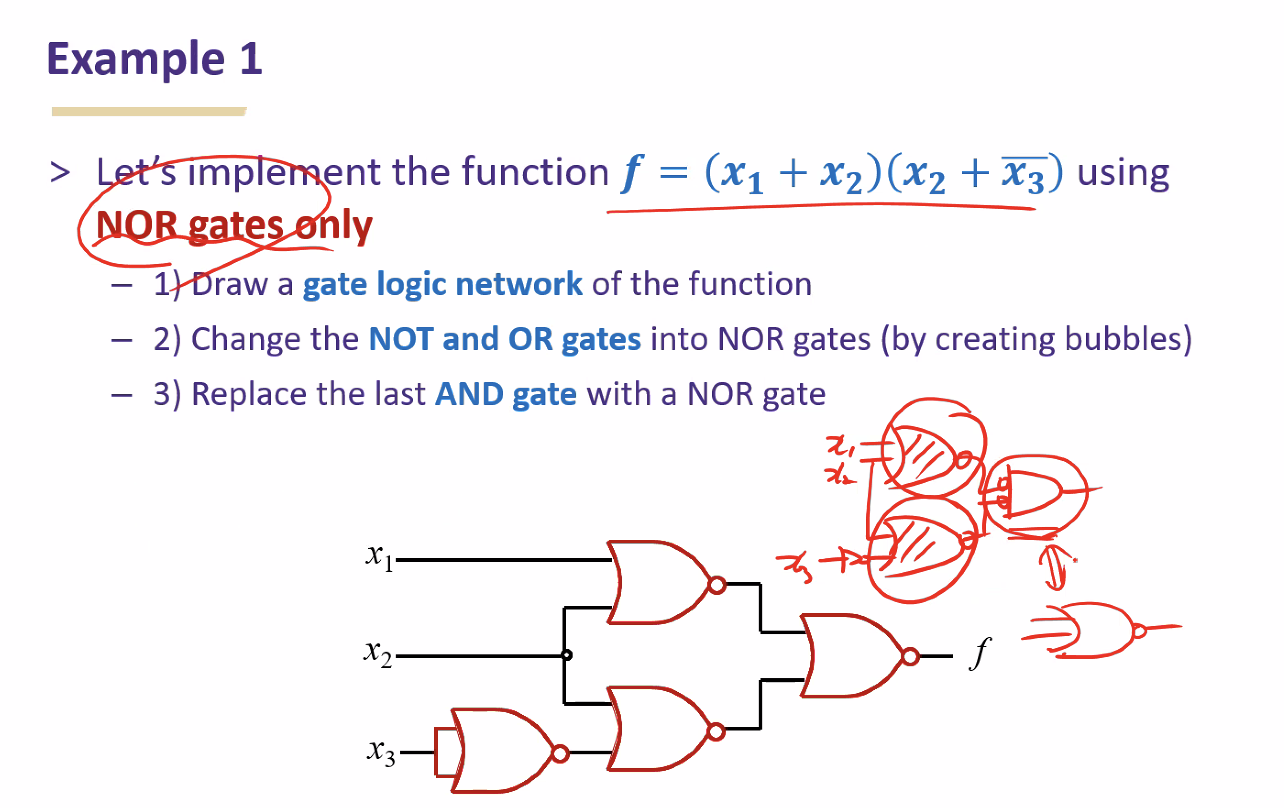

NAND and NOR

DAY 4

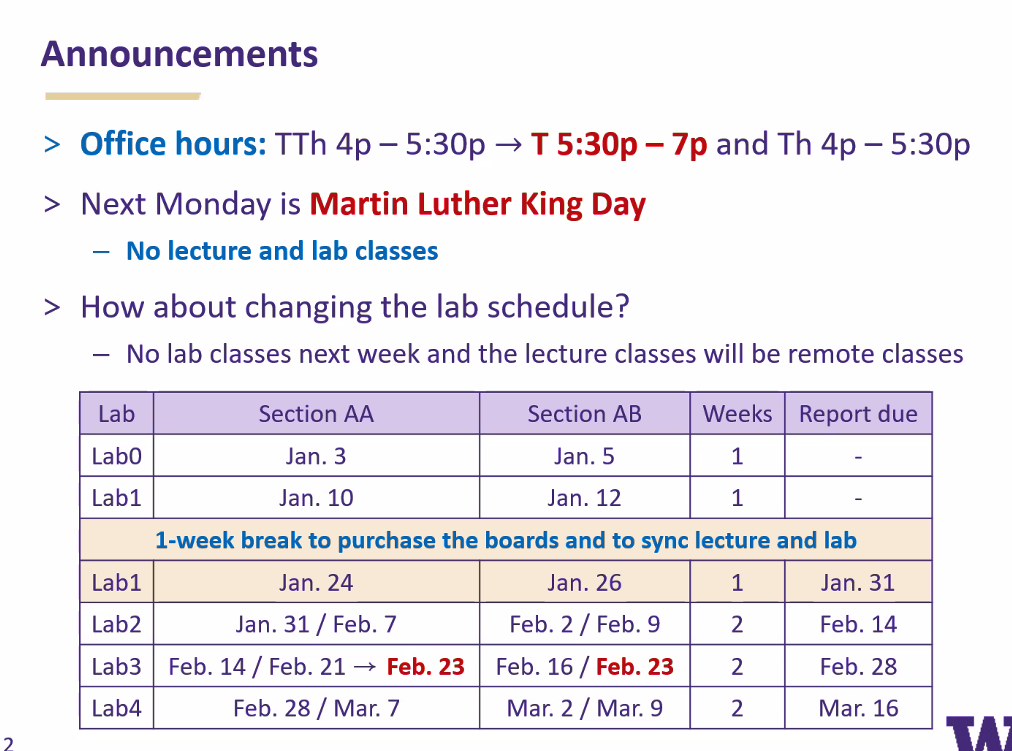

Changed Schedule

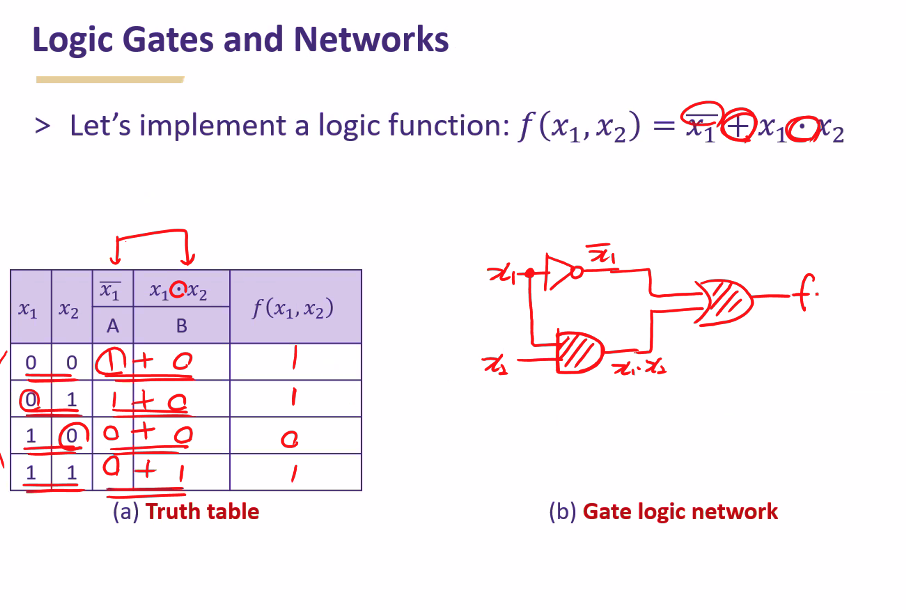

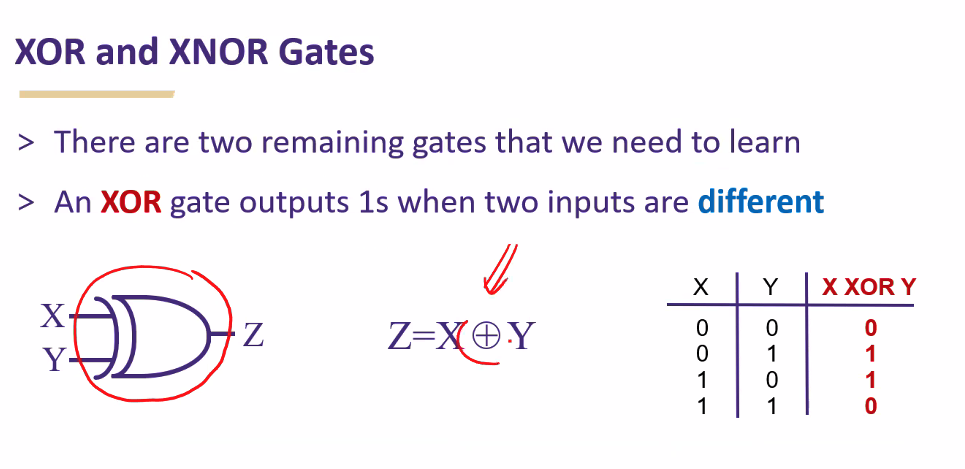

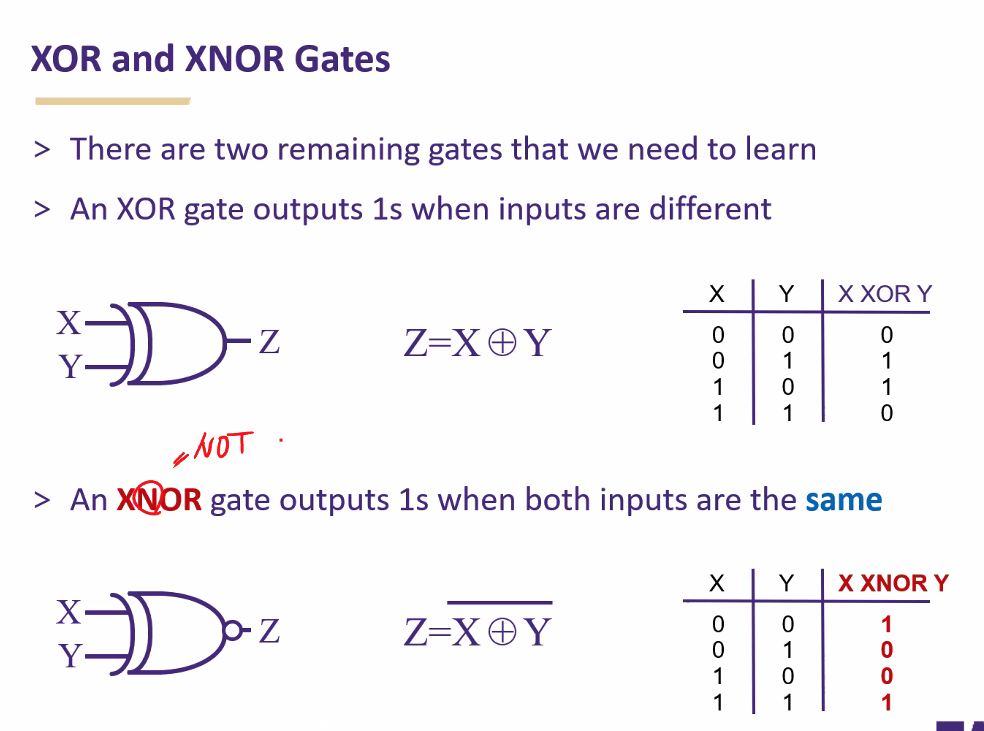

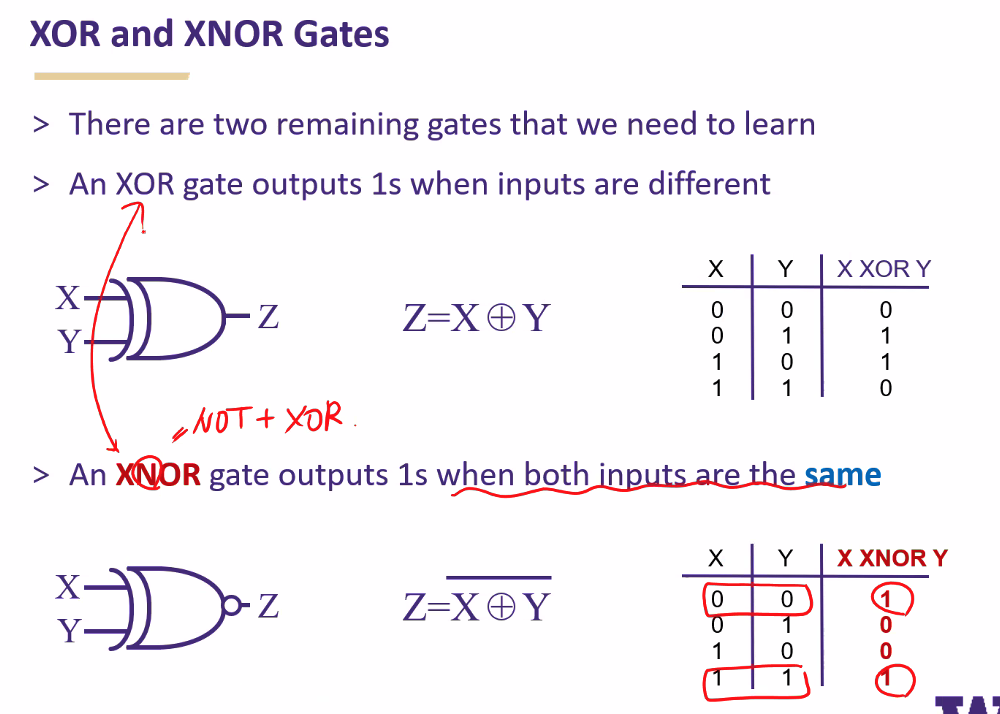

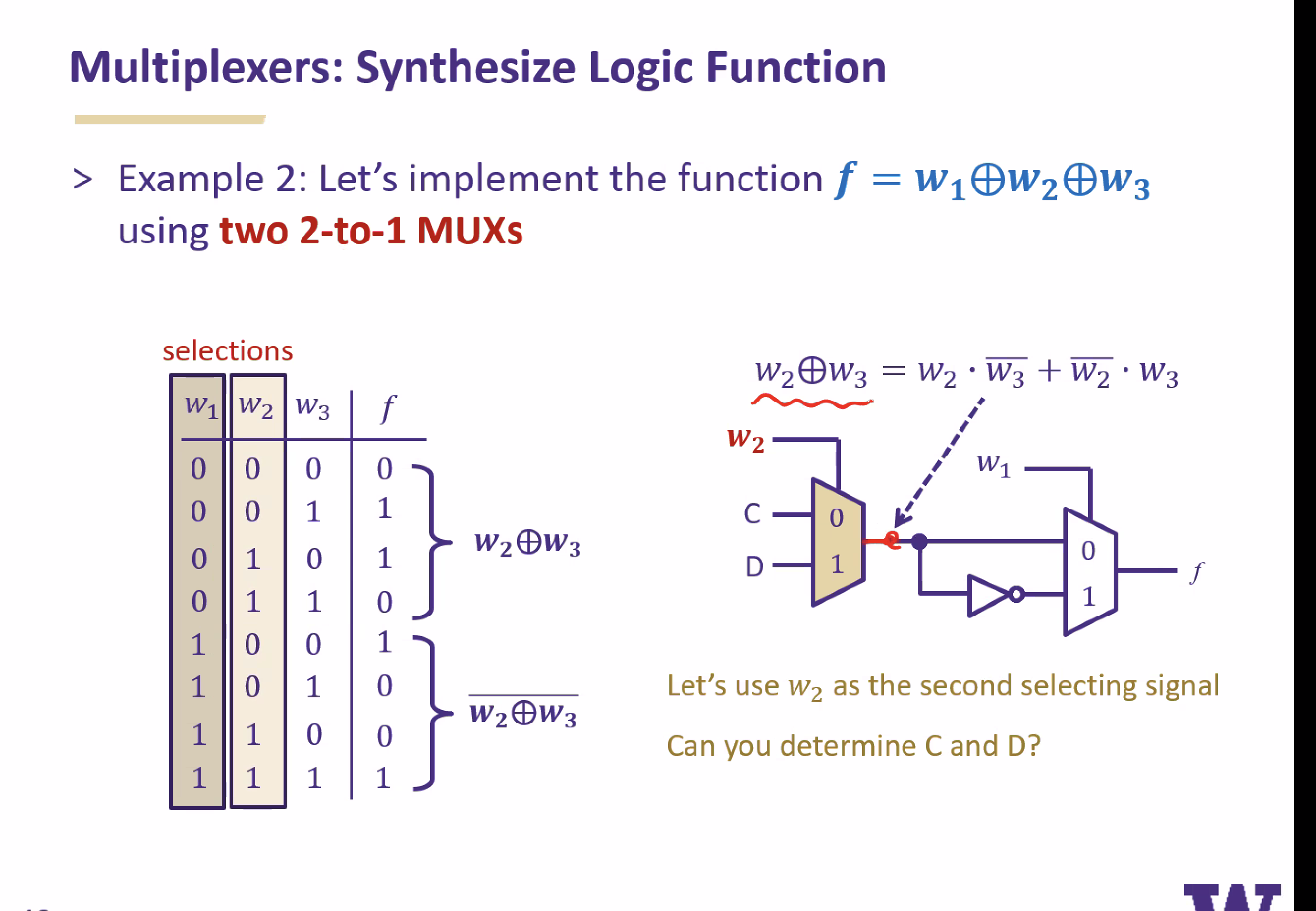

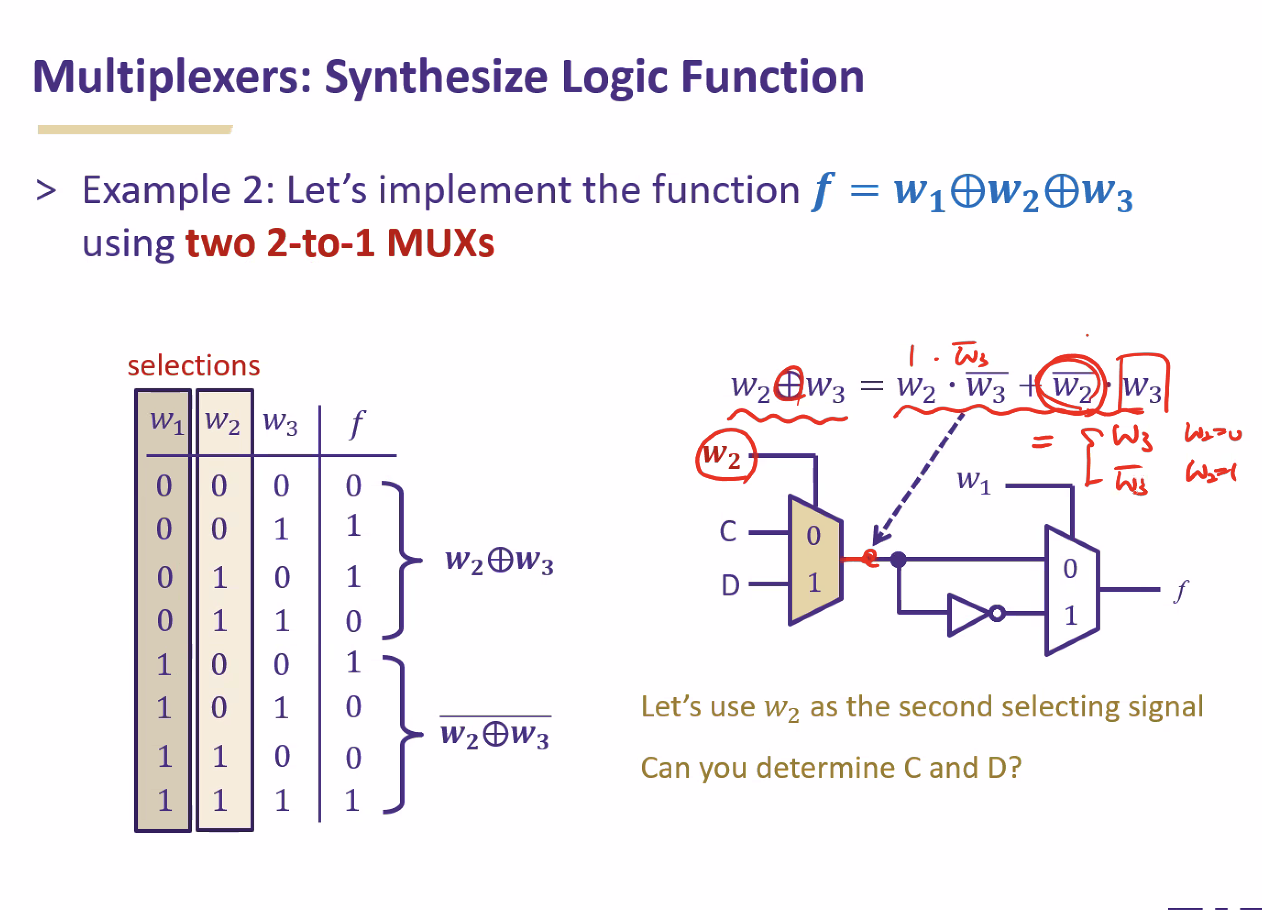

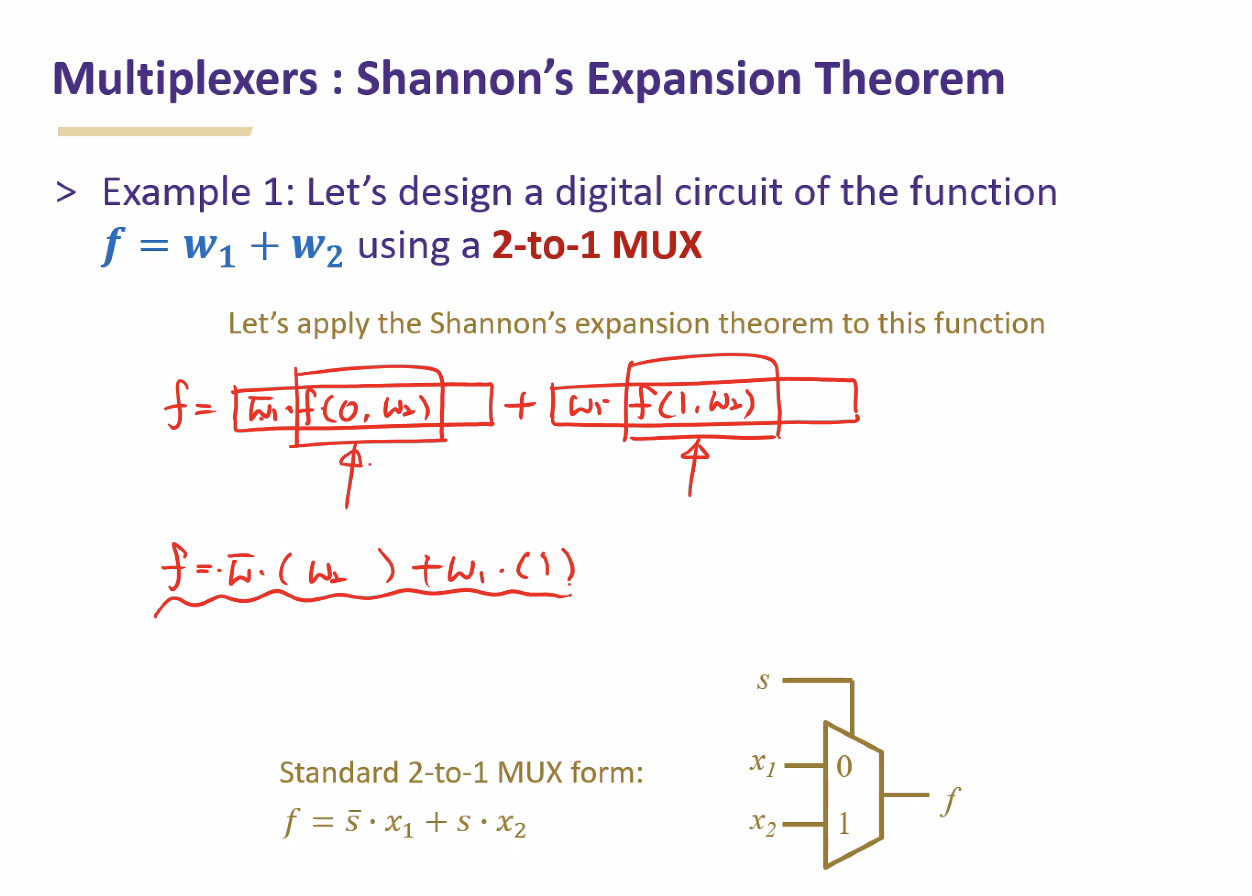

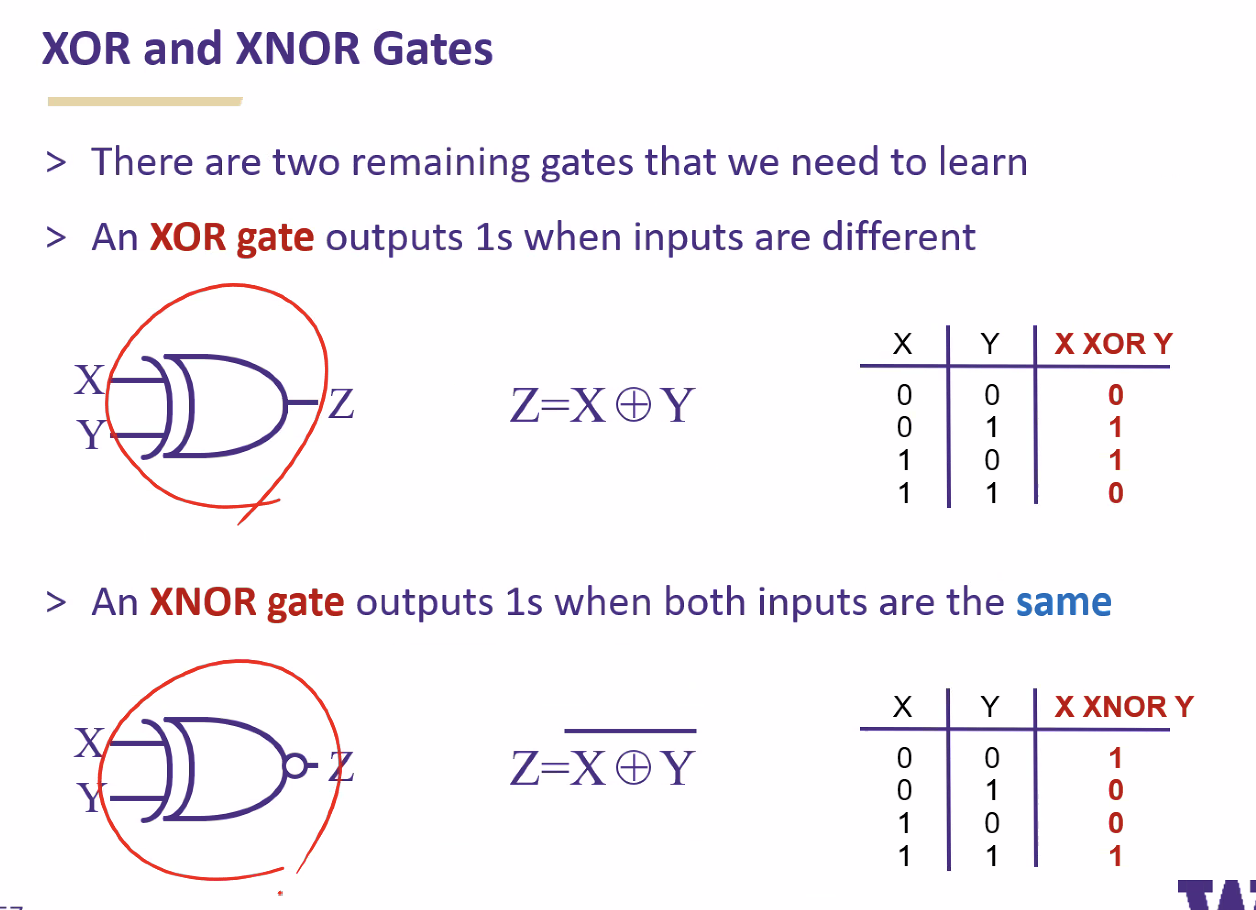

XOR output once when the output is different

Lecture 5

Lecture 6

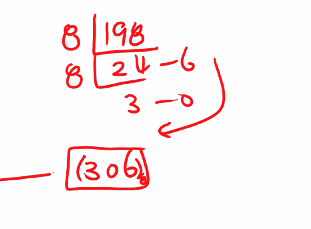

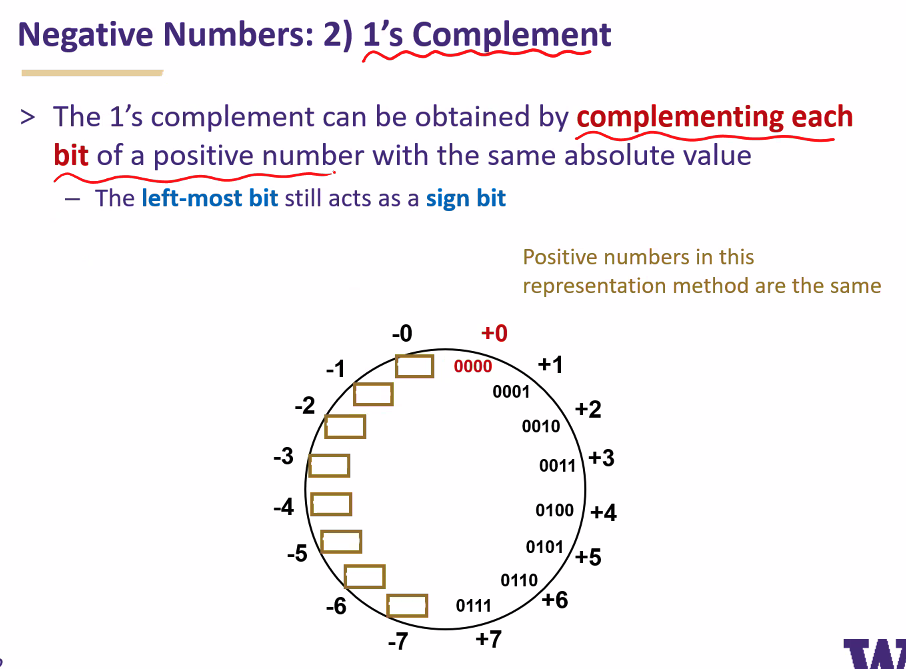

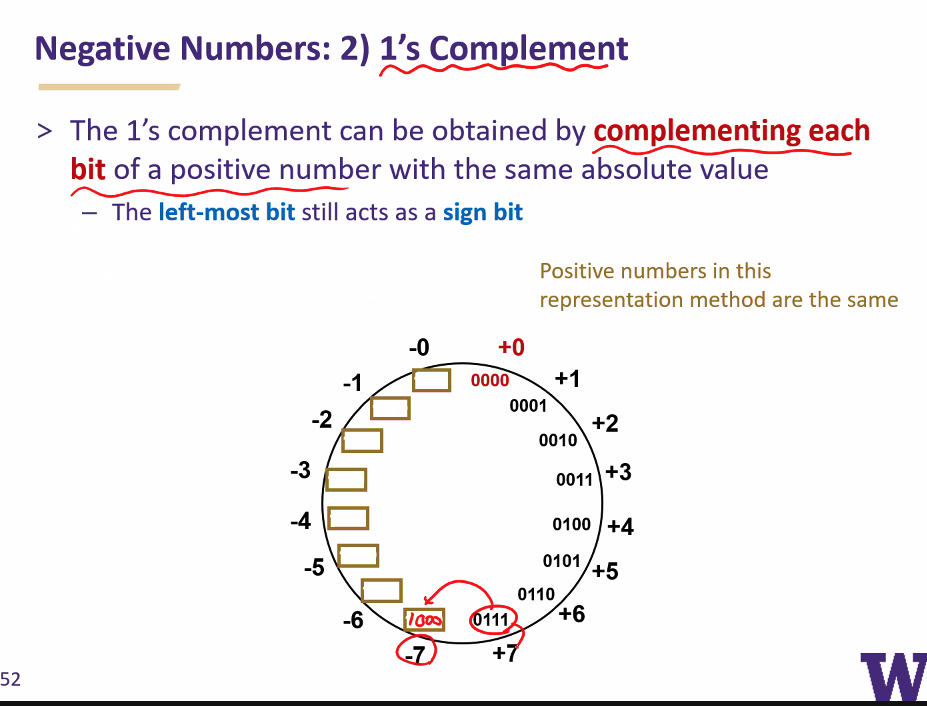

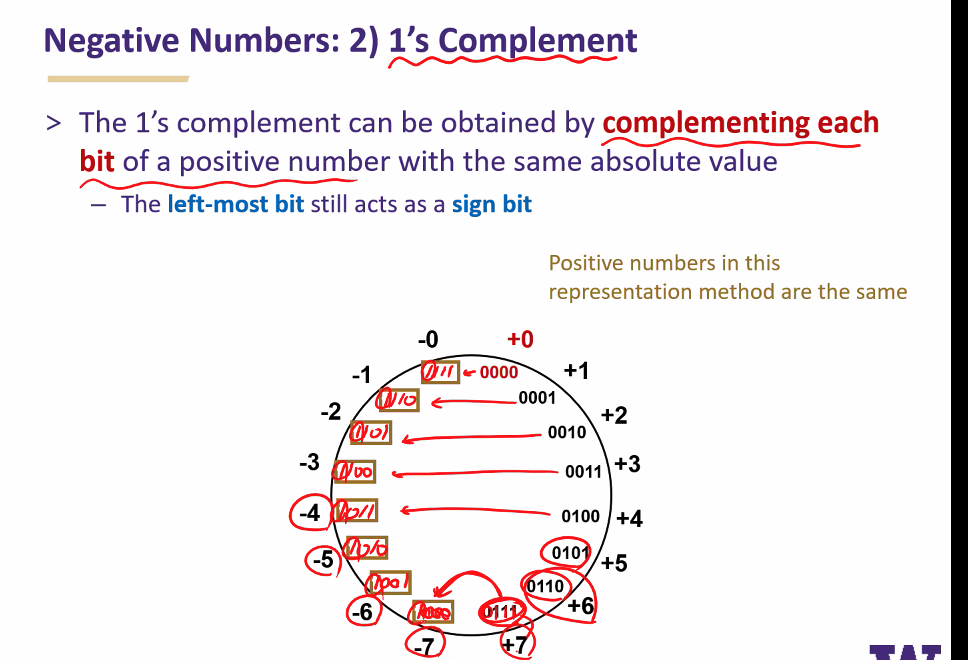

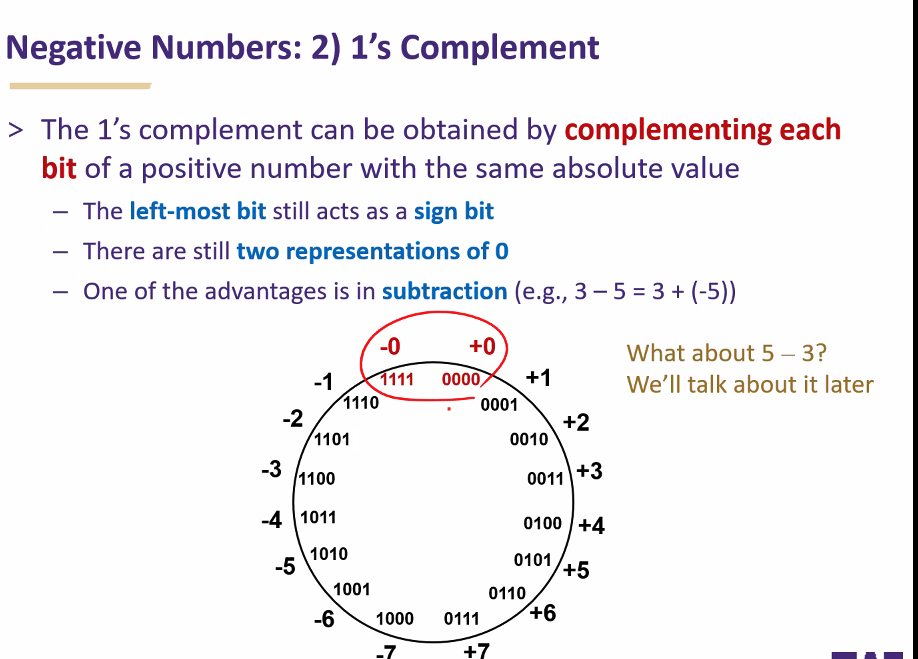

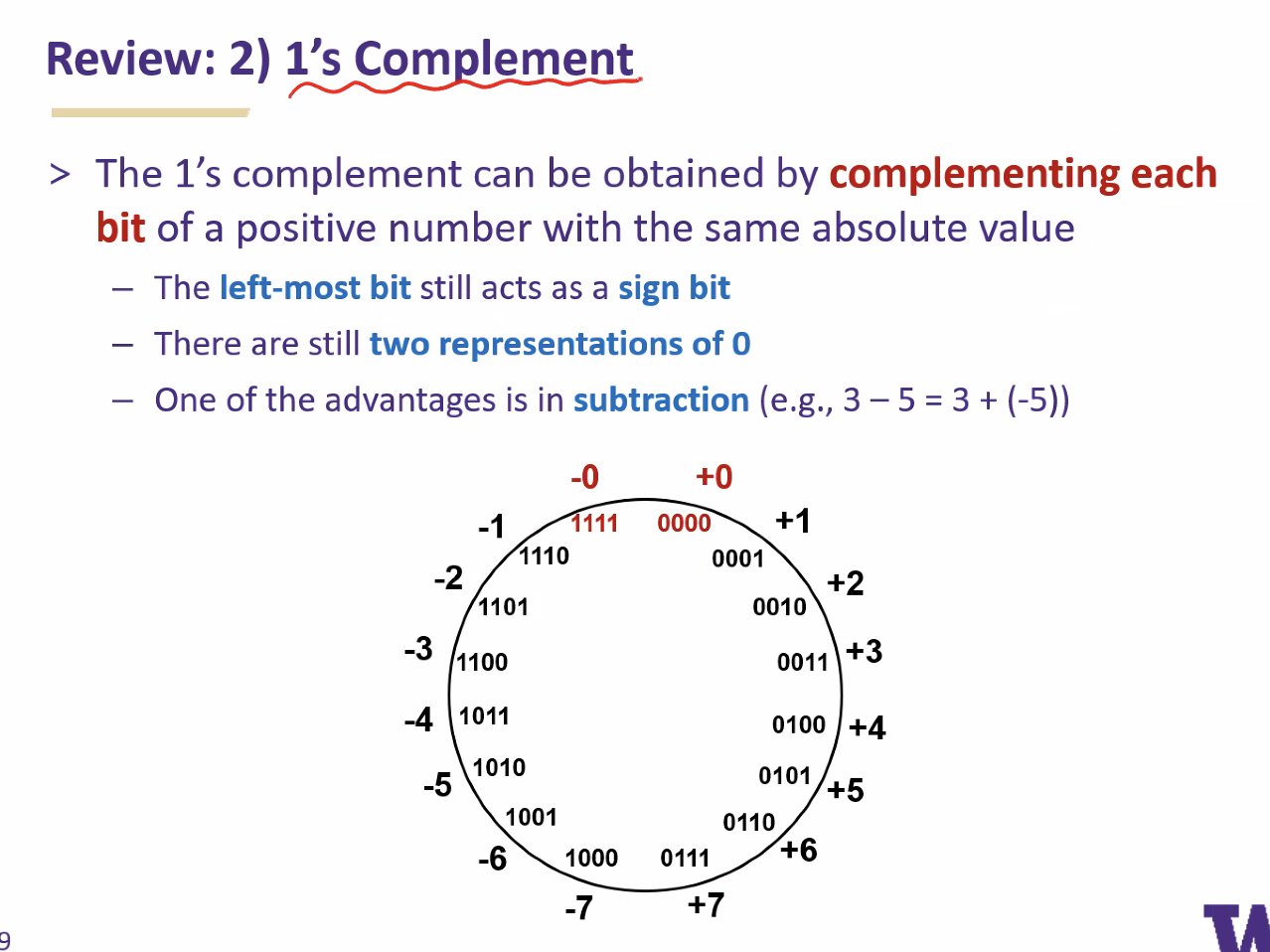

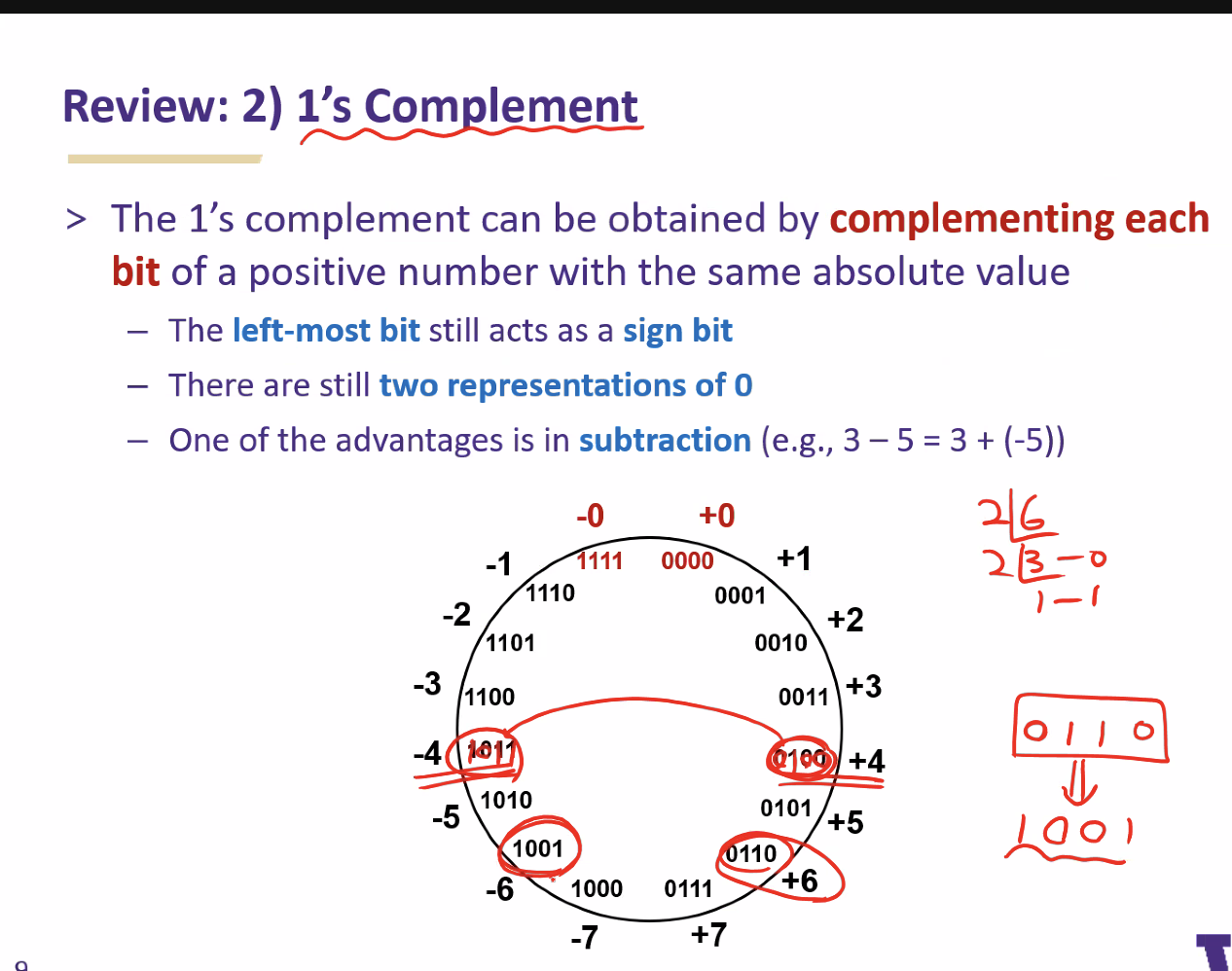

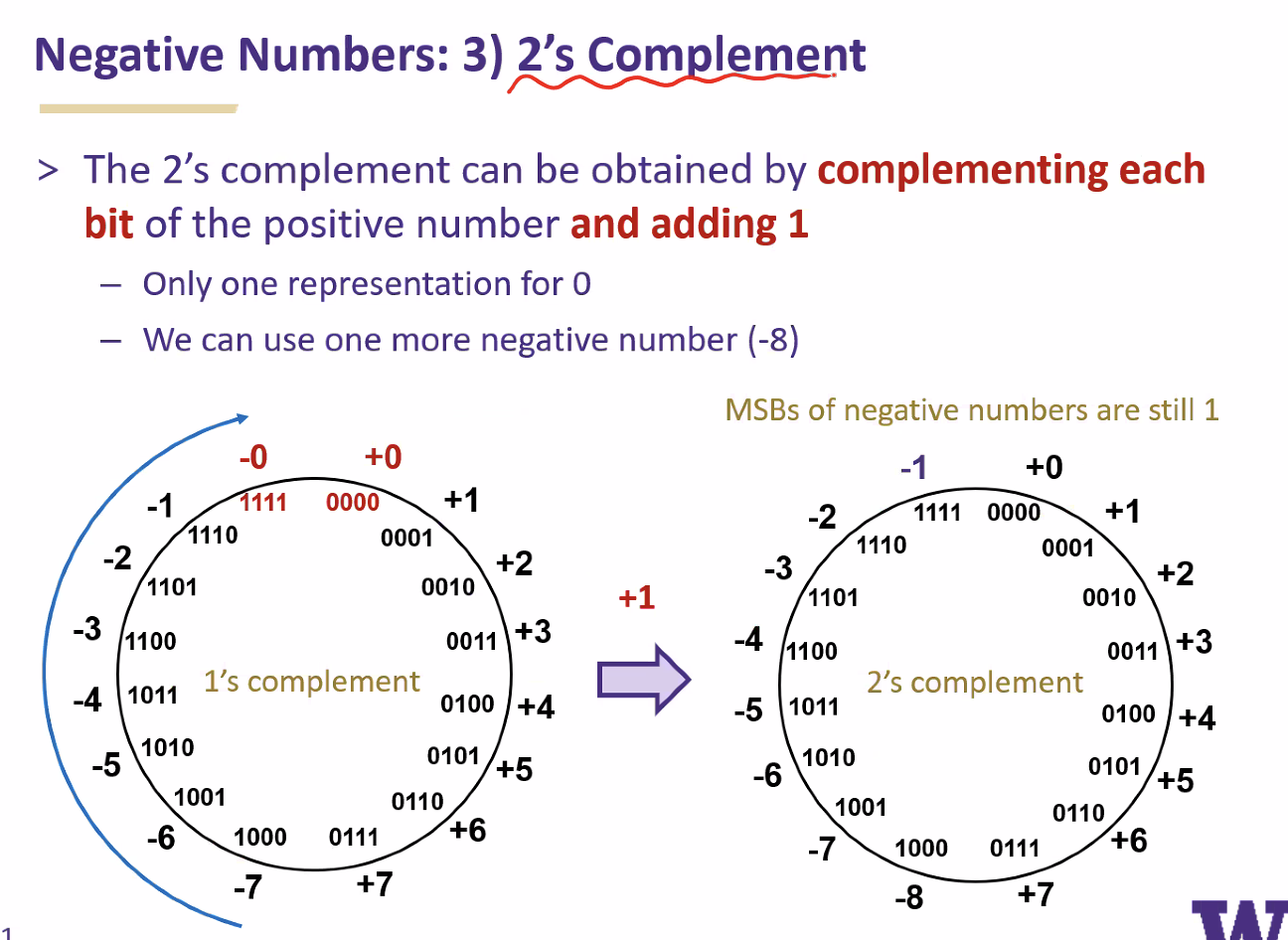

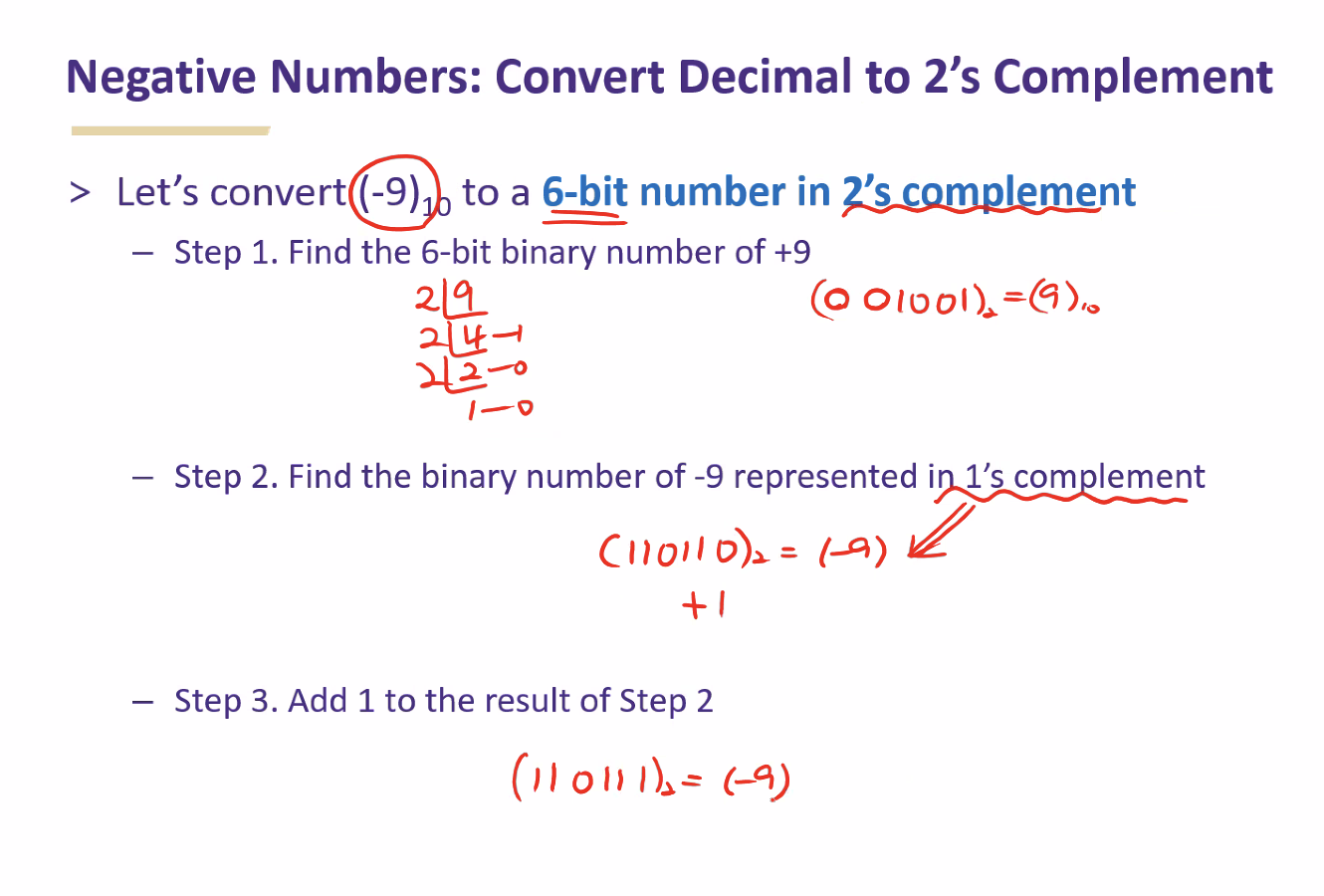

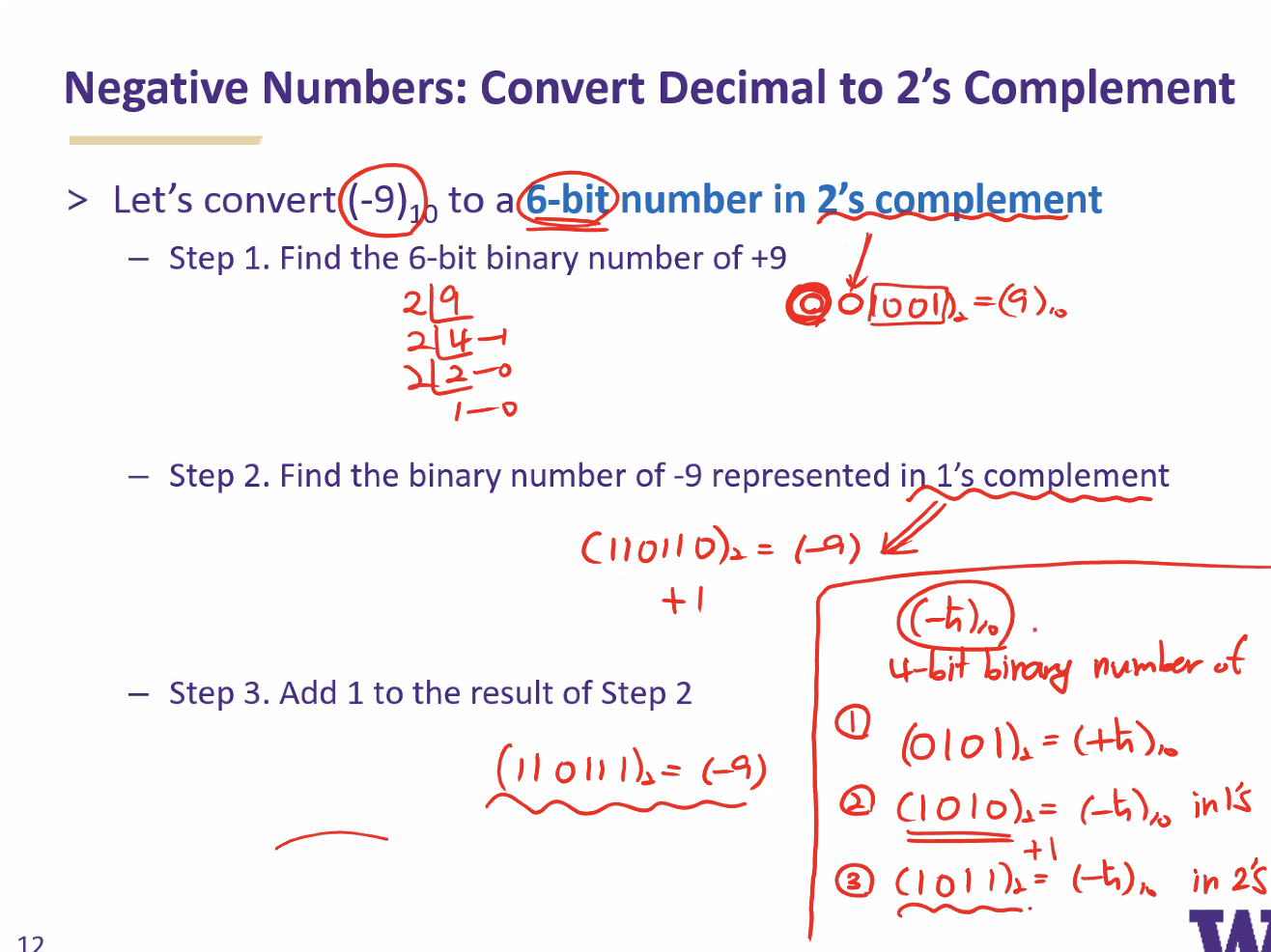

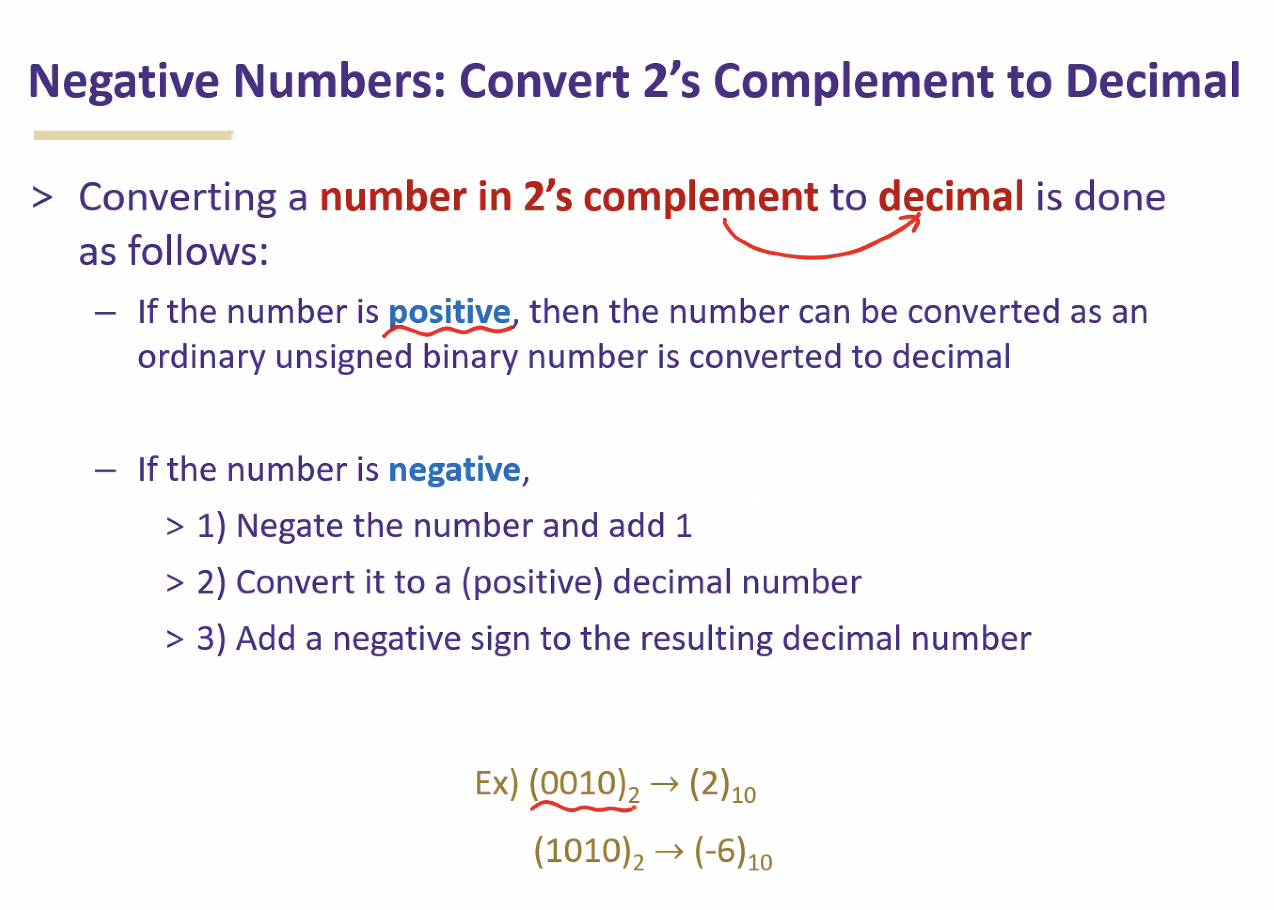

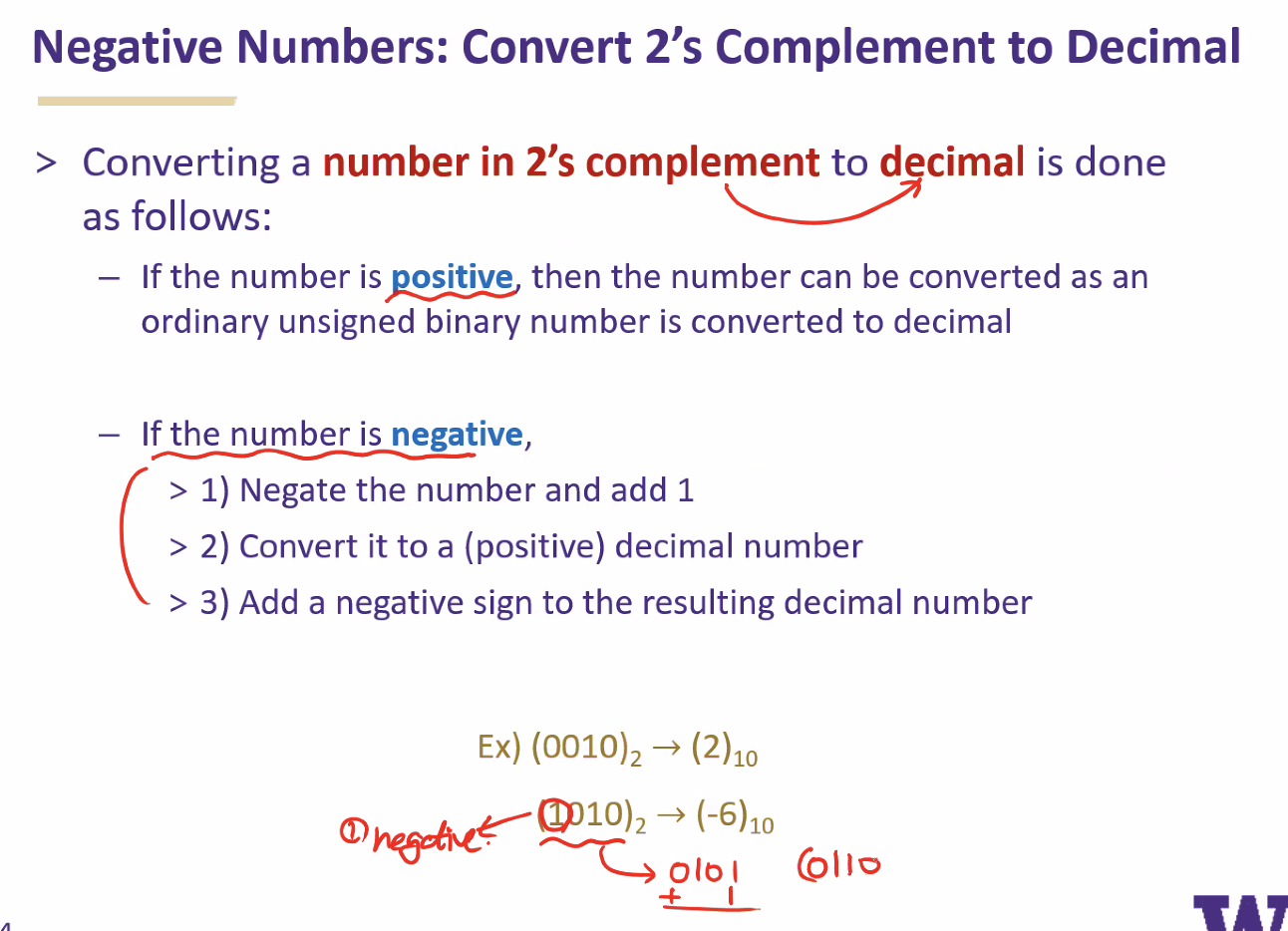

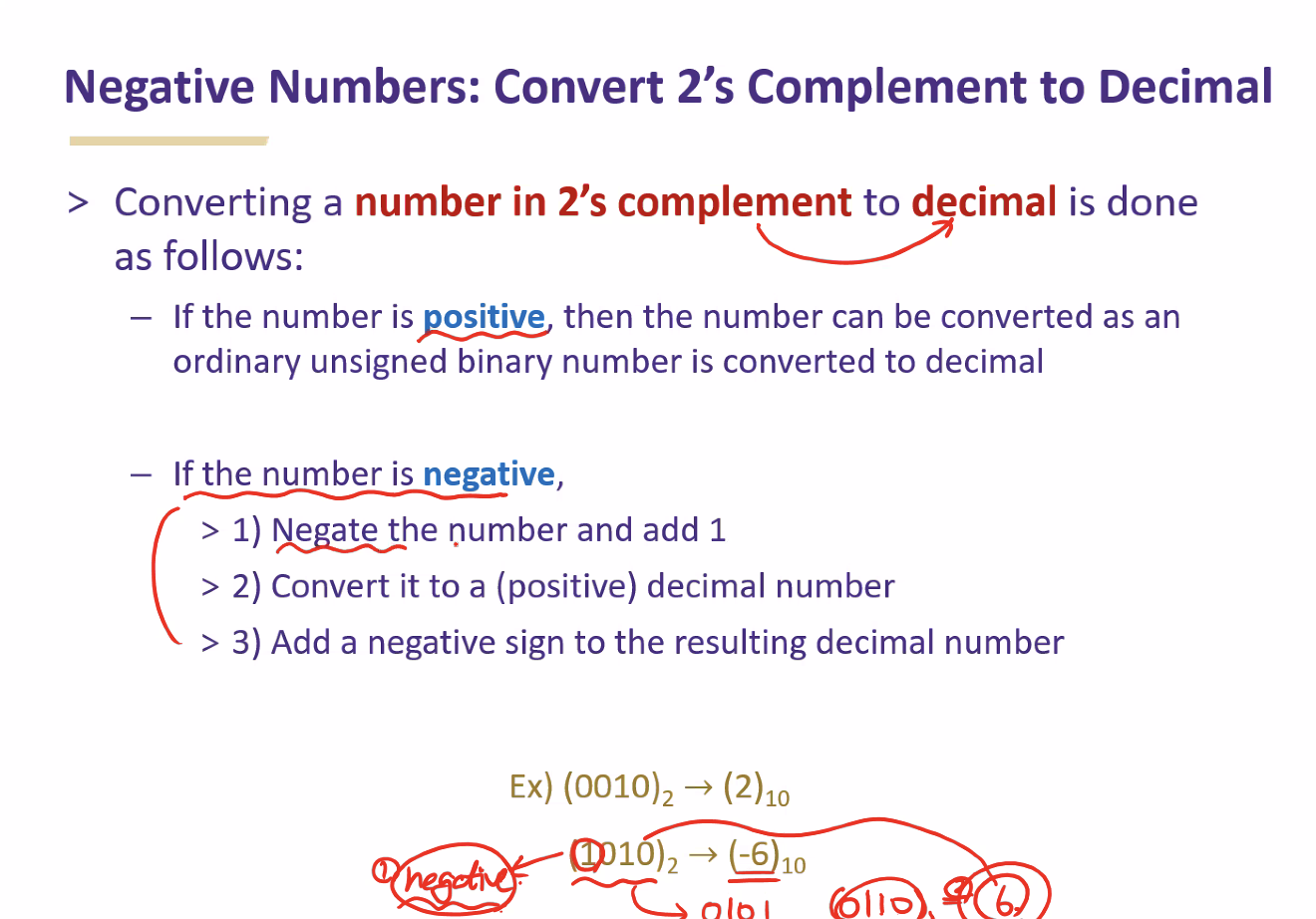

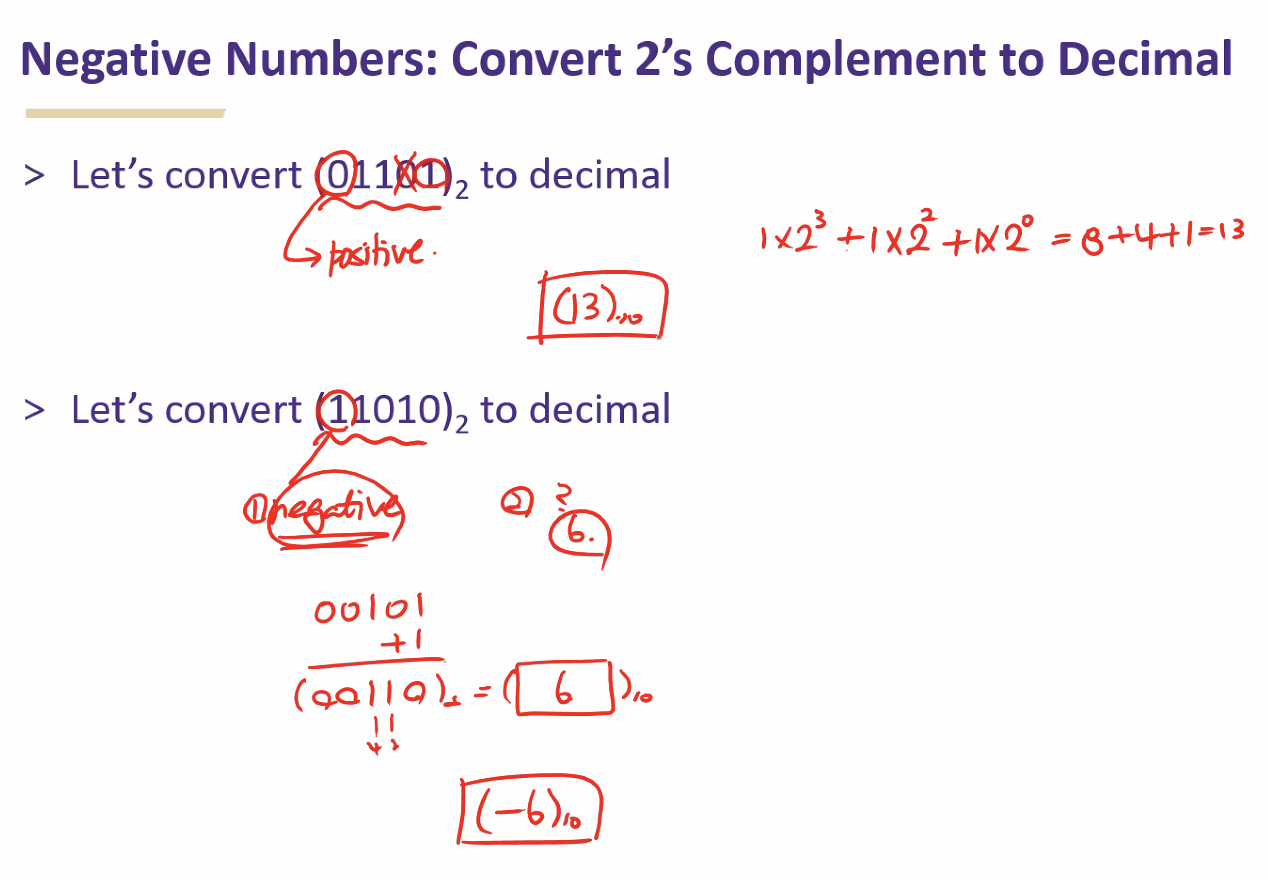

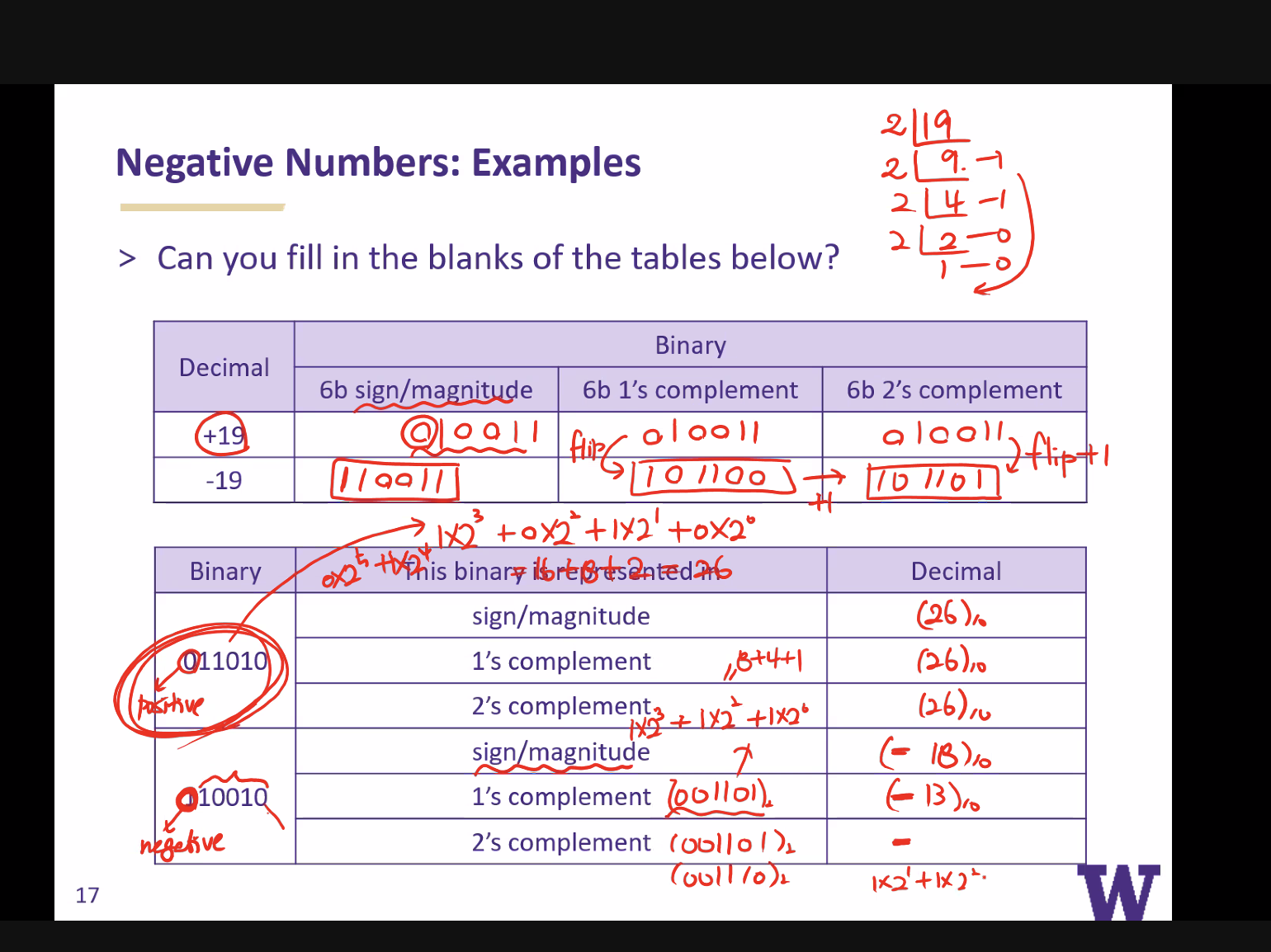

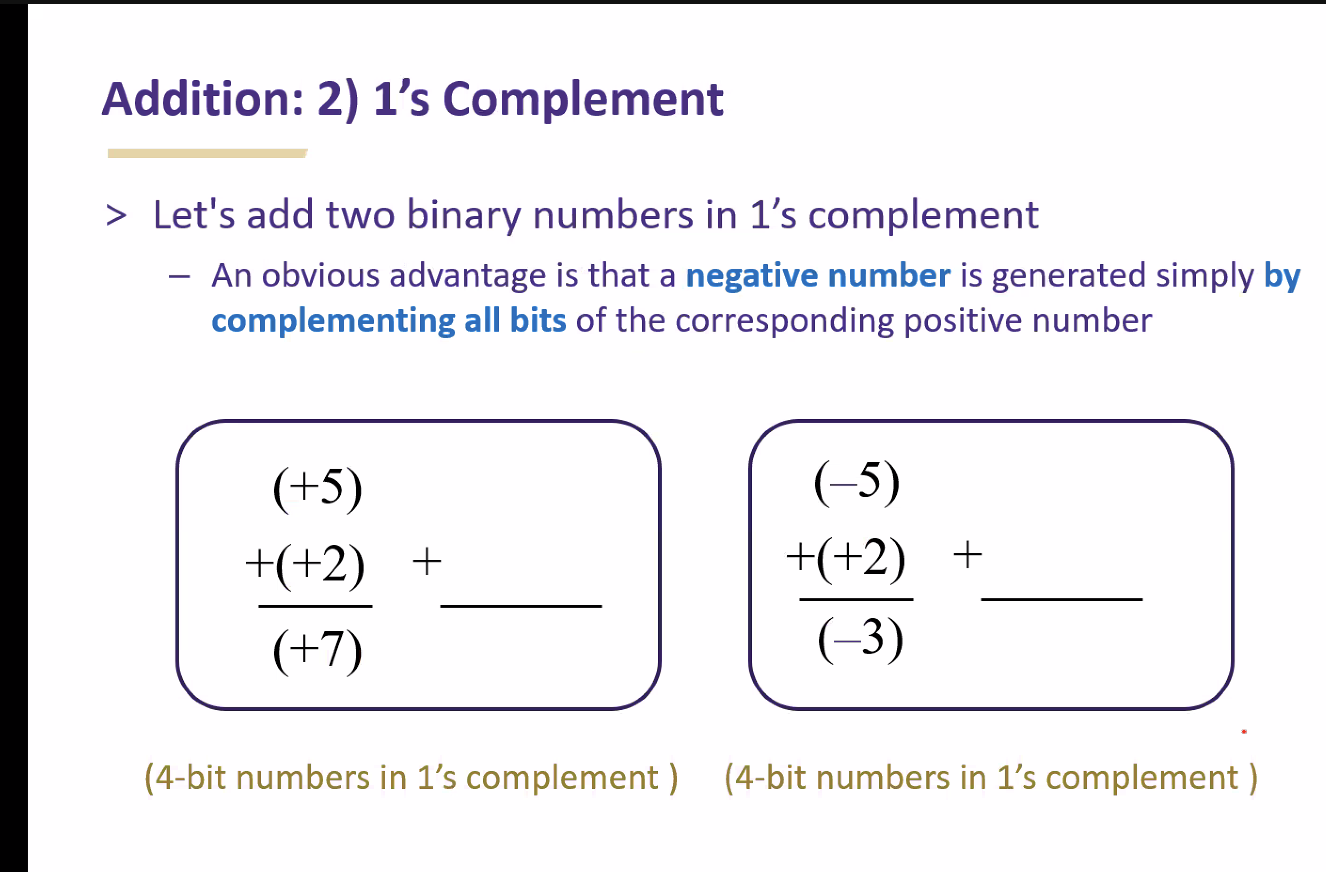

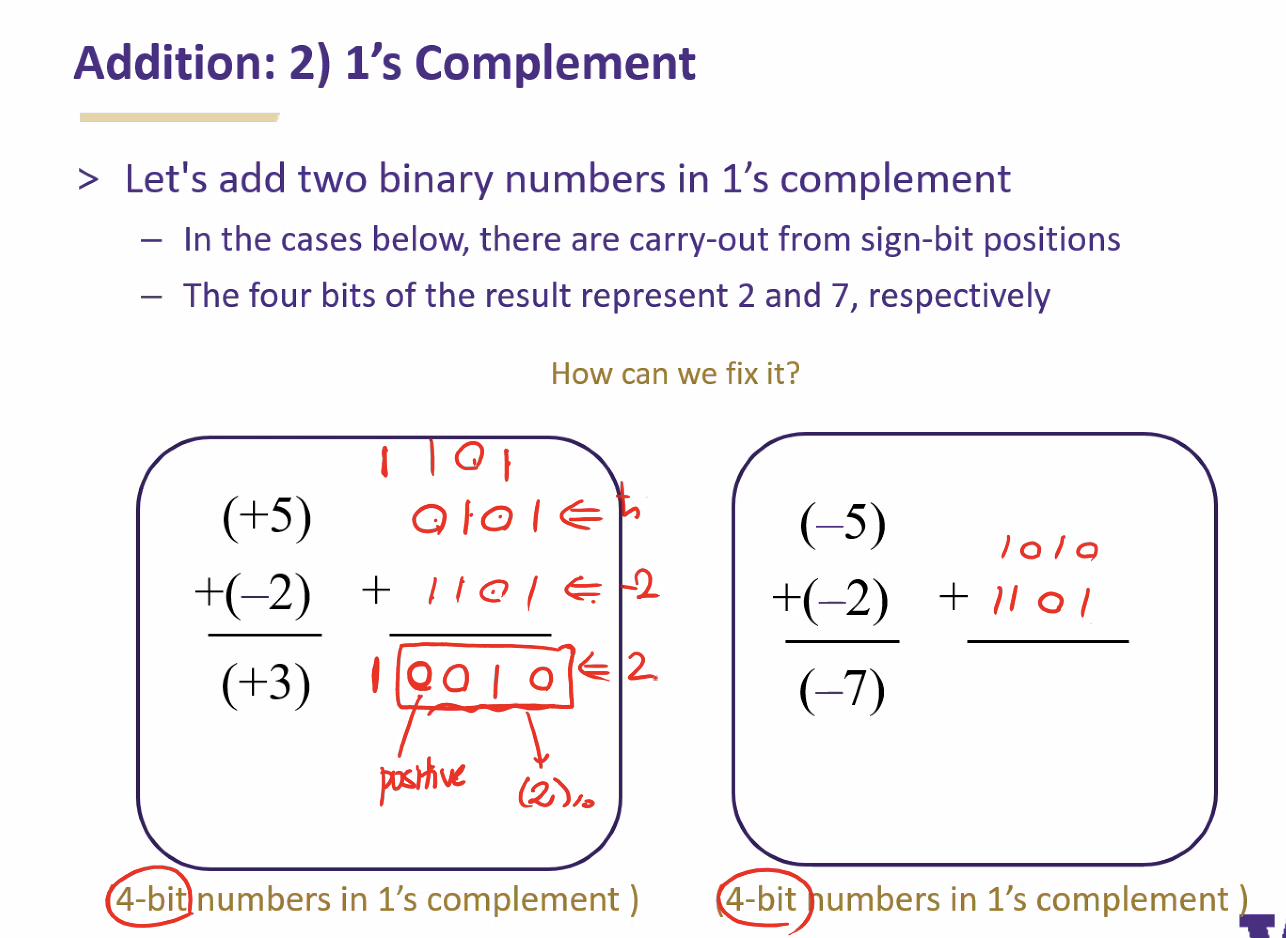

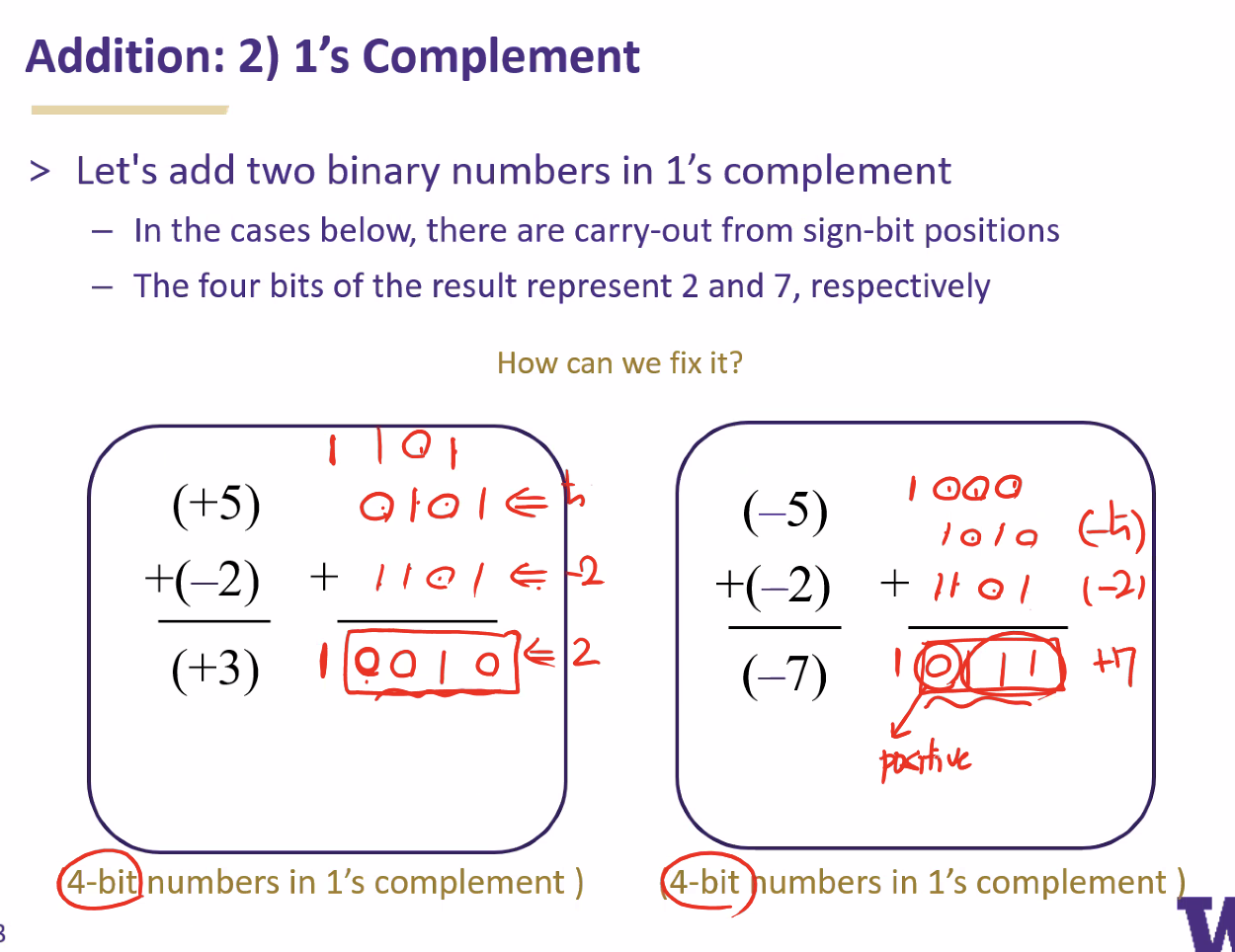

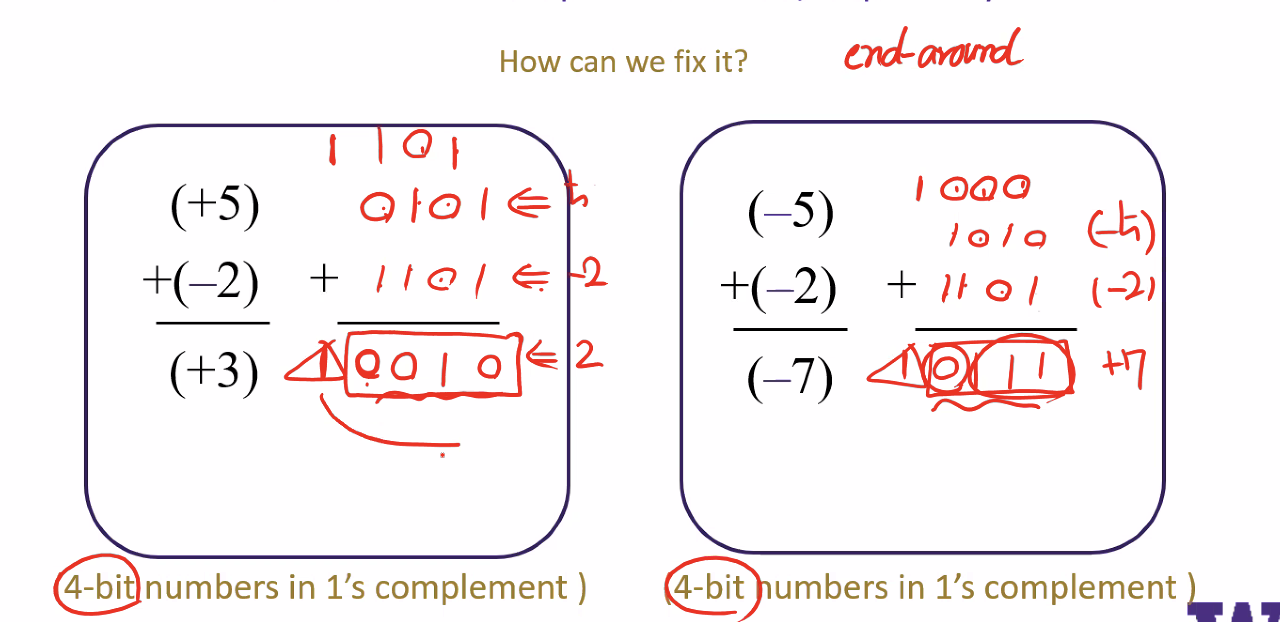

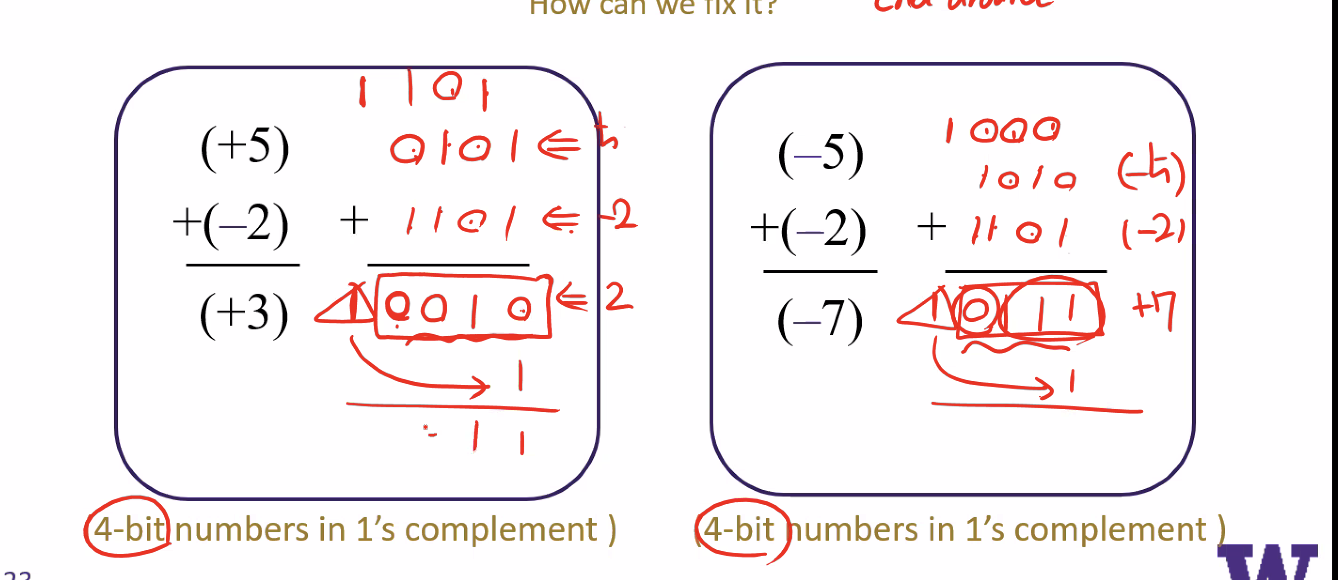

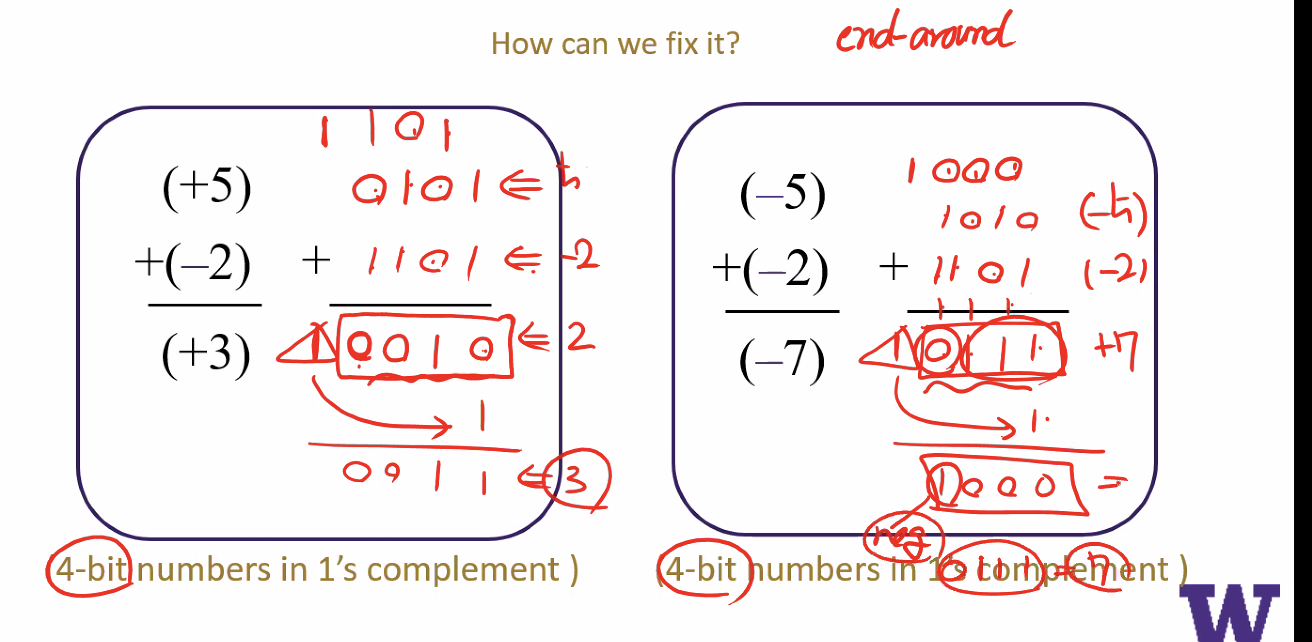

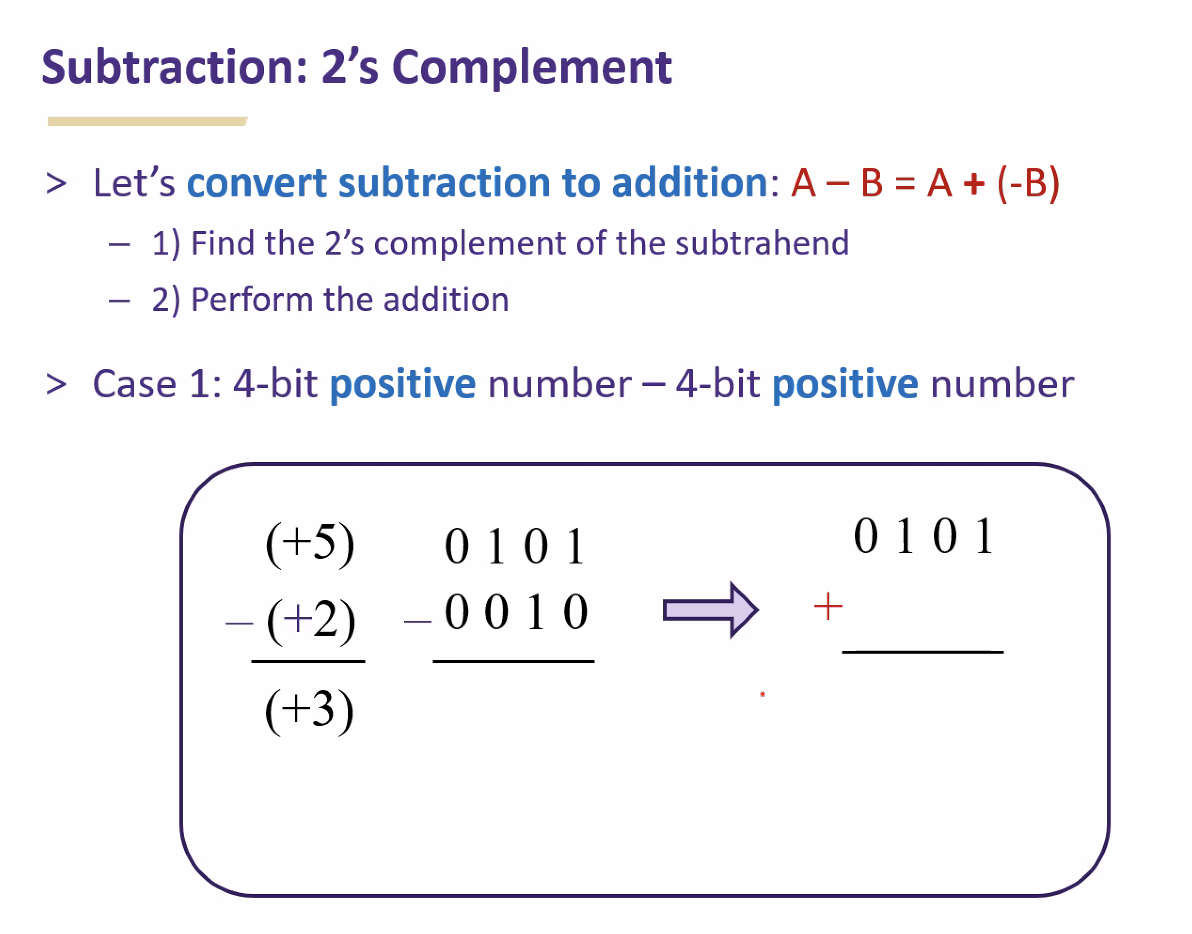

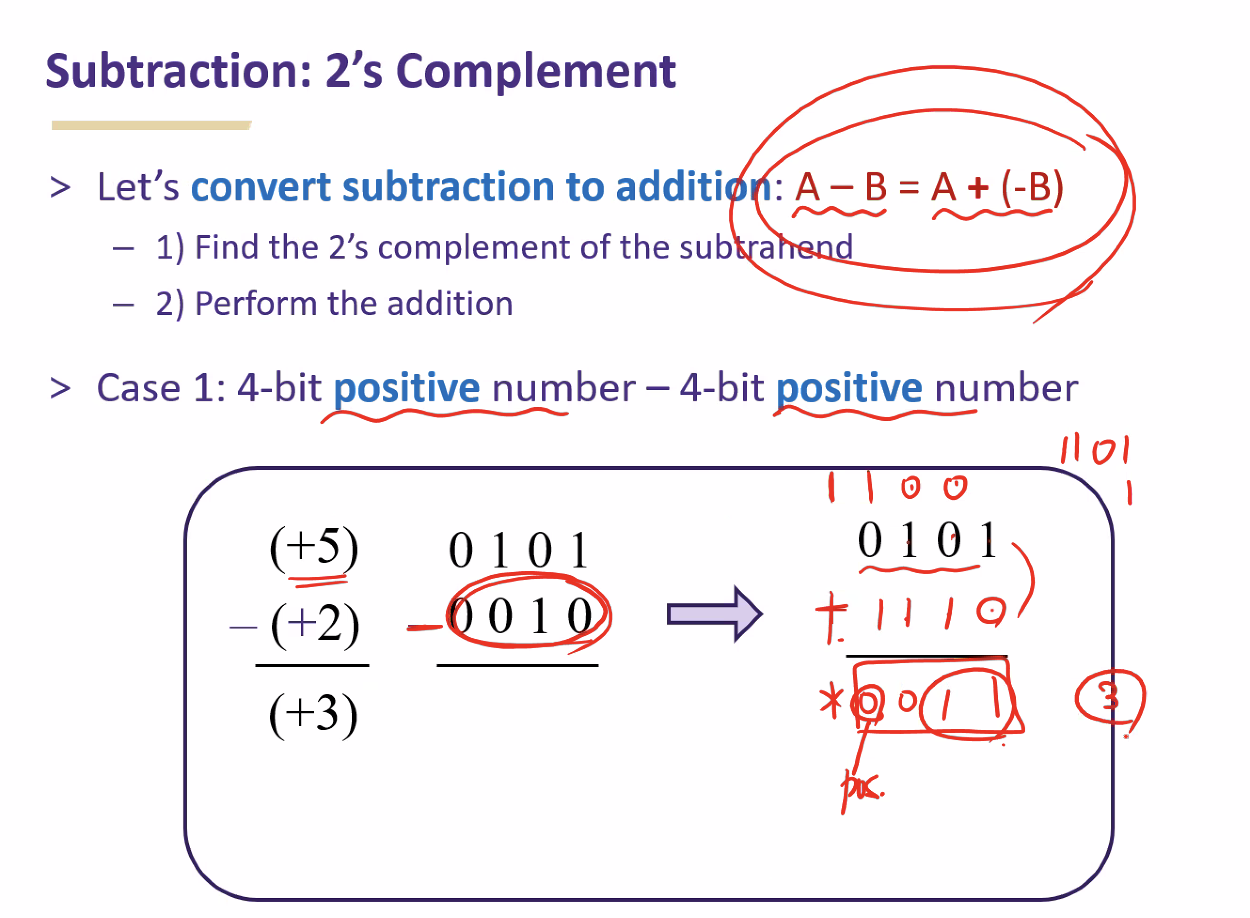

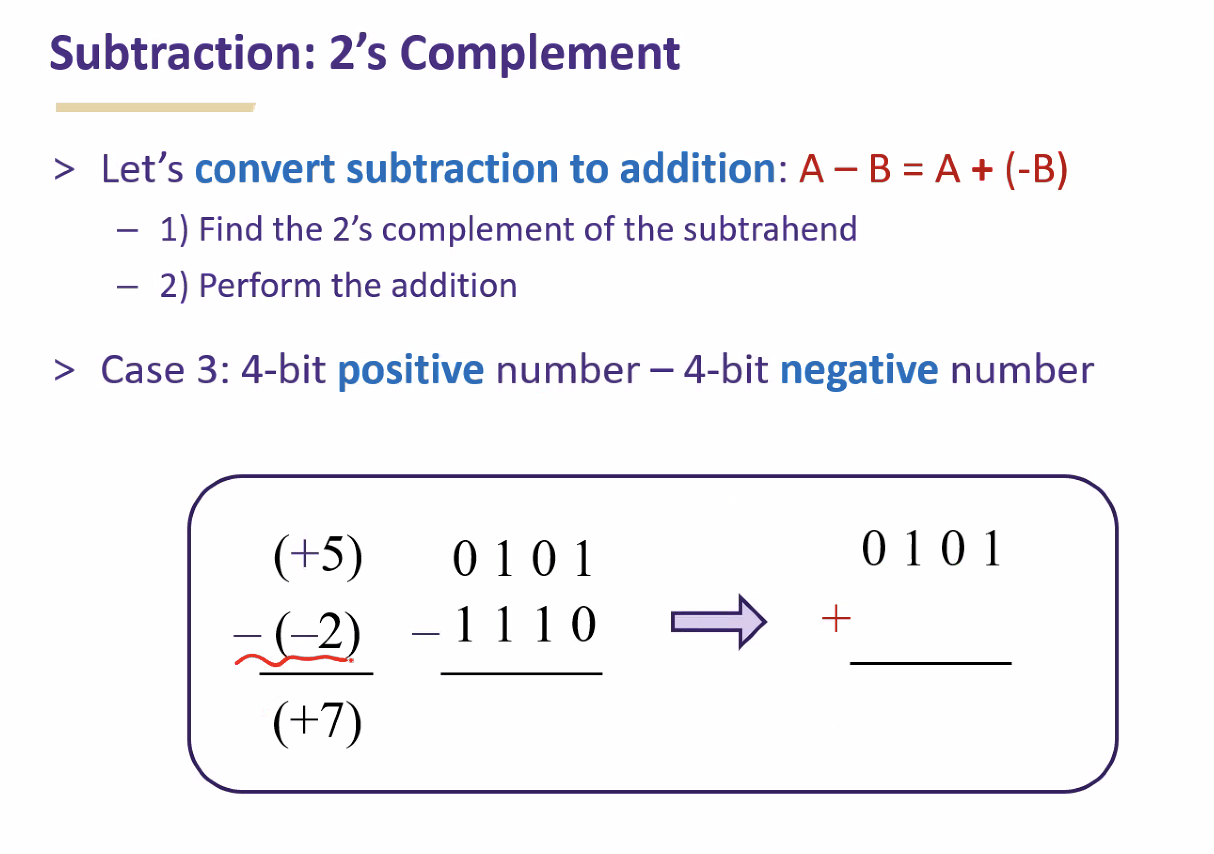

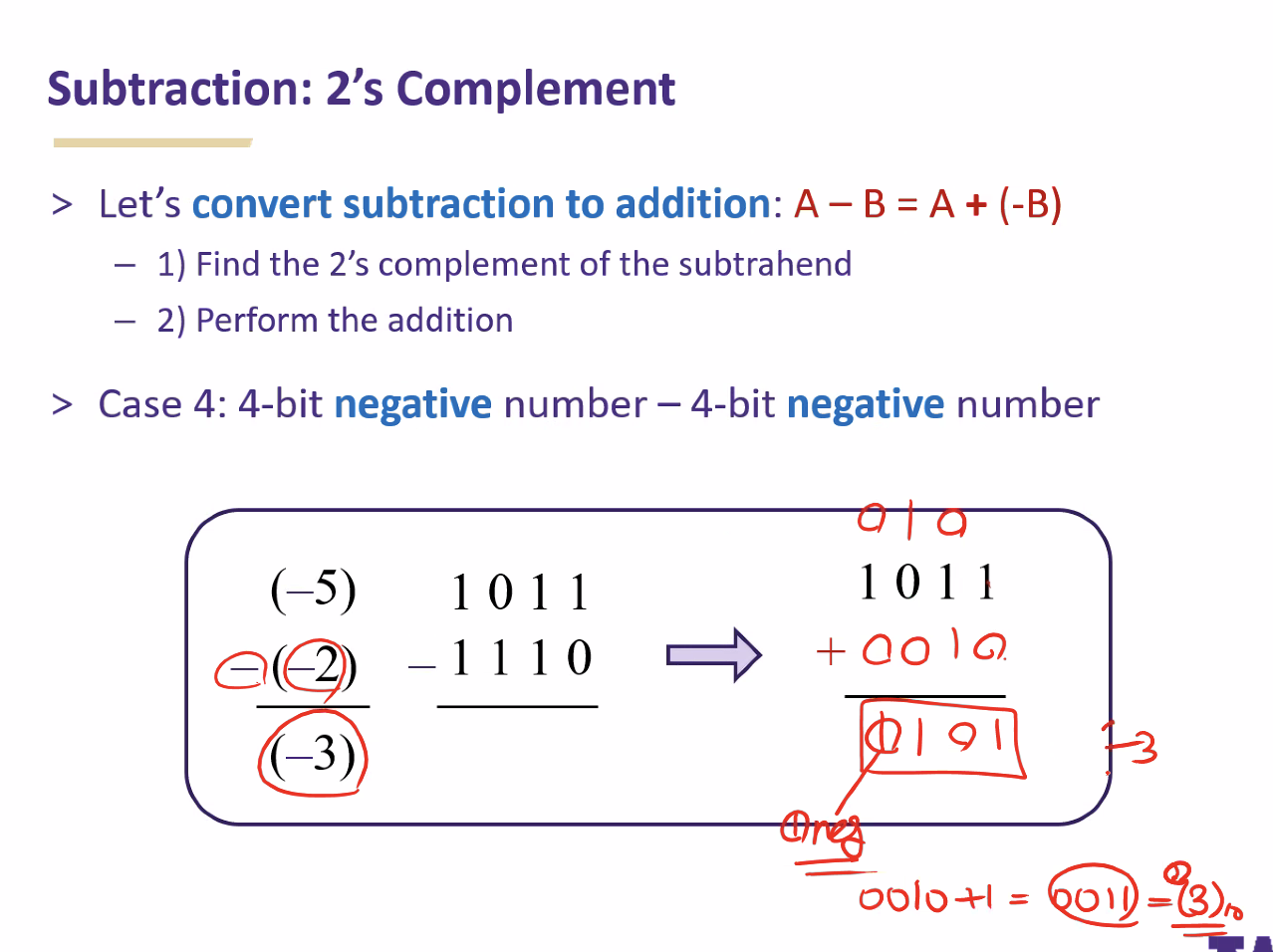

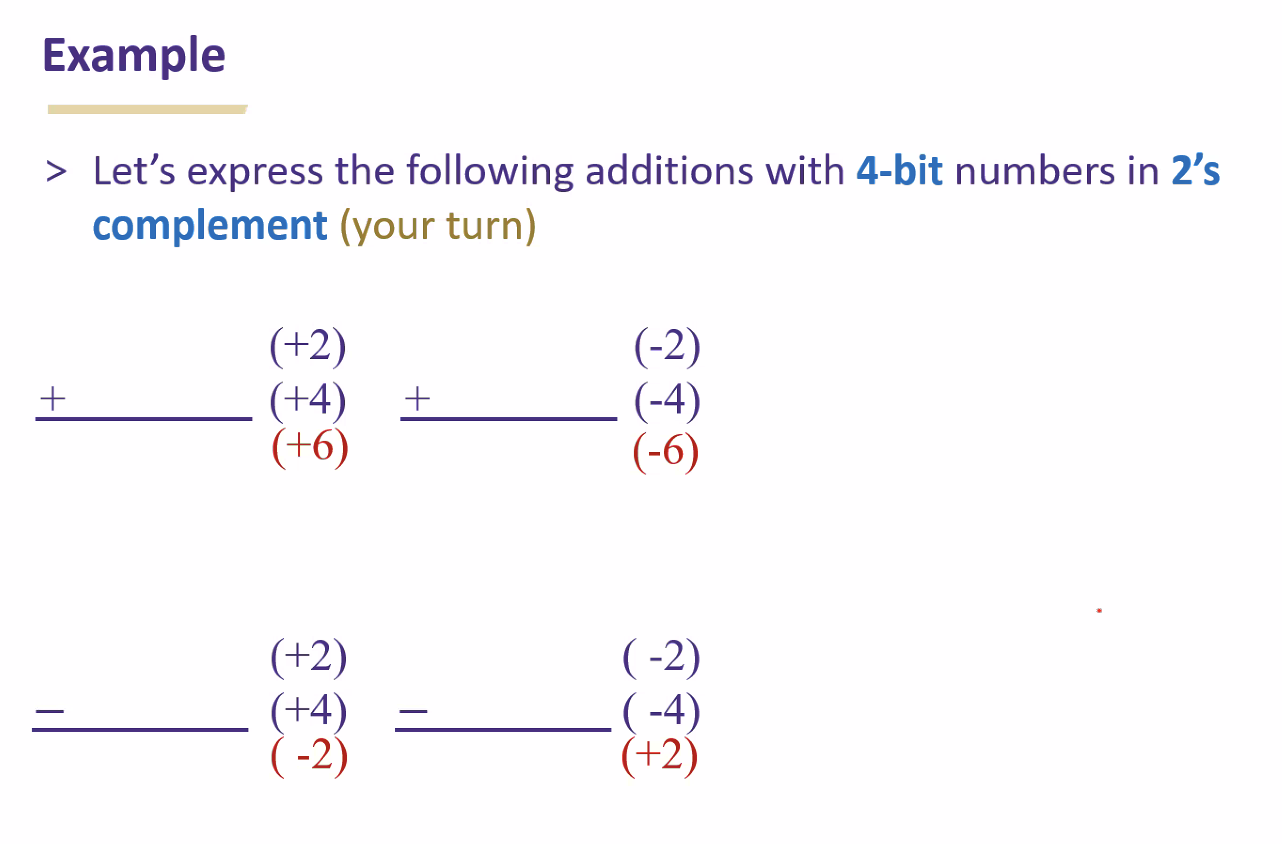

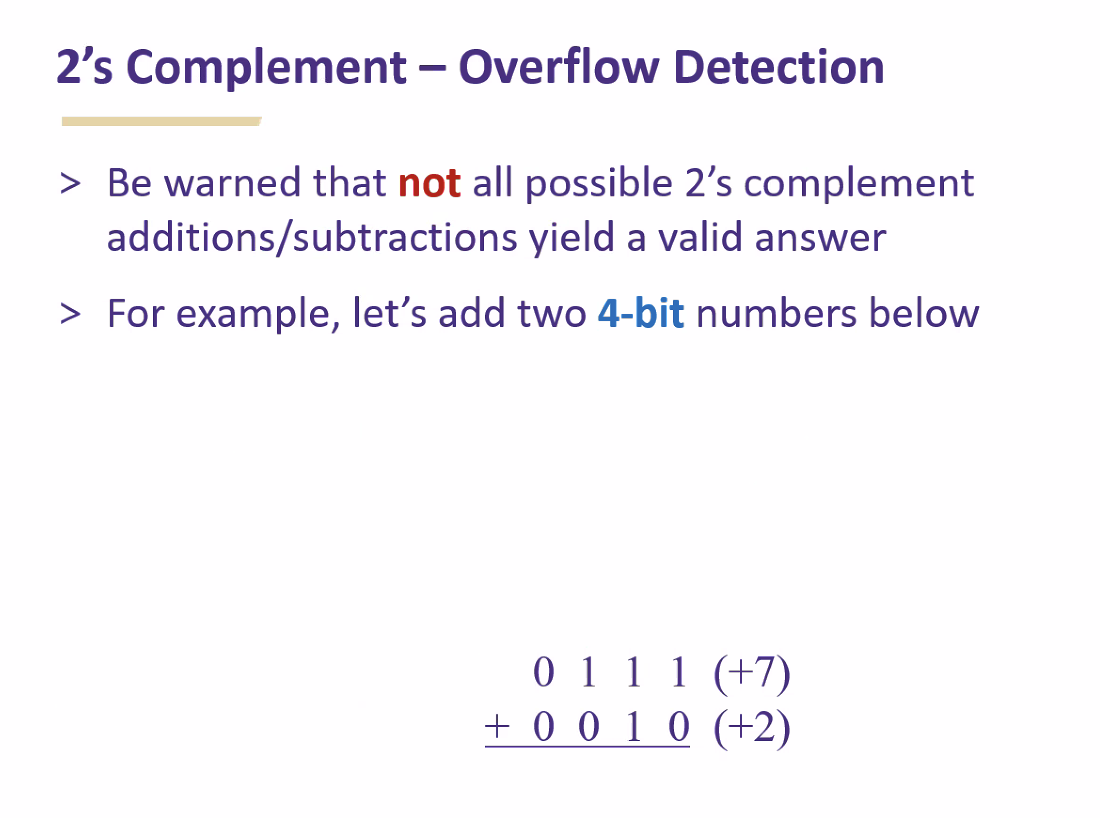

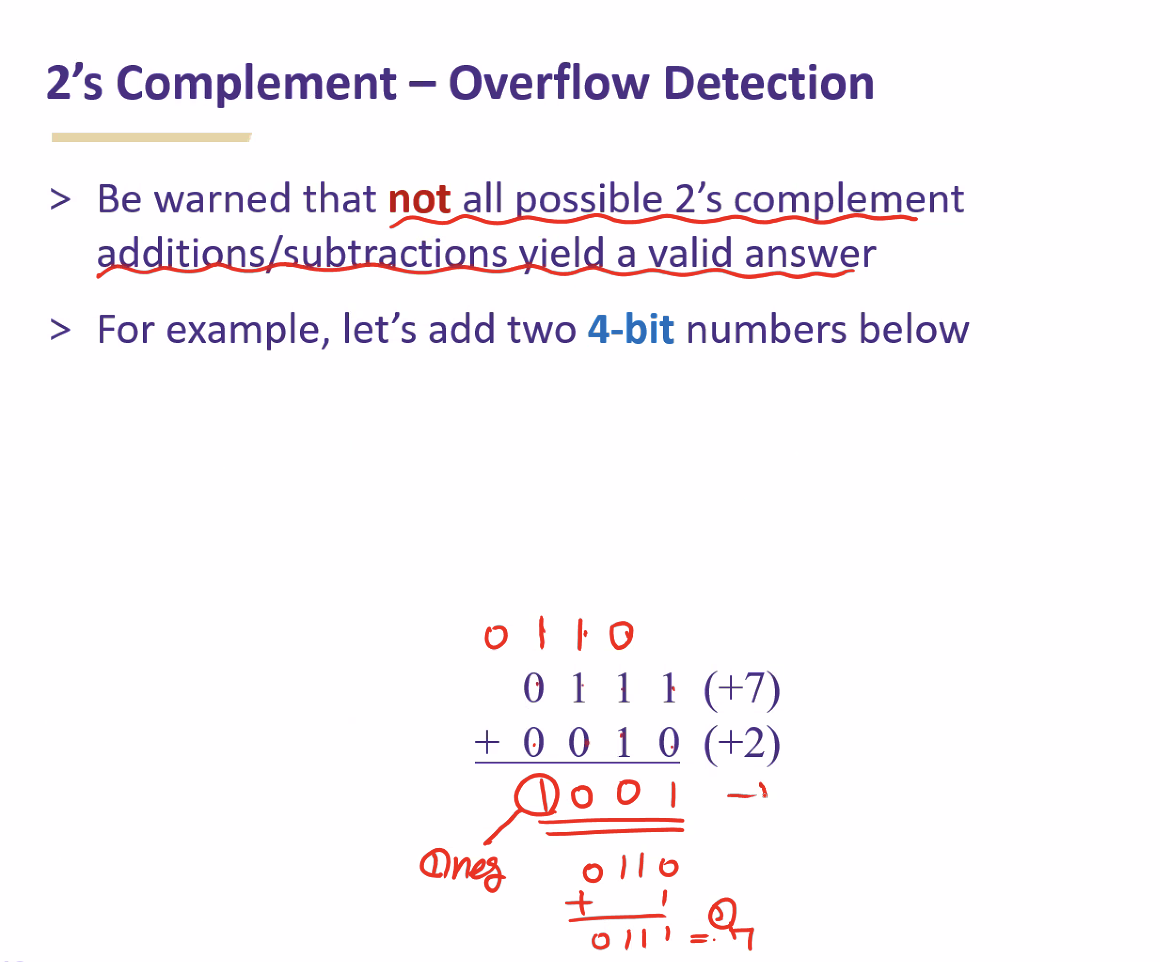

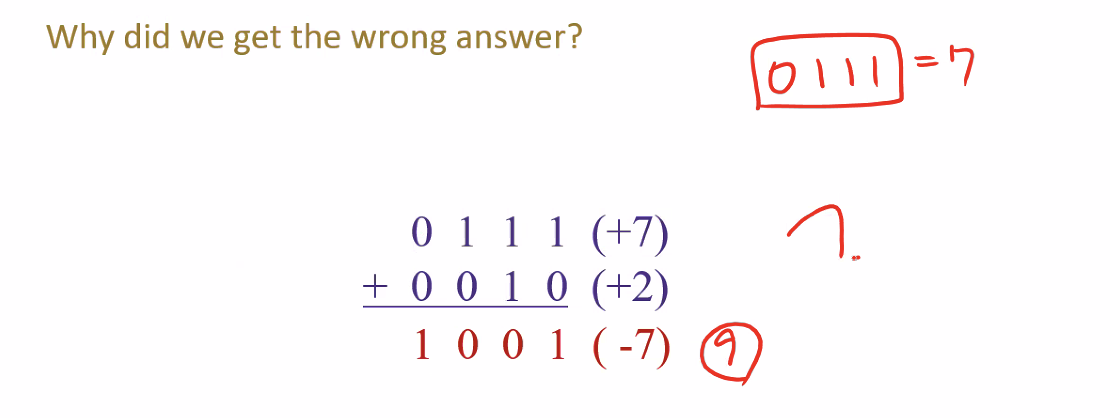

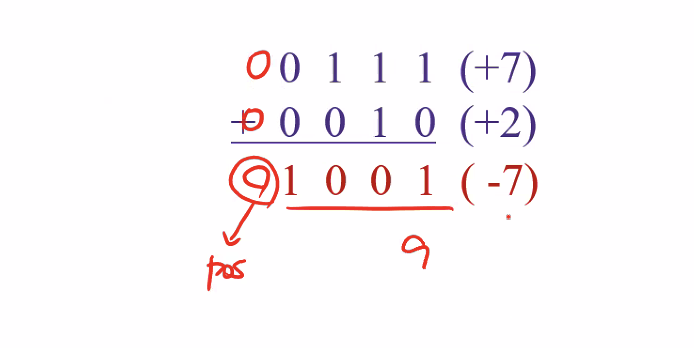

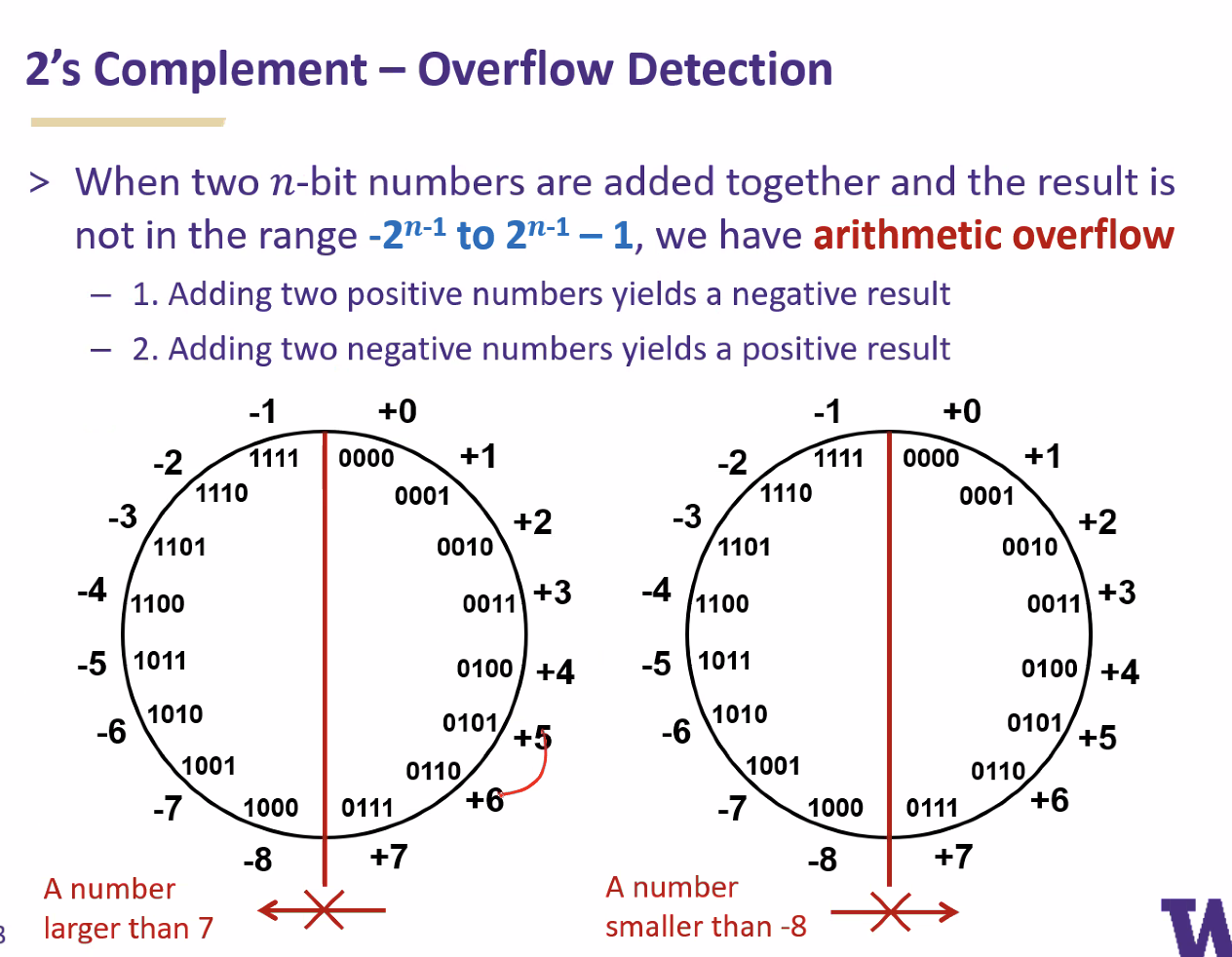

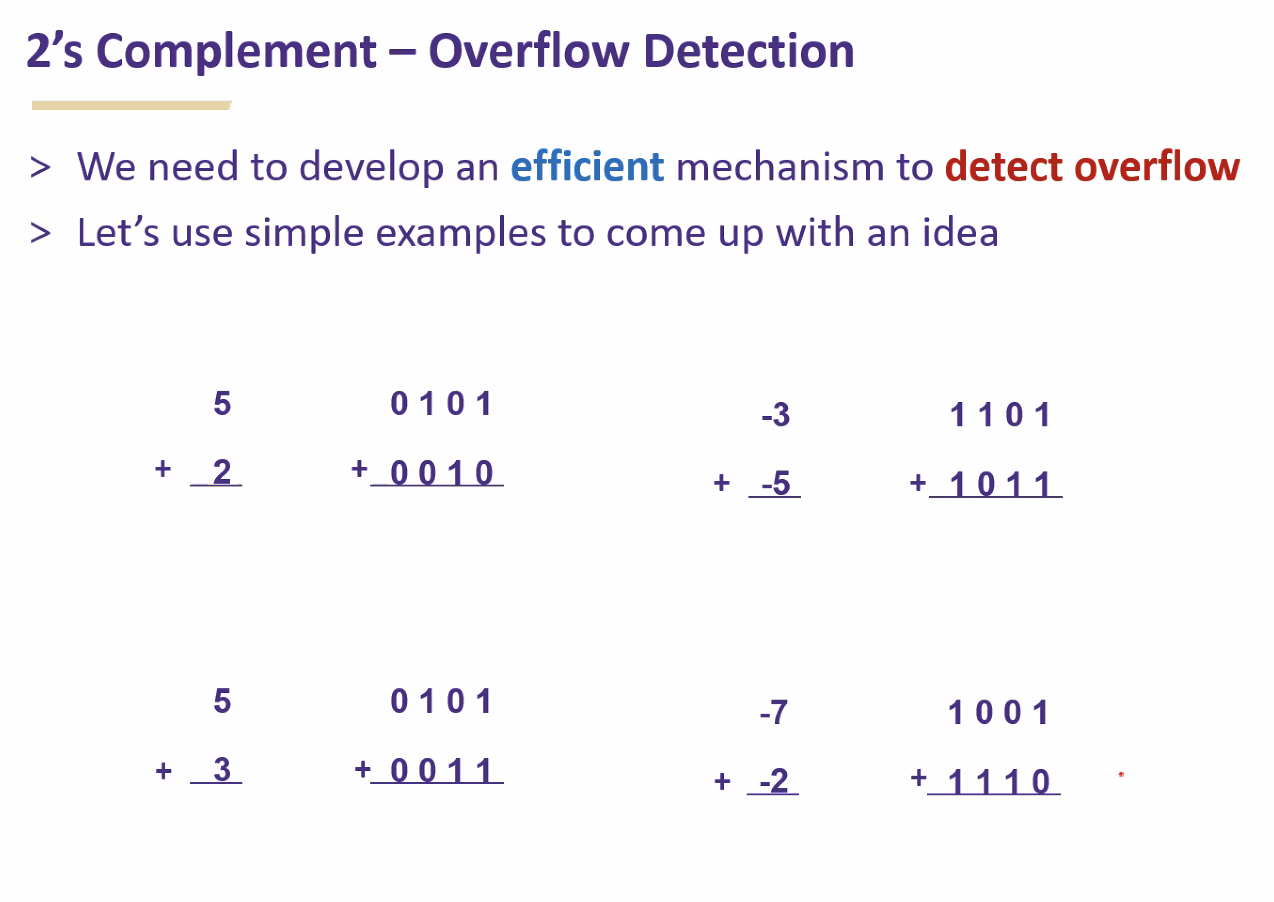

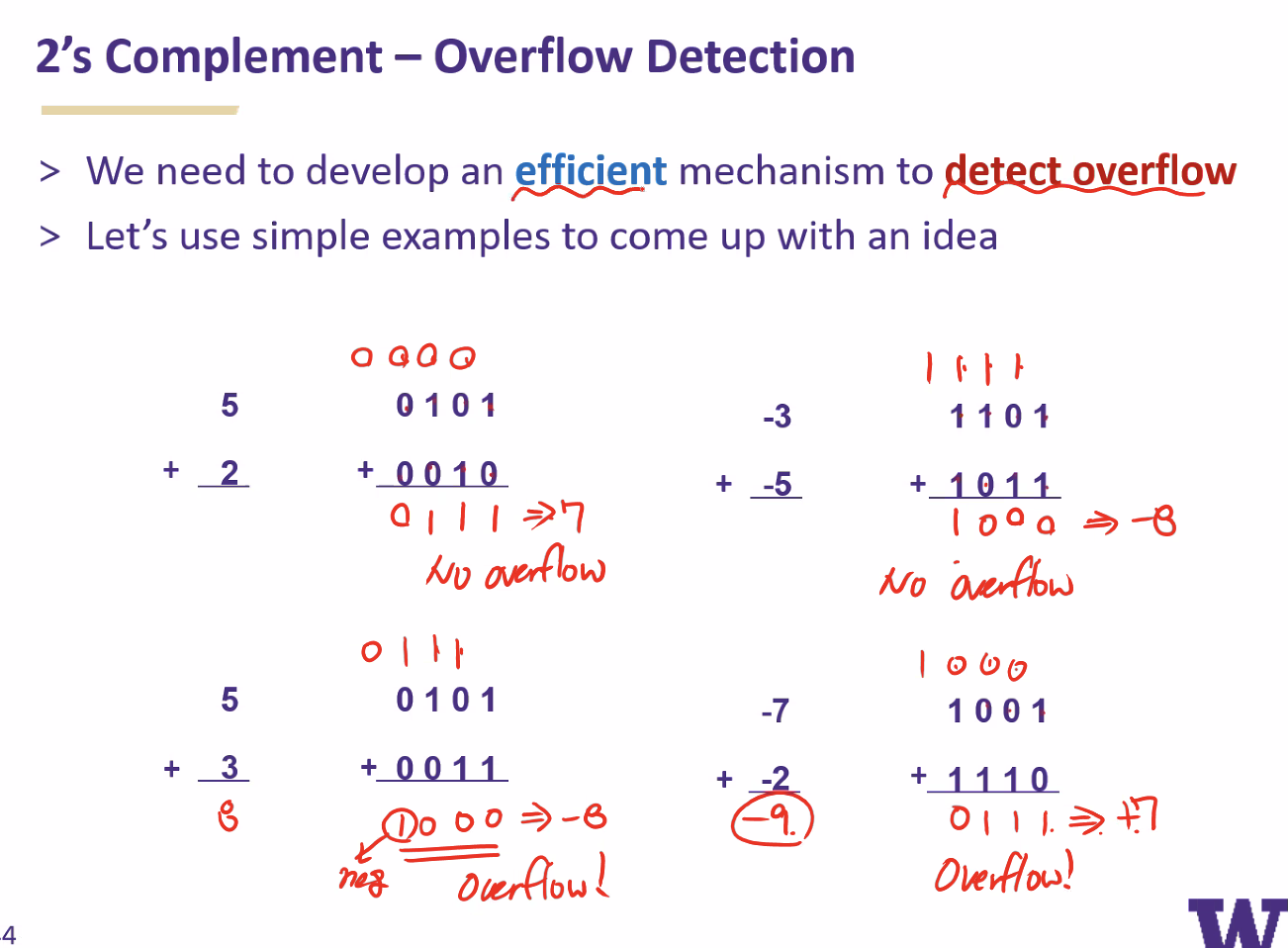

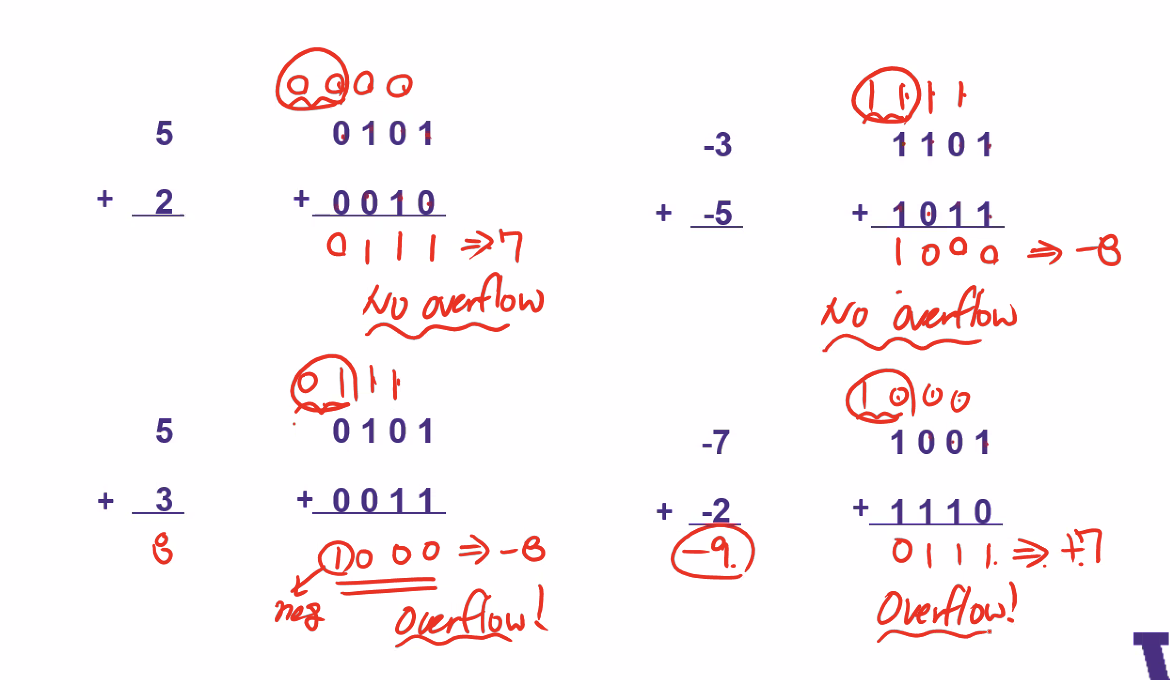

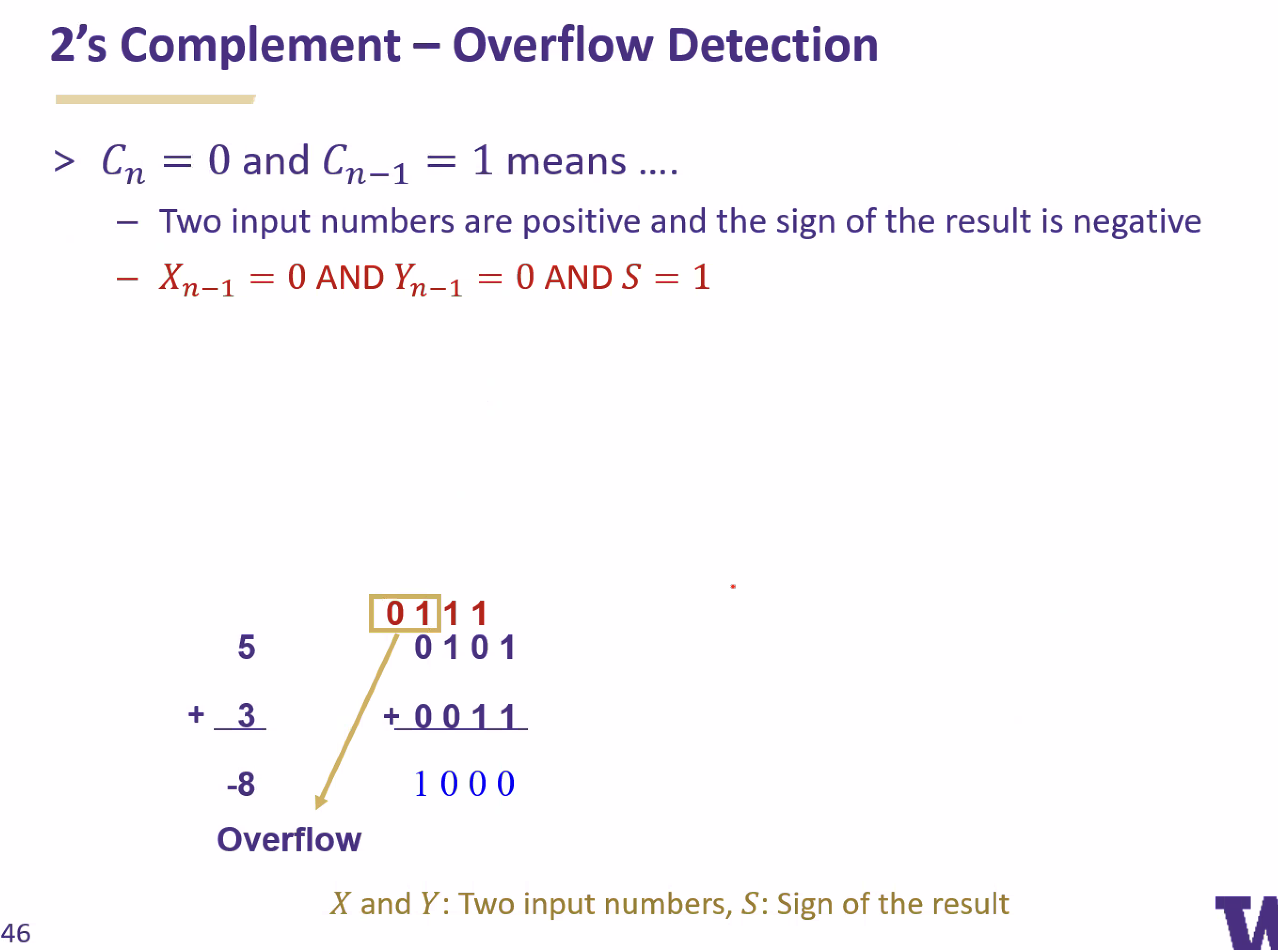

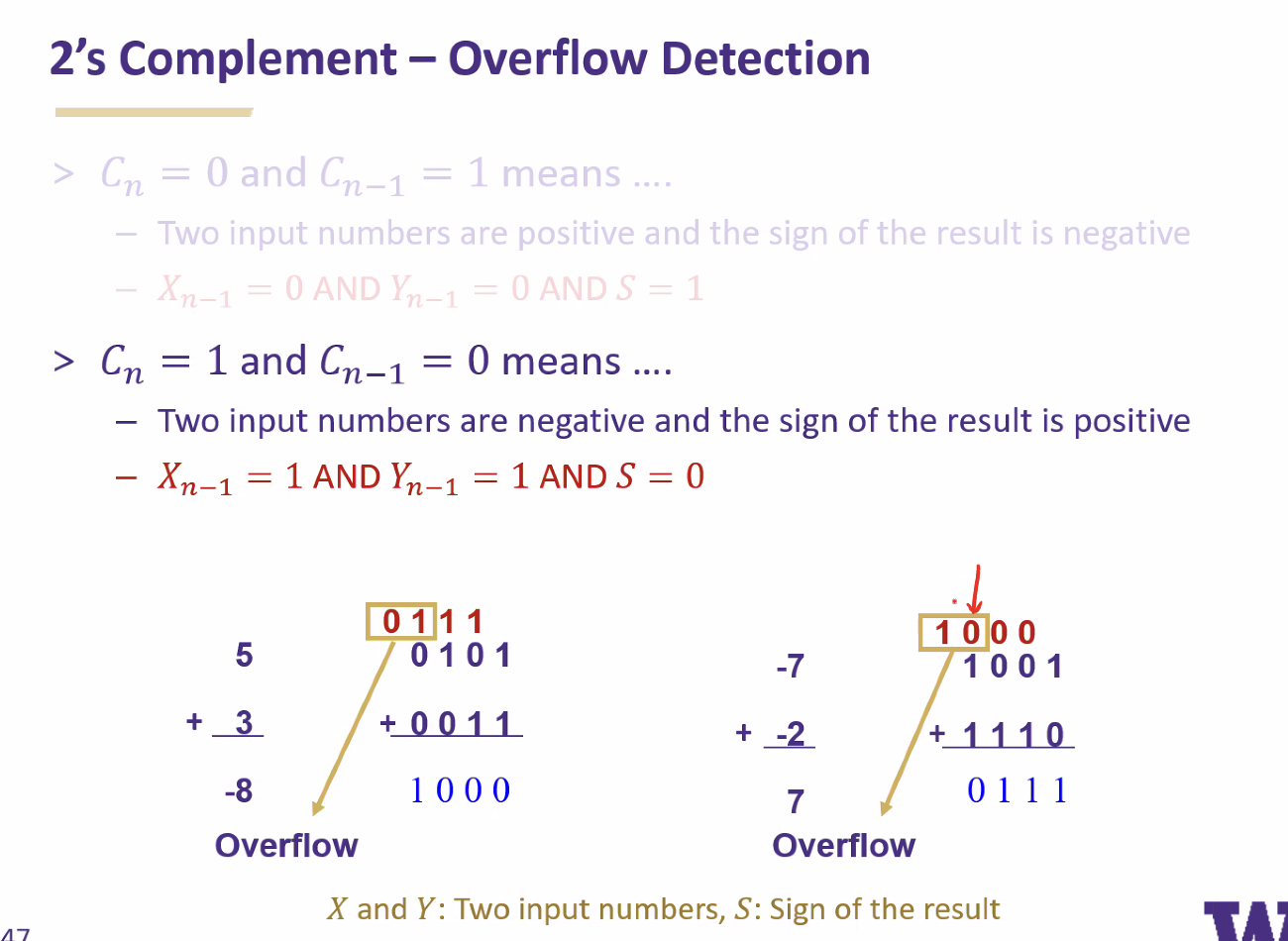

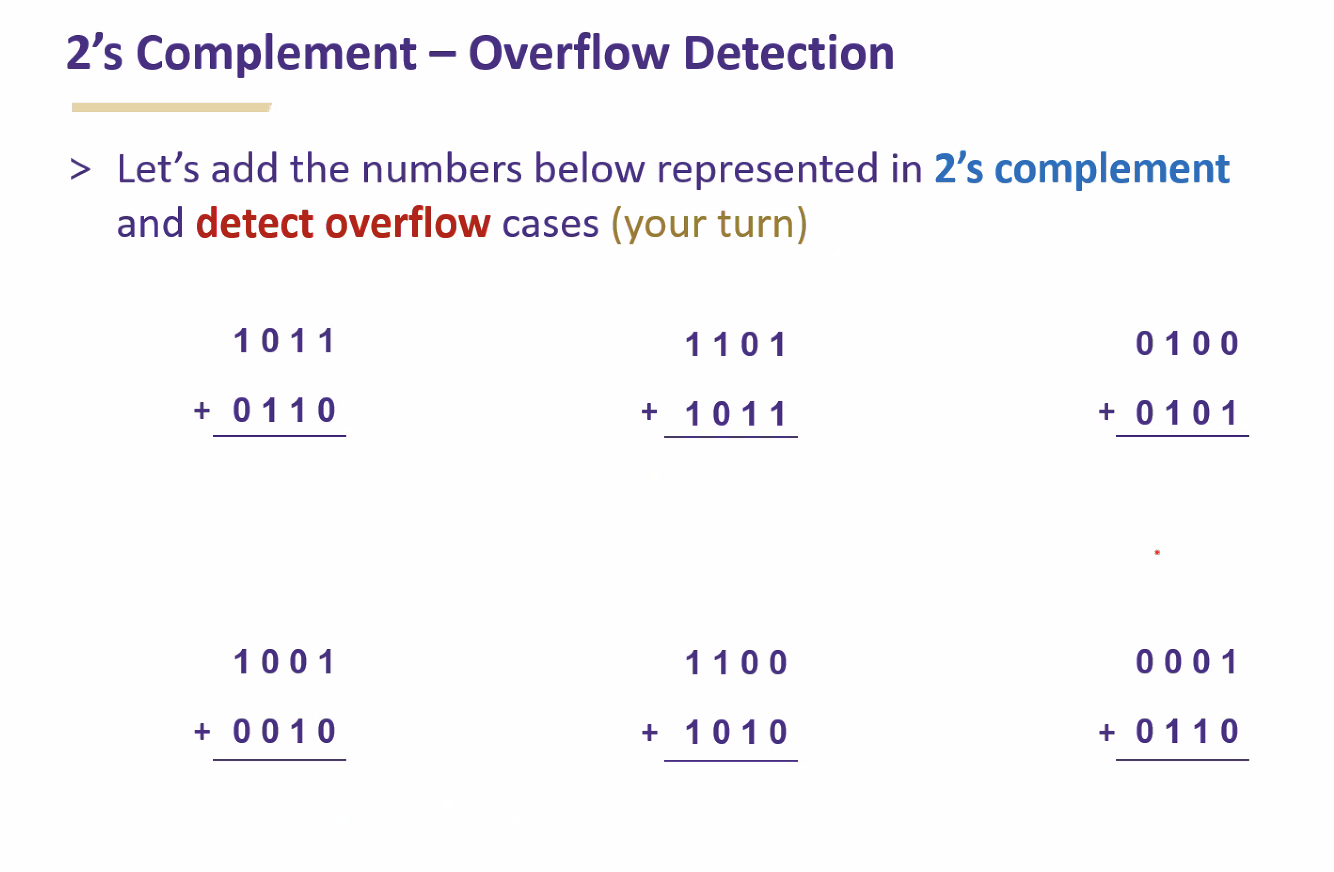

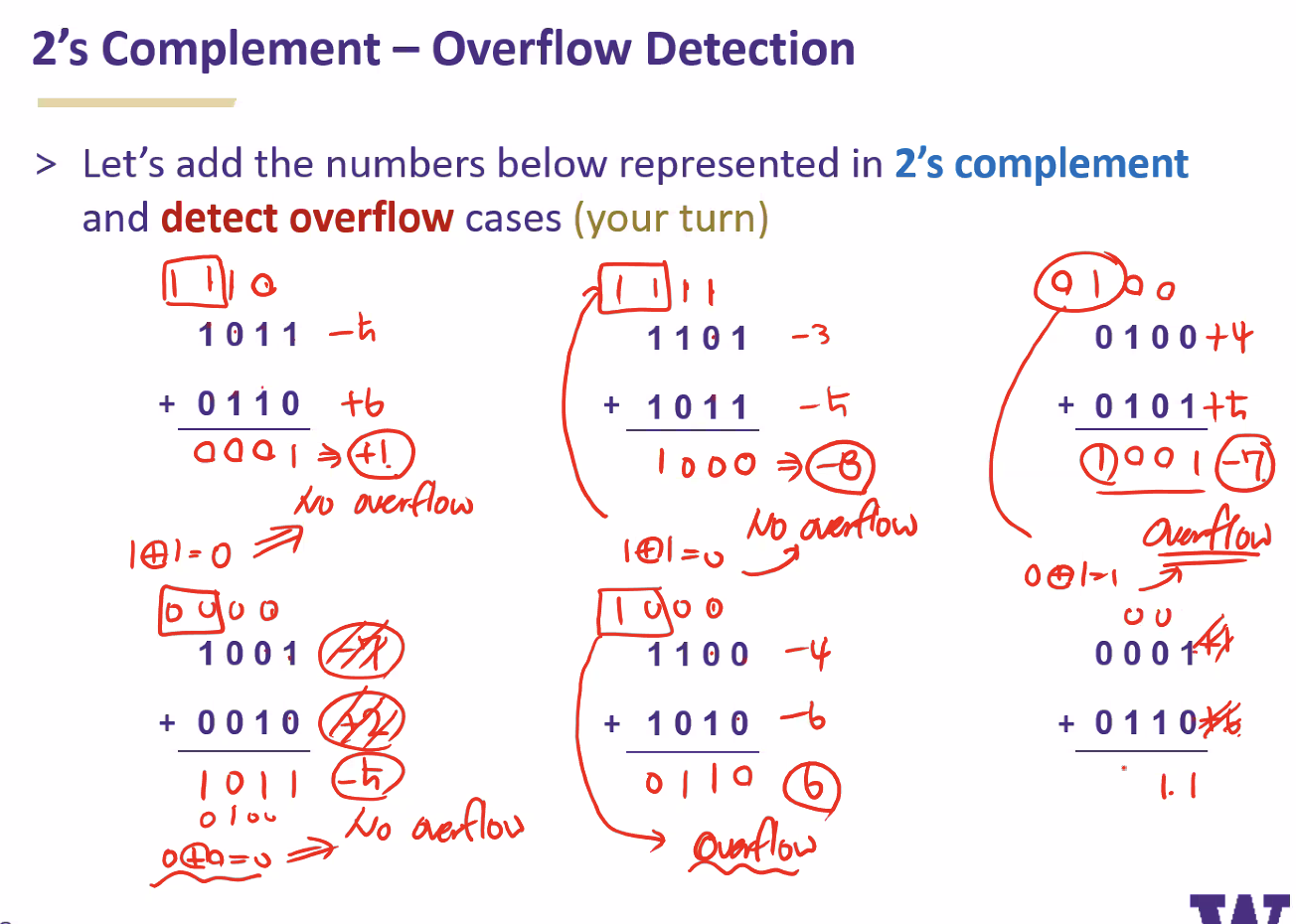

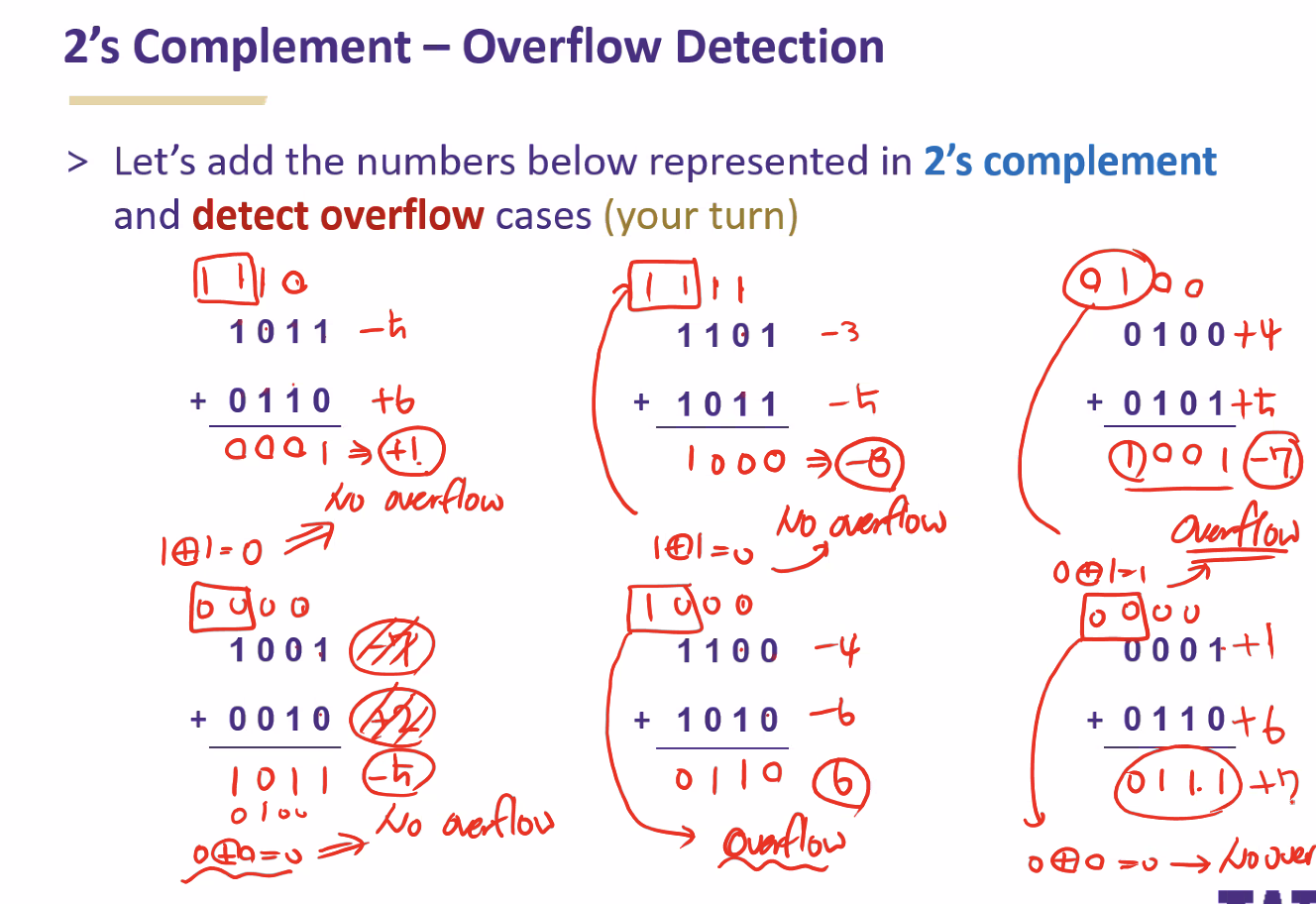

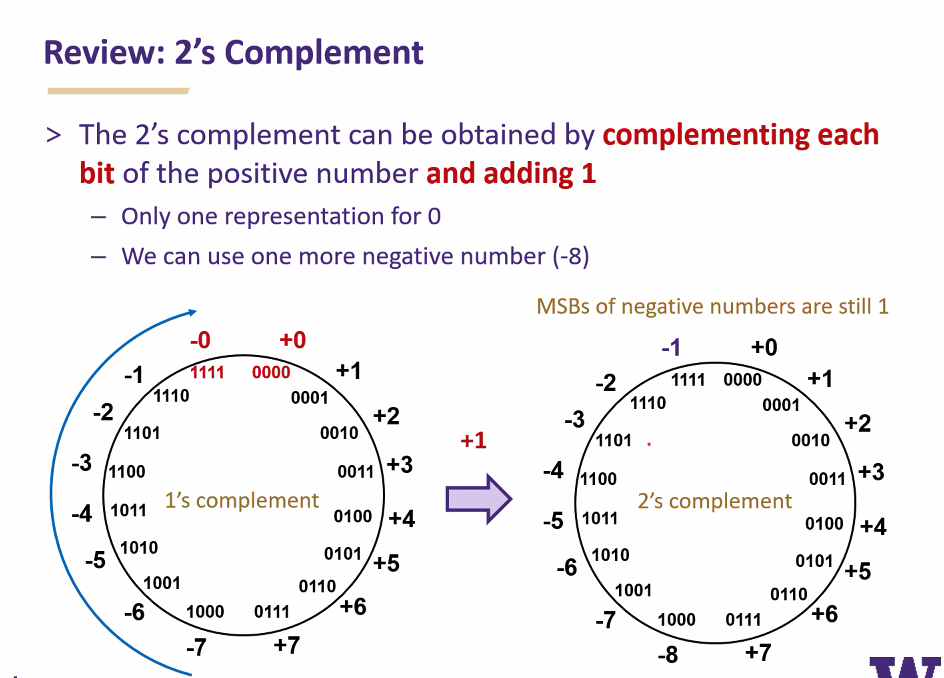

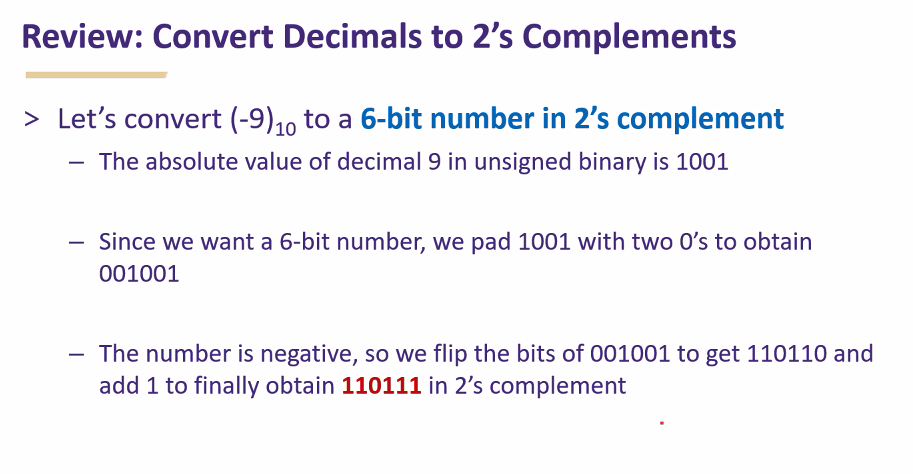

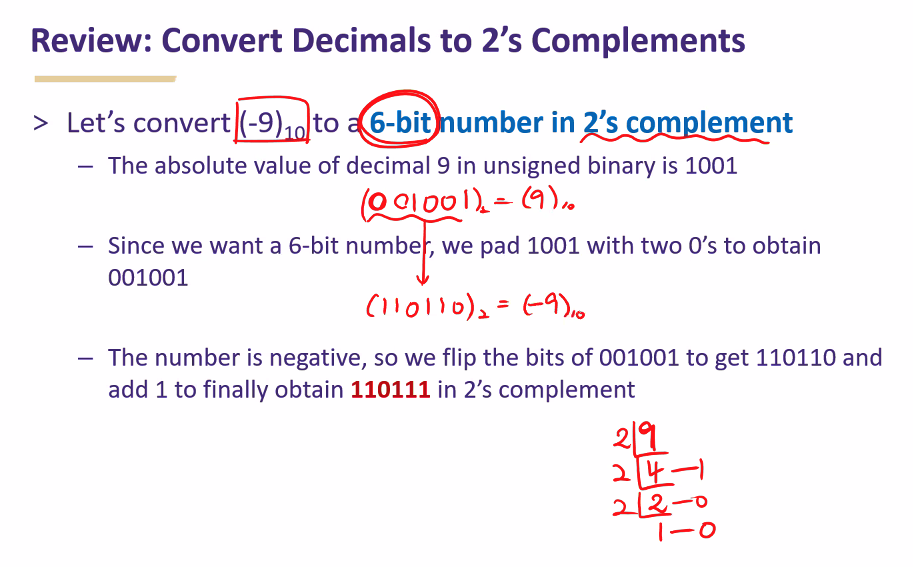

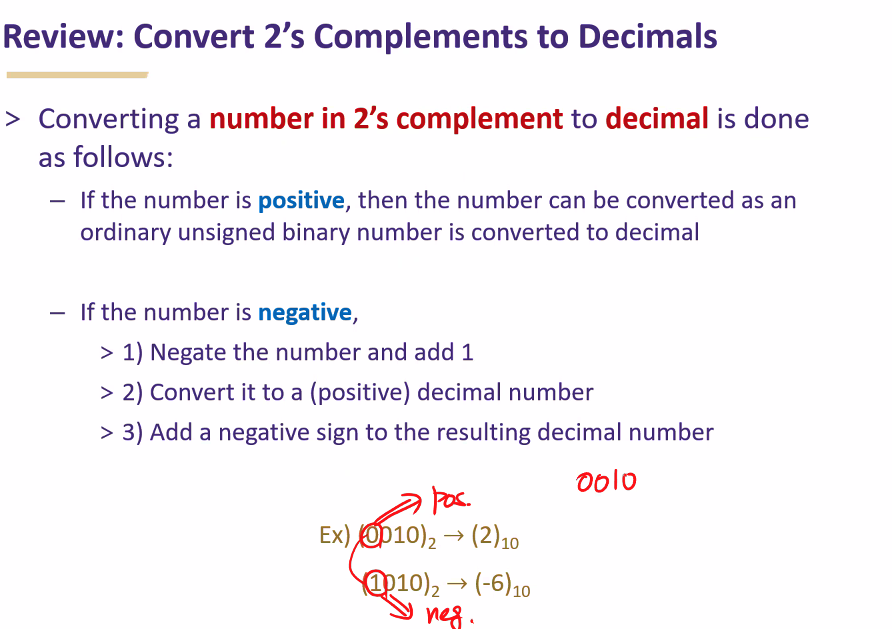

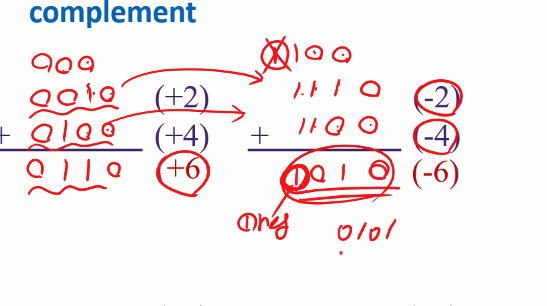

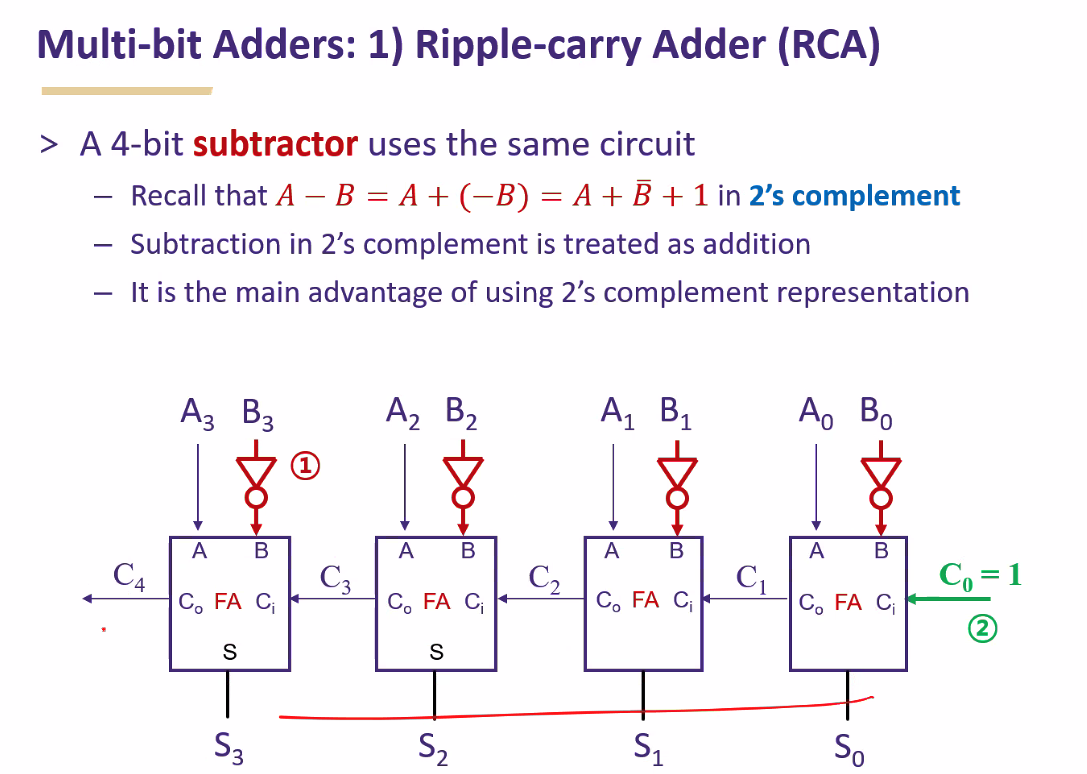

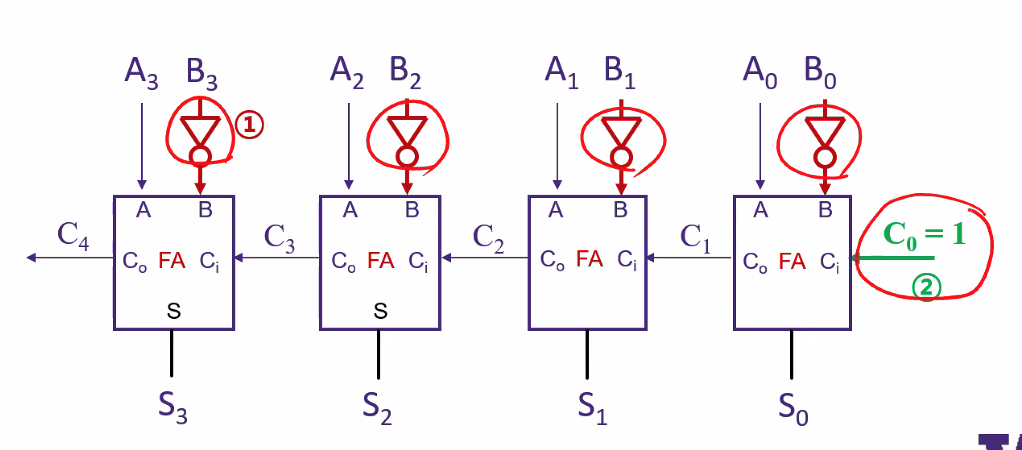

add 1 to the 1's compliment number

Lecture 7

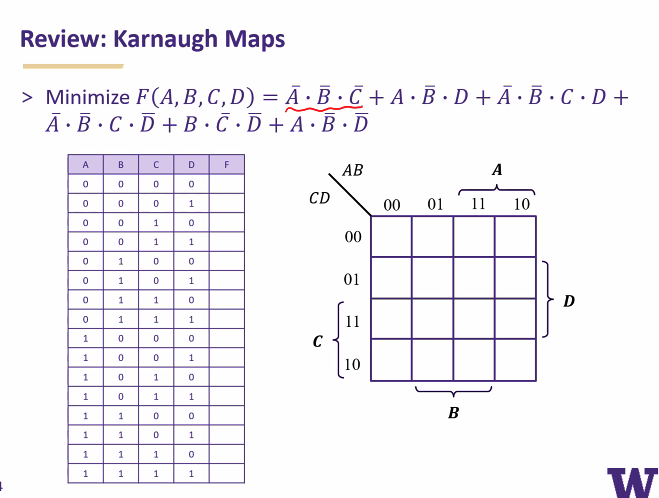

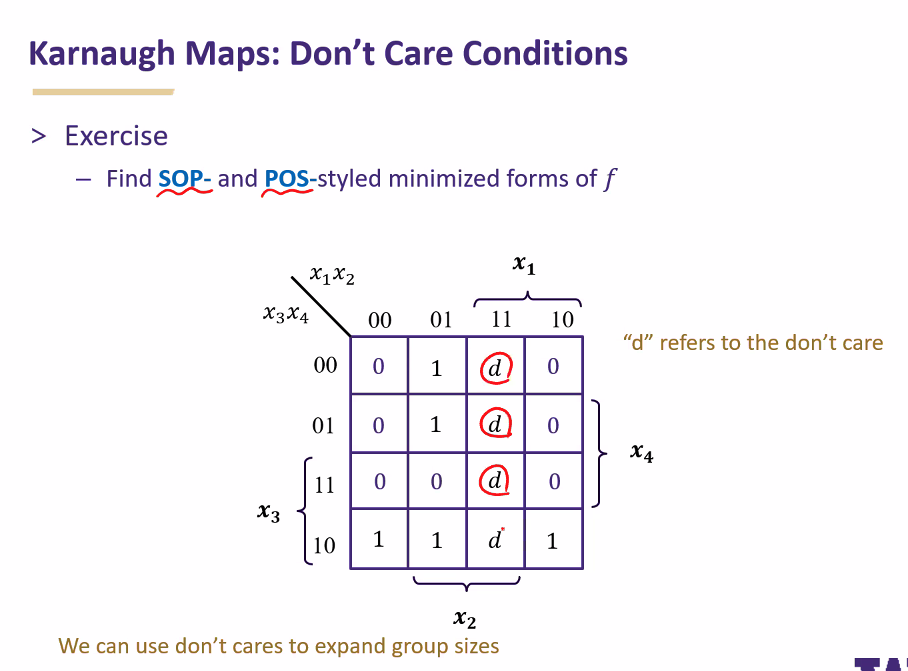

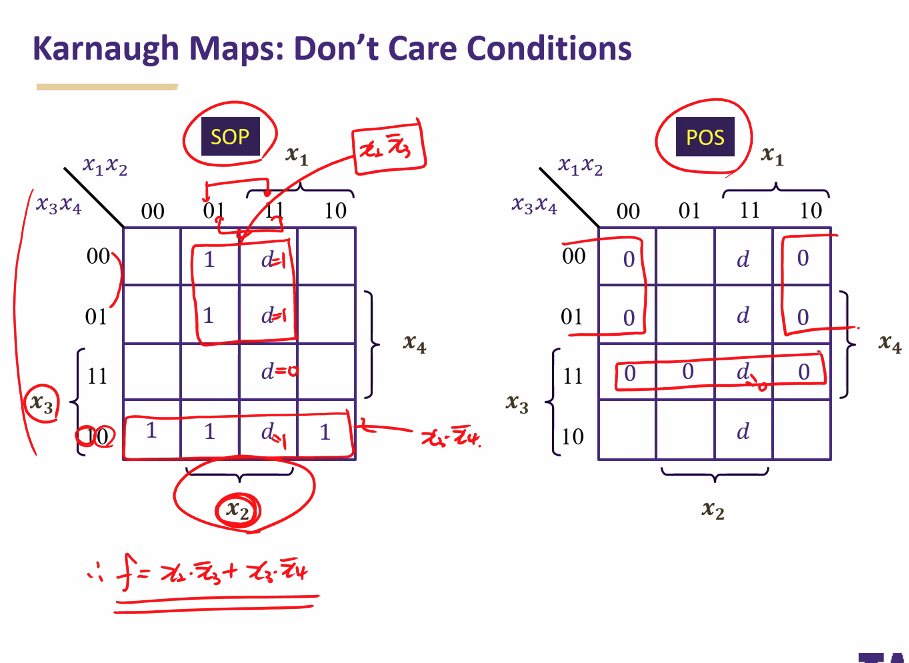

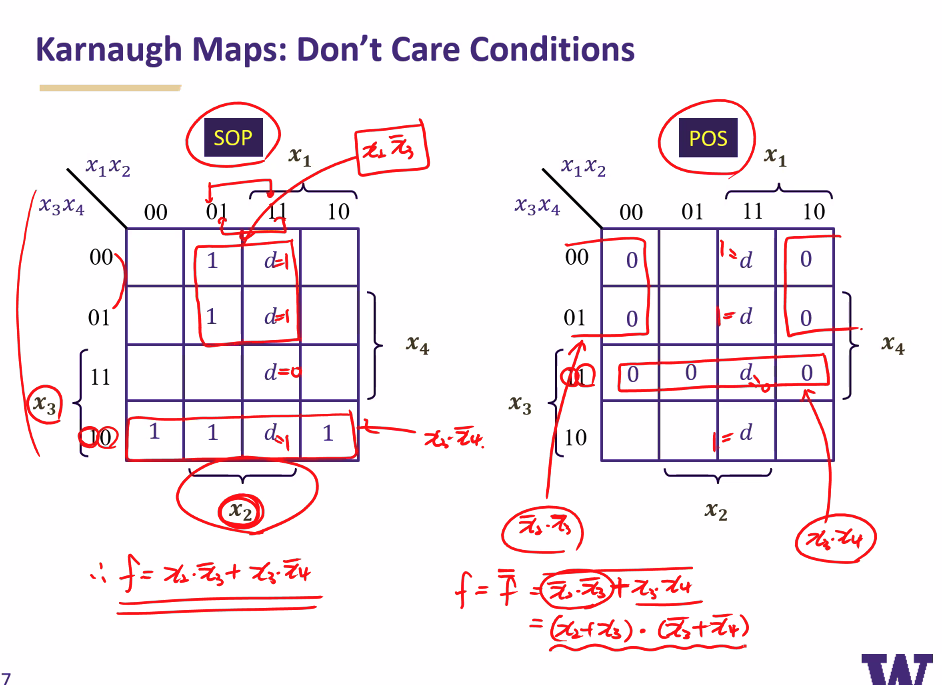

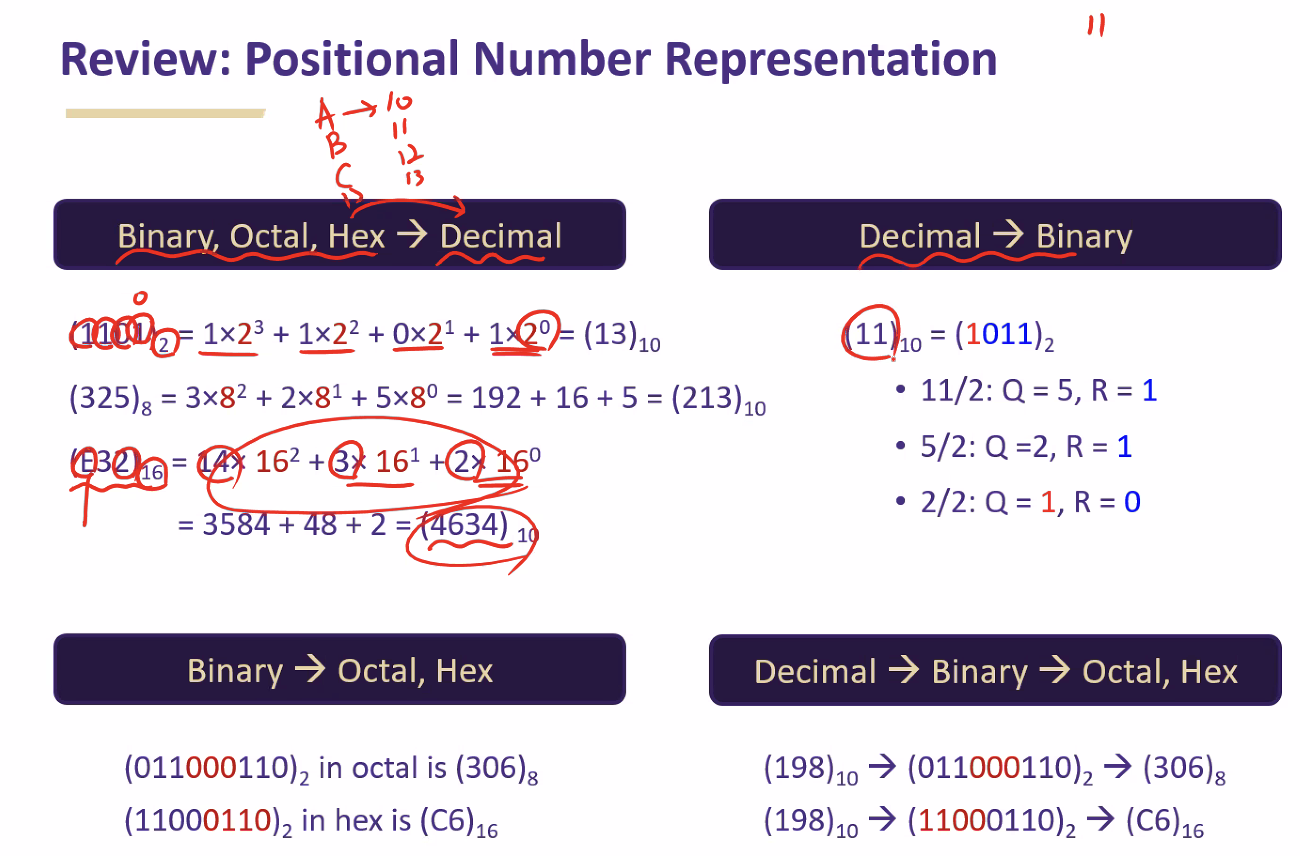

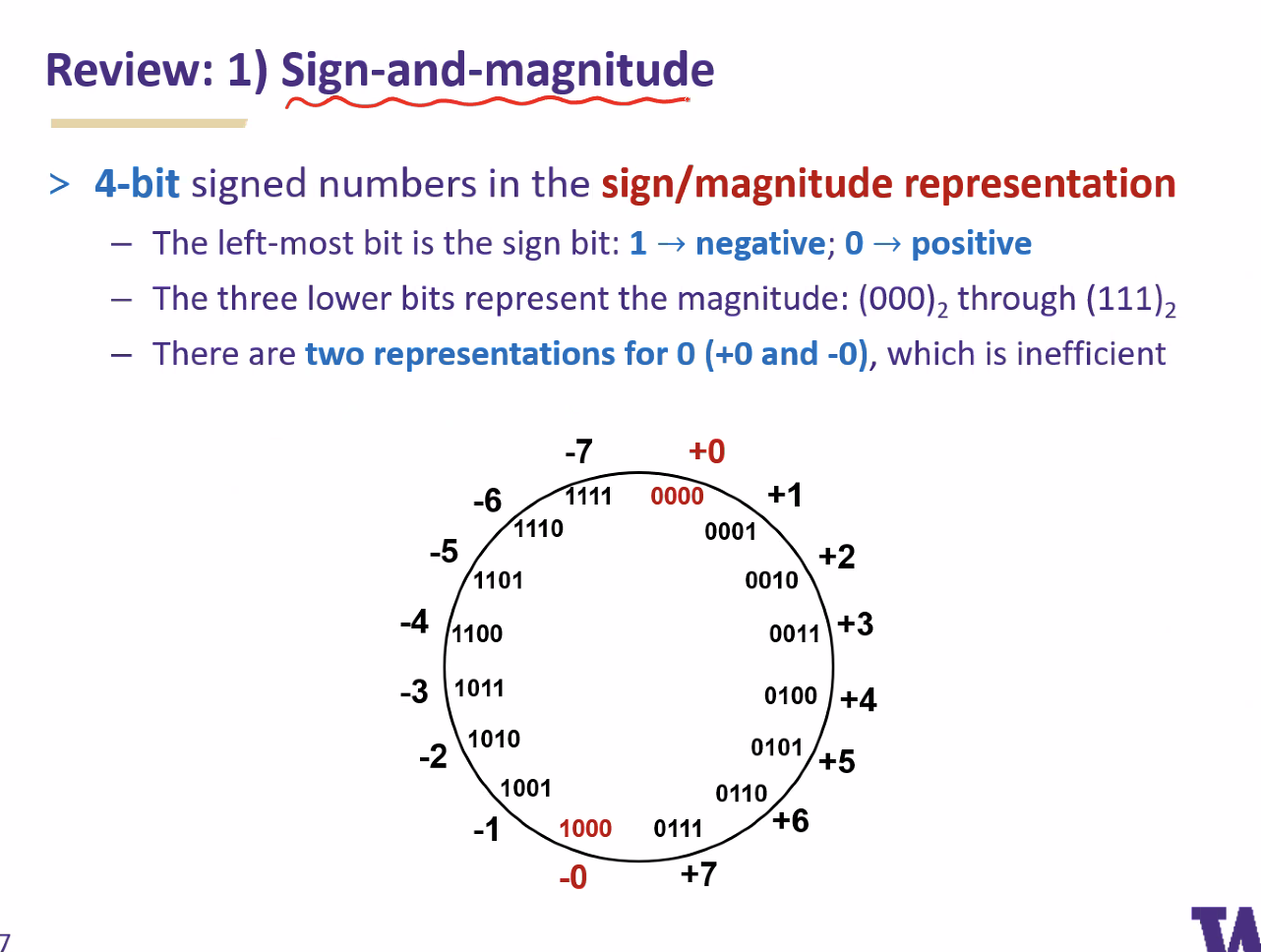

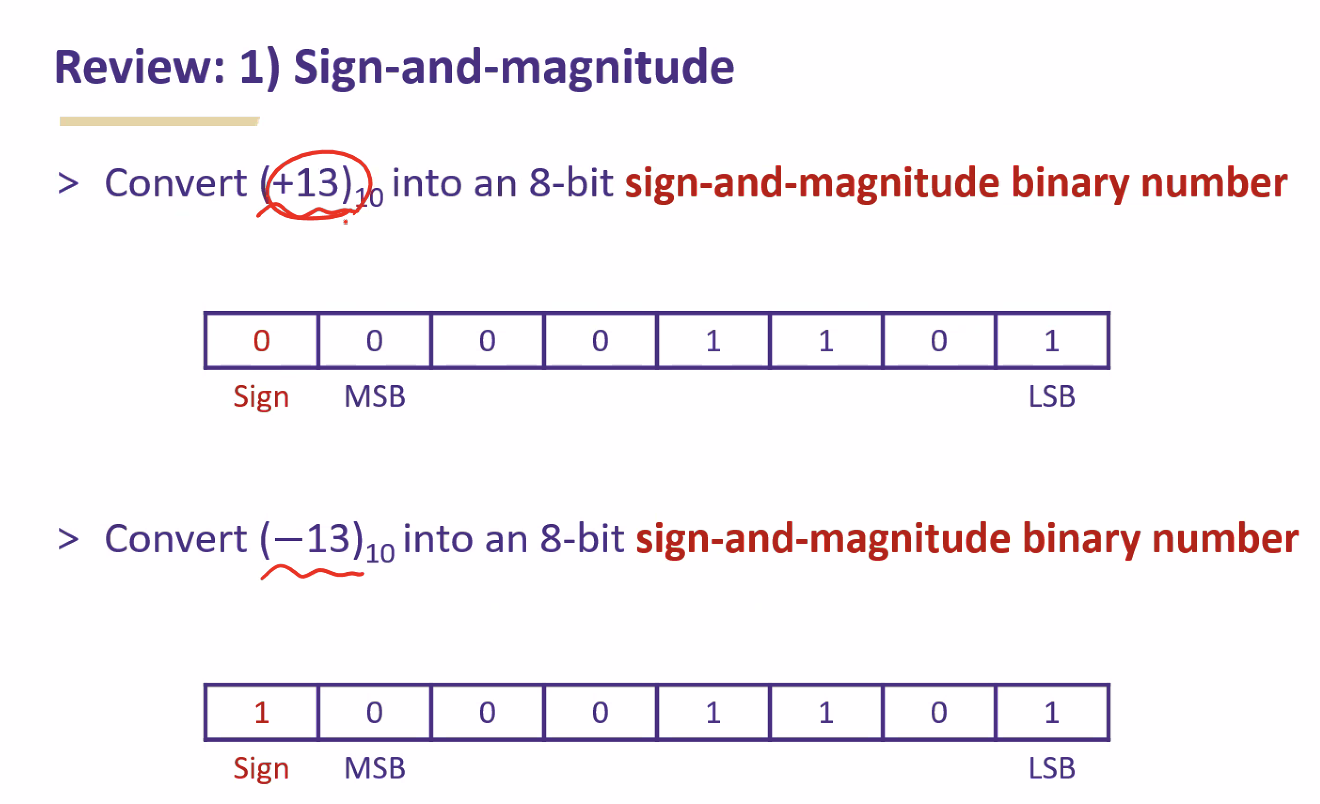

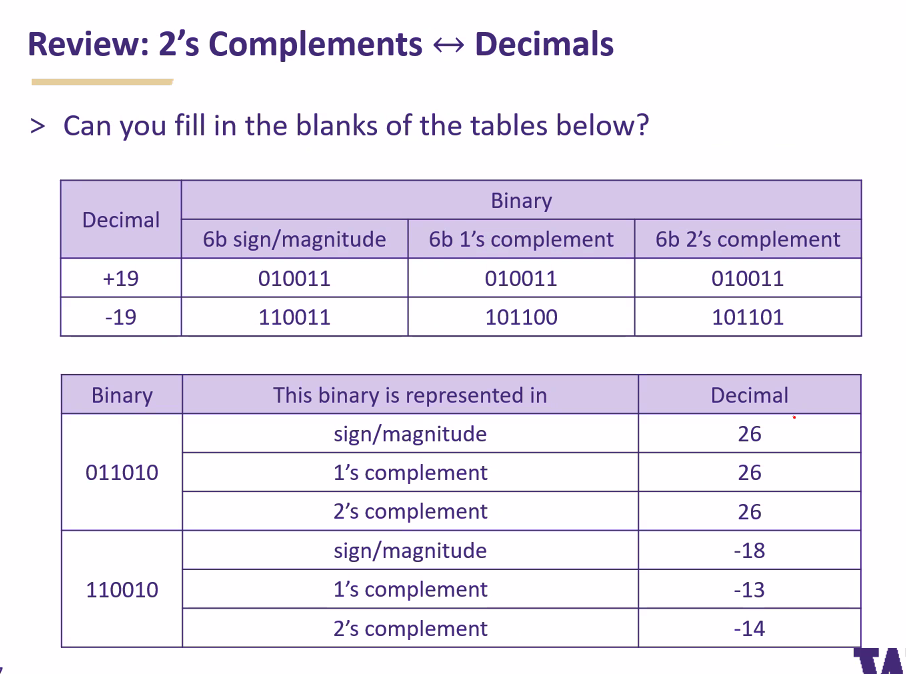

Review

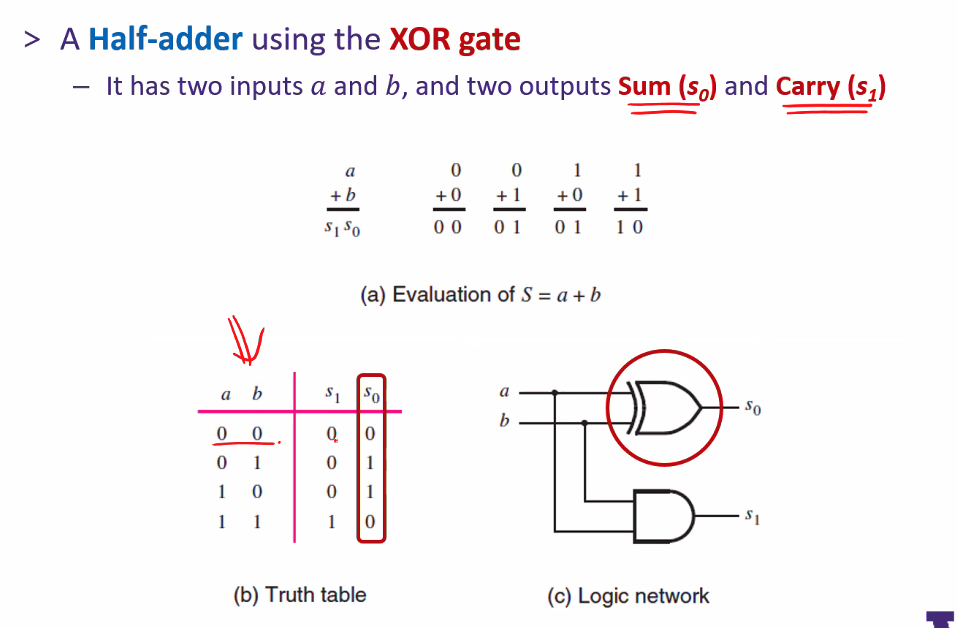

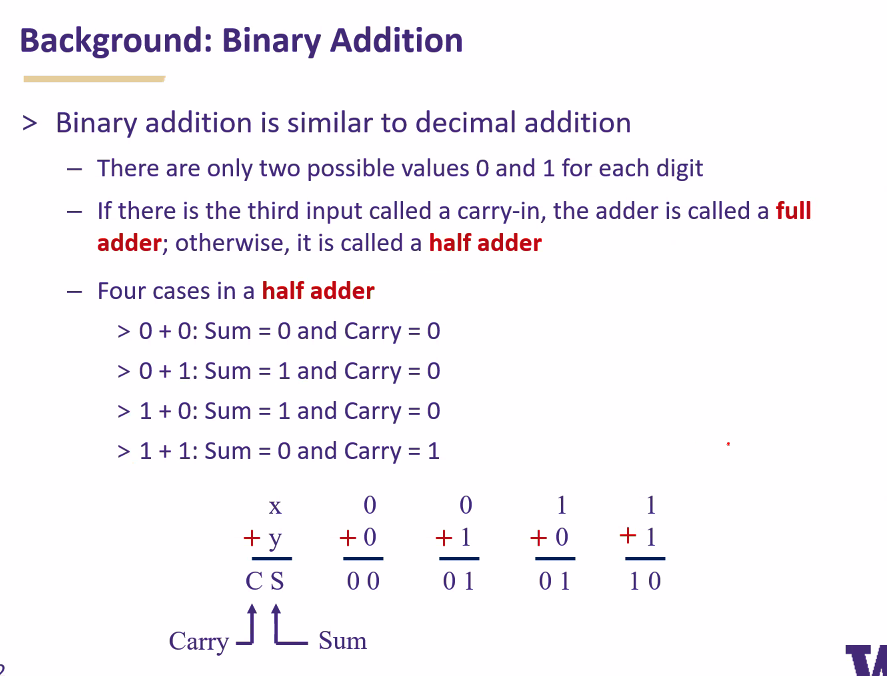

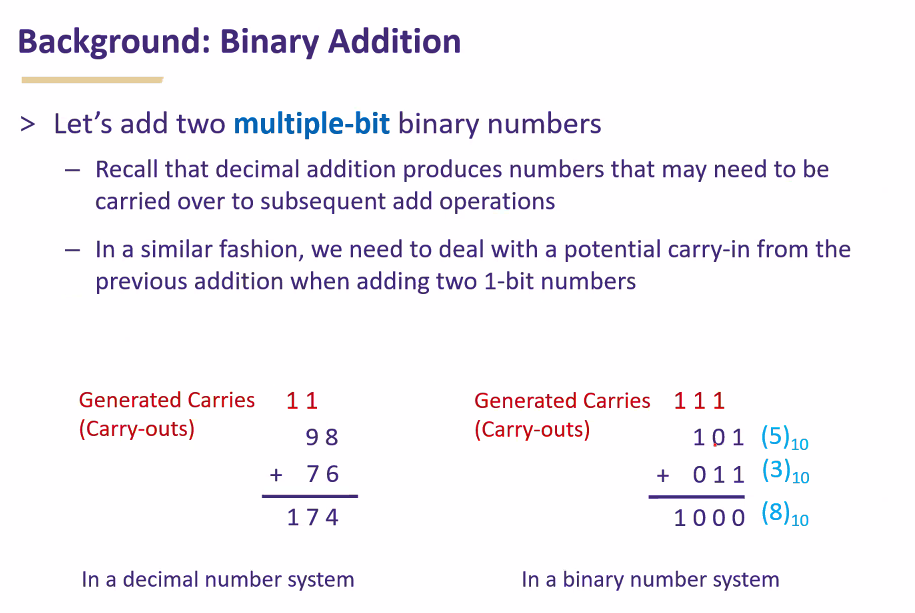

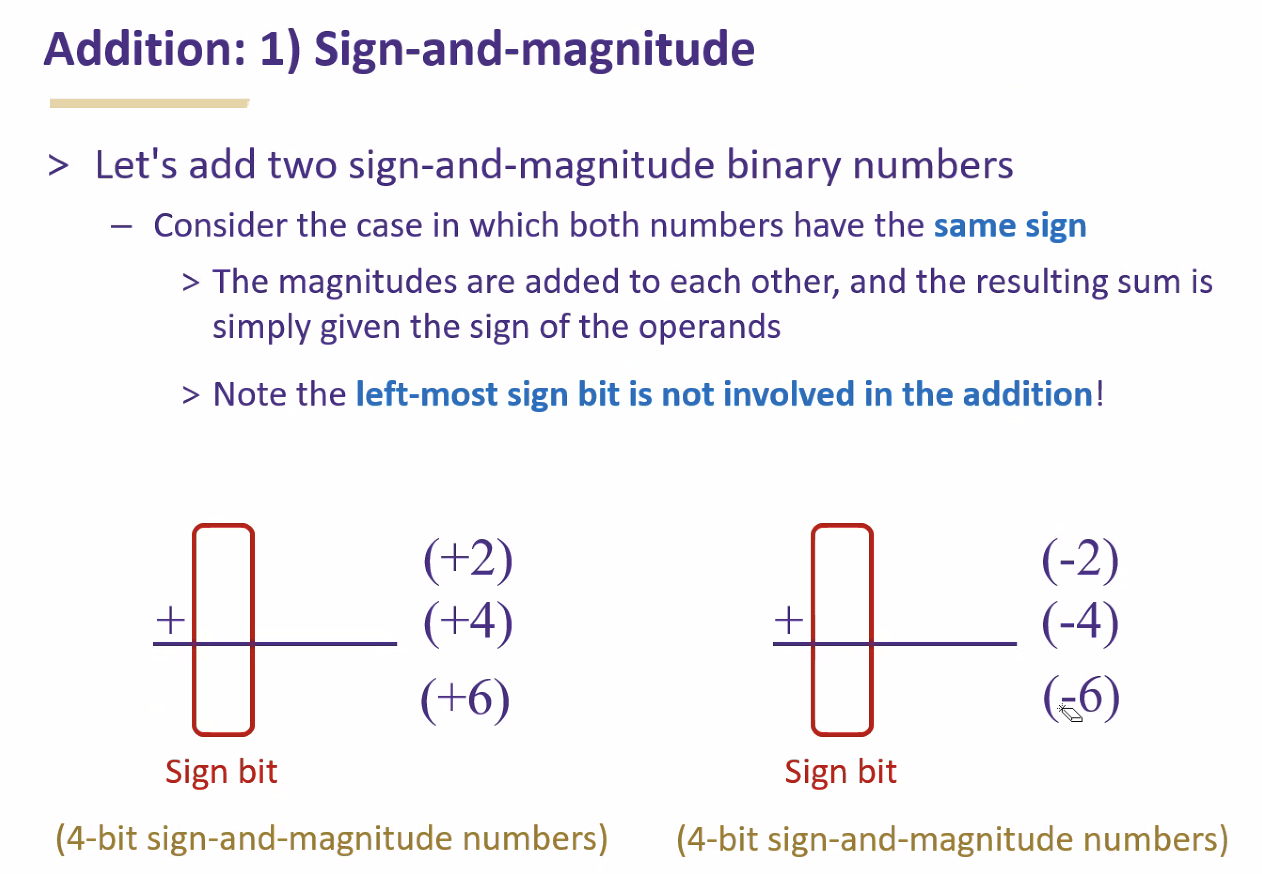

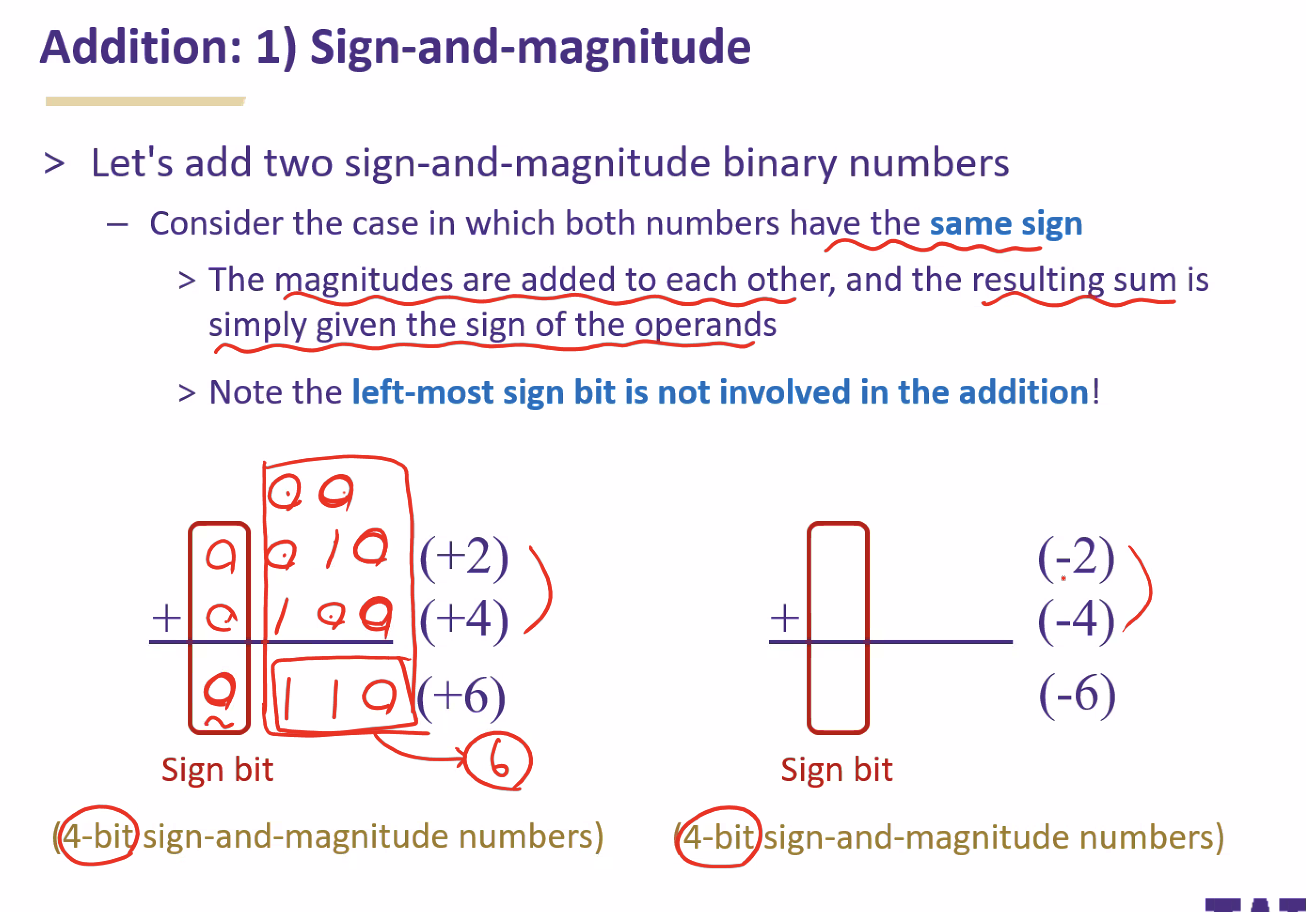

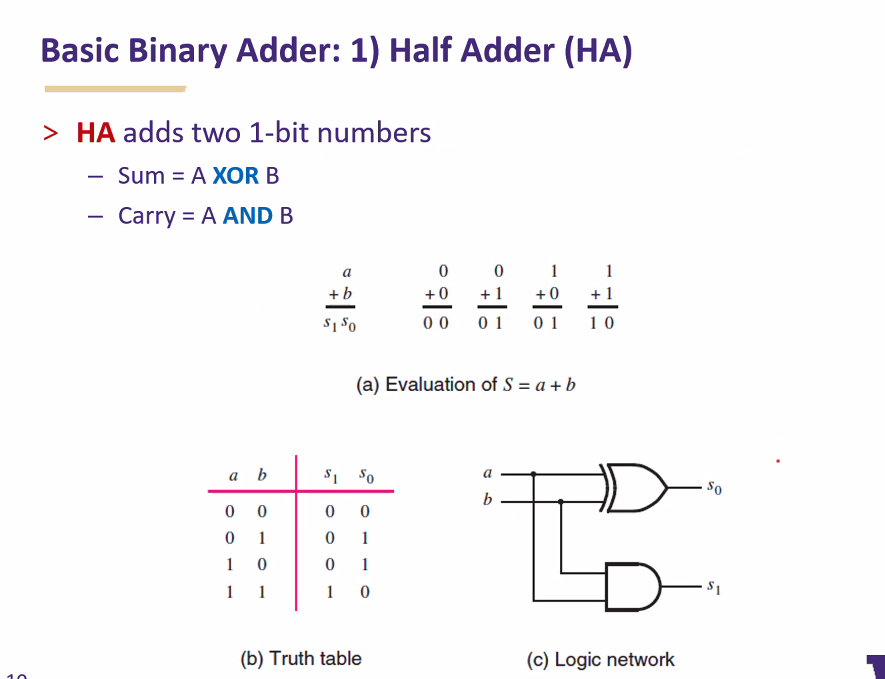

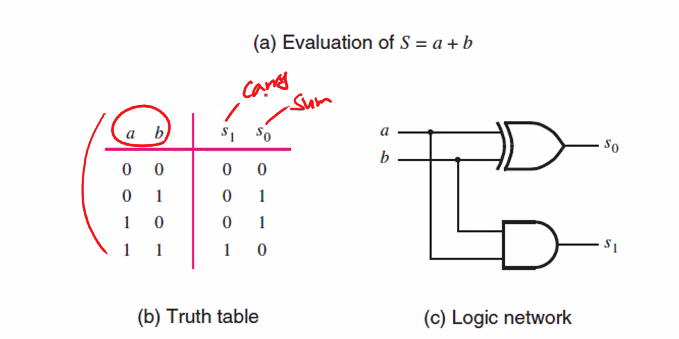

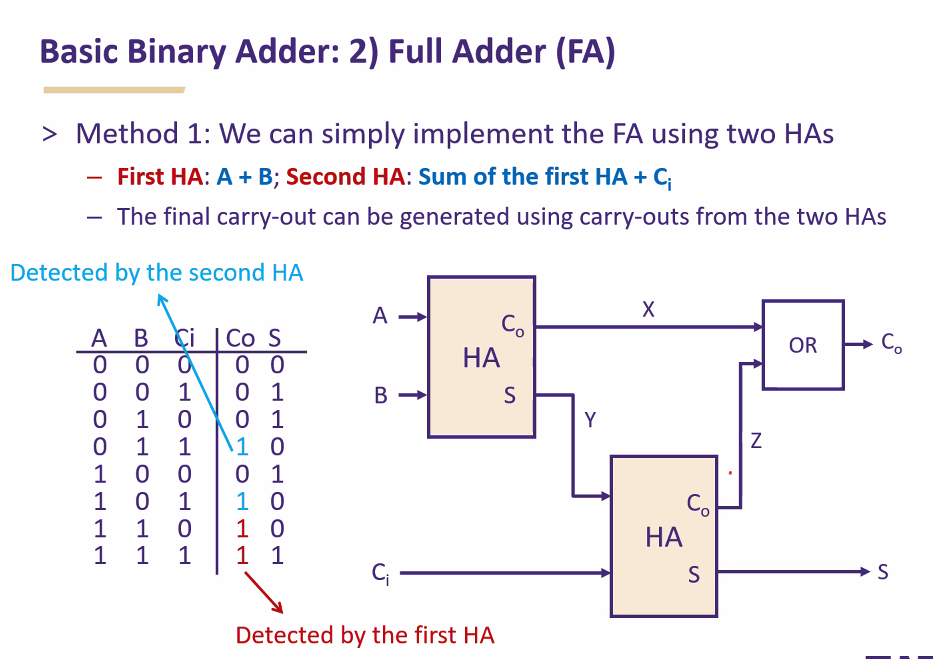

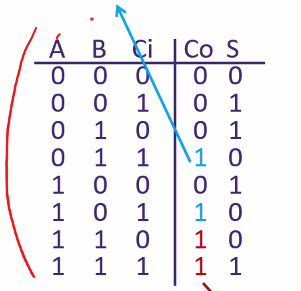

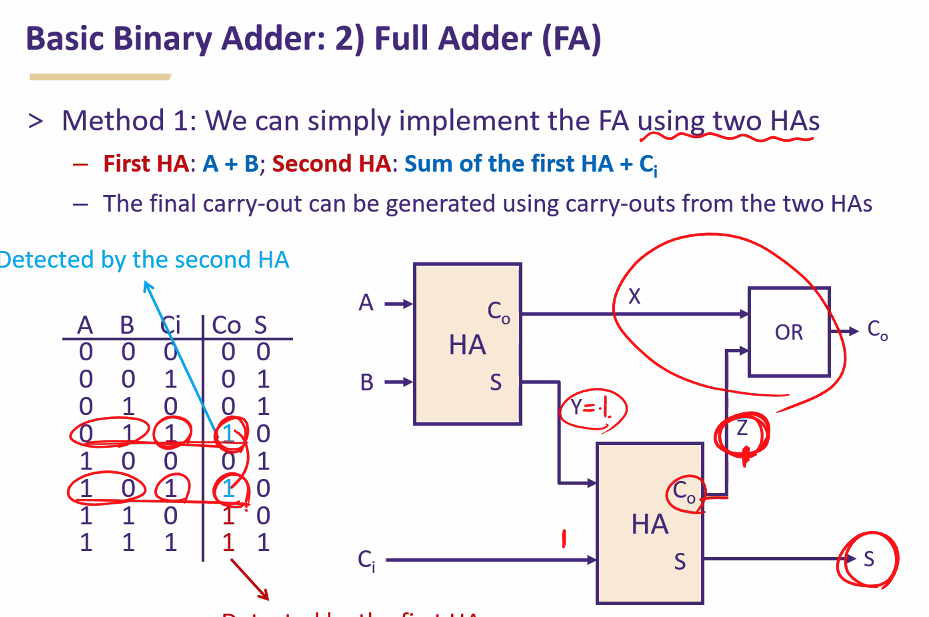

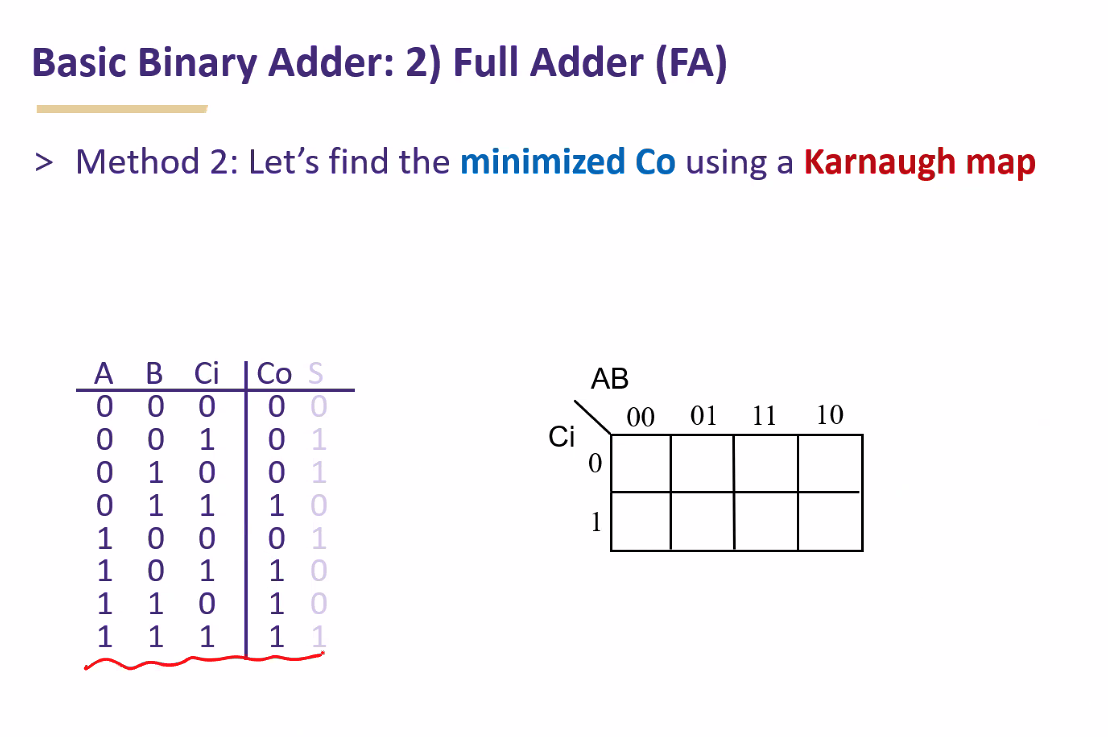

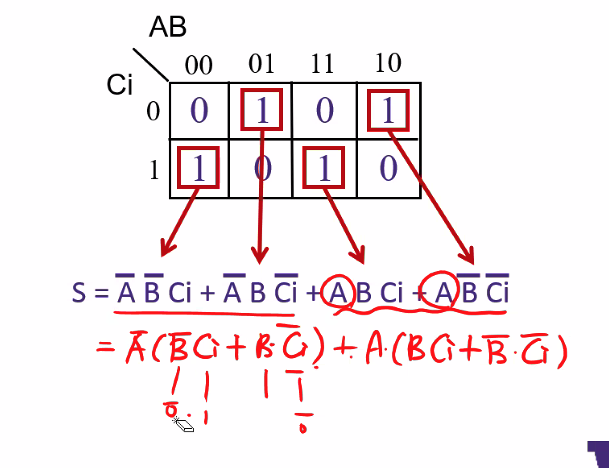

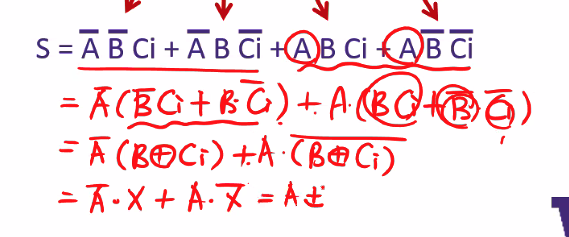

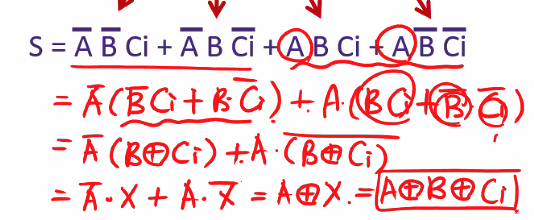

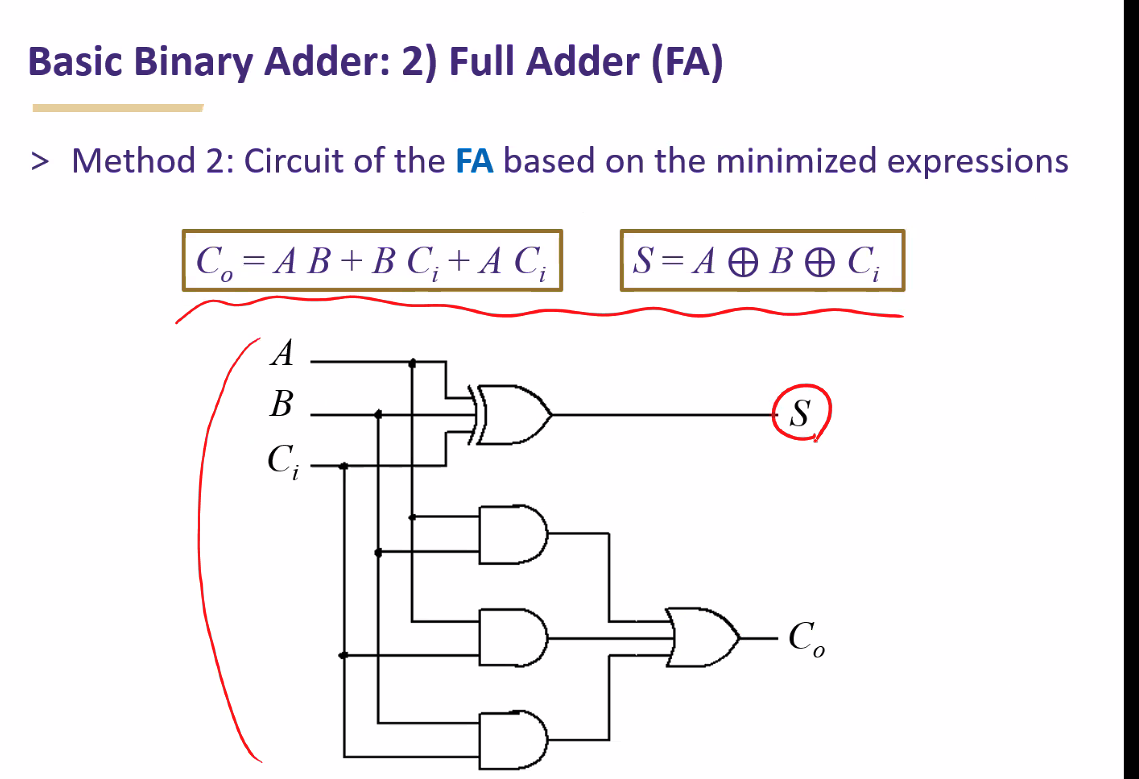

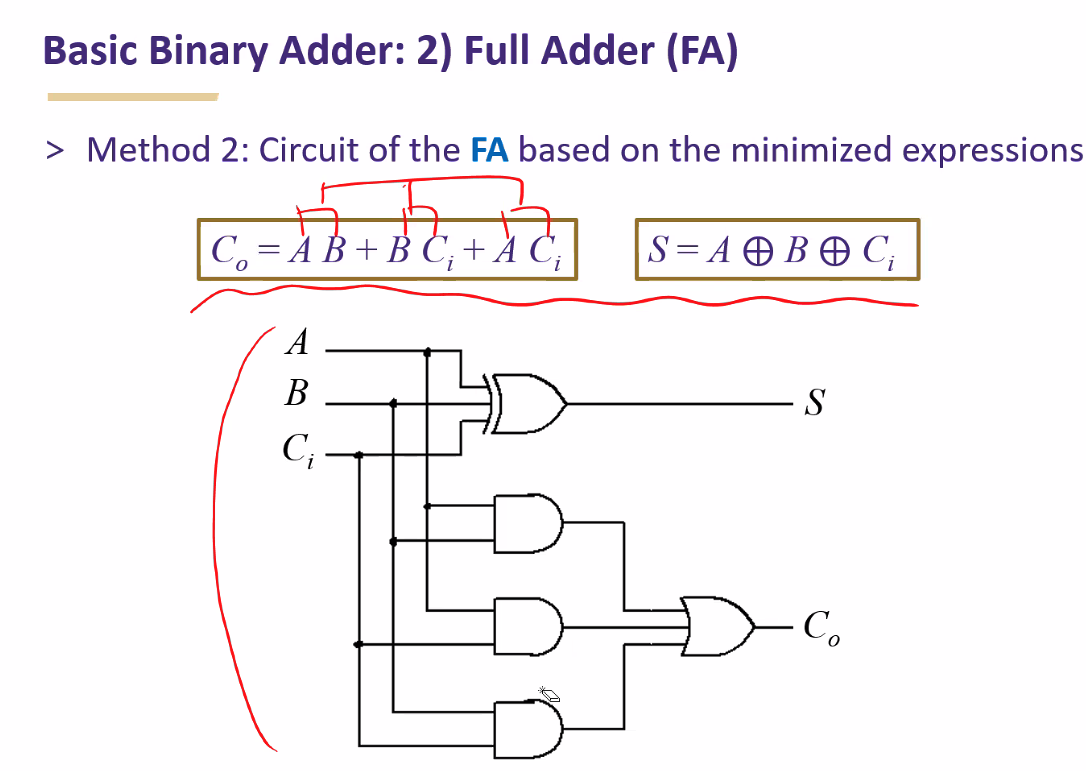

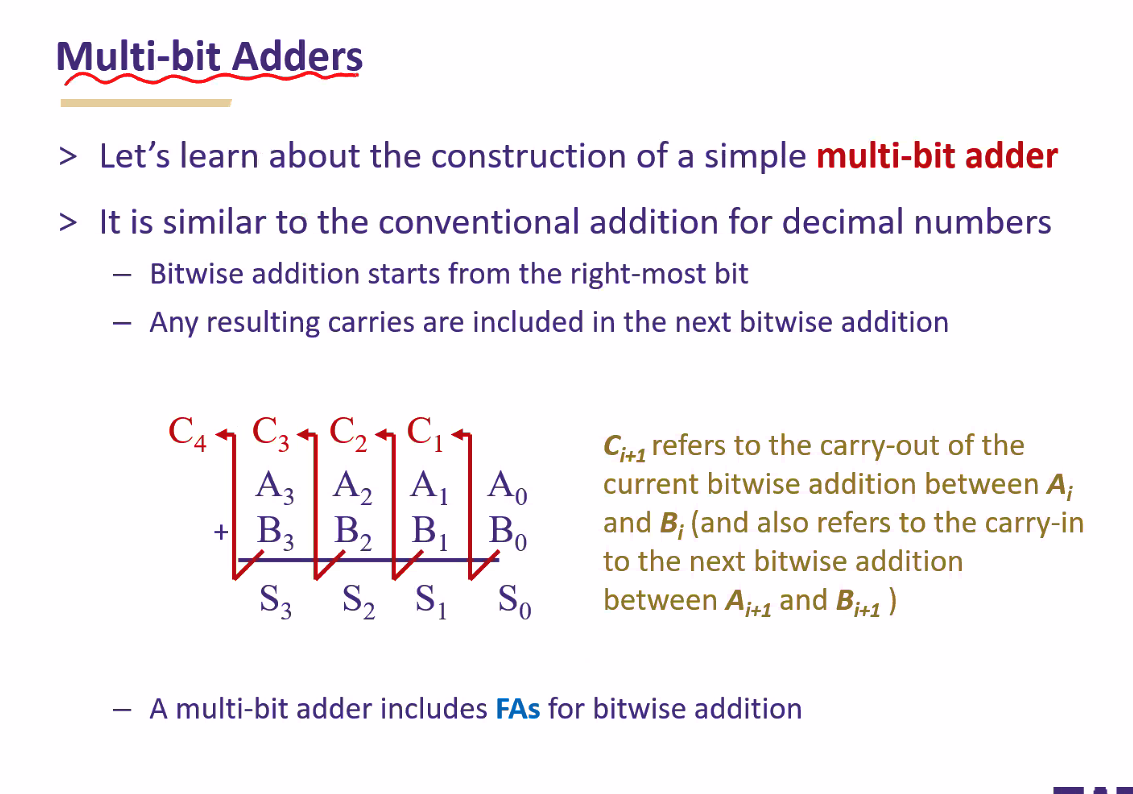

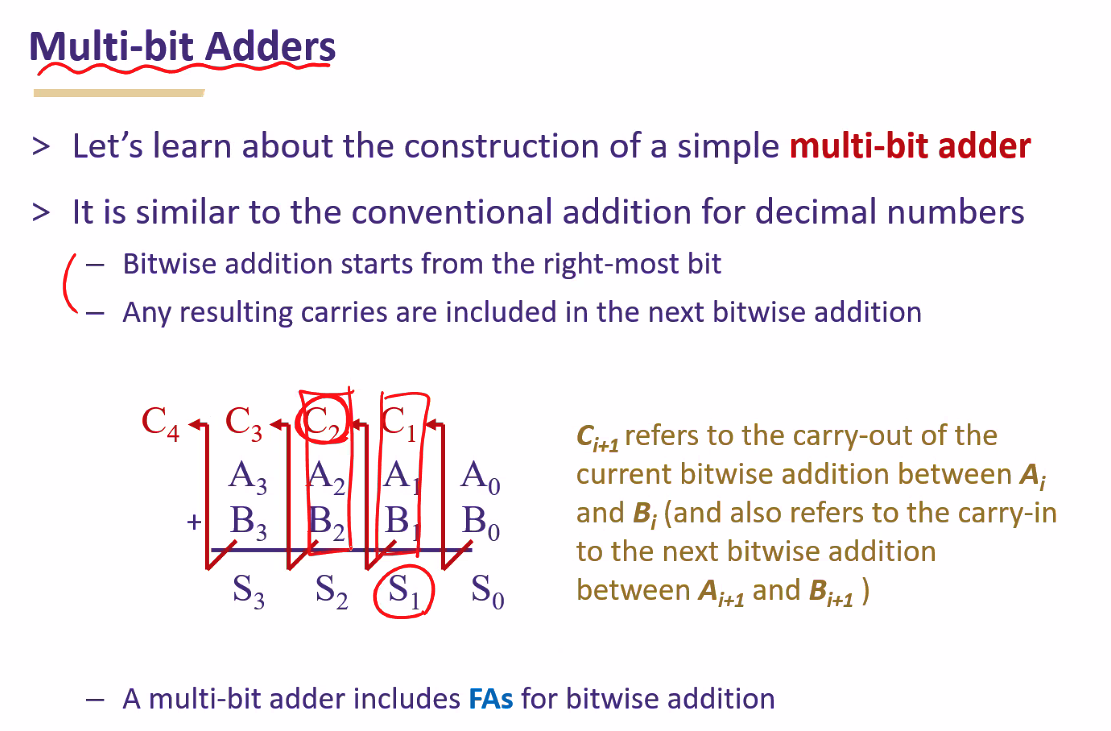

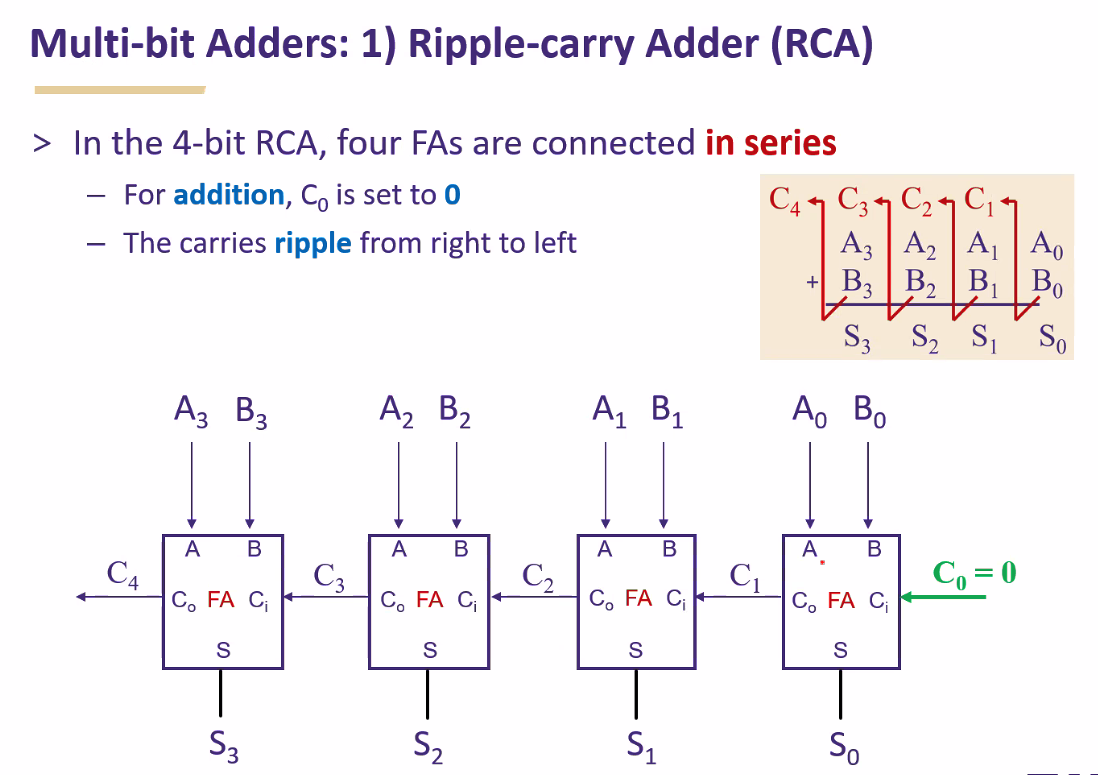

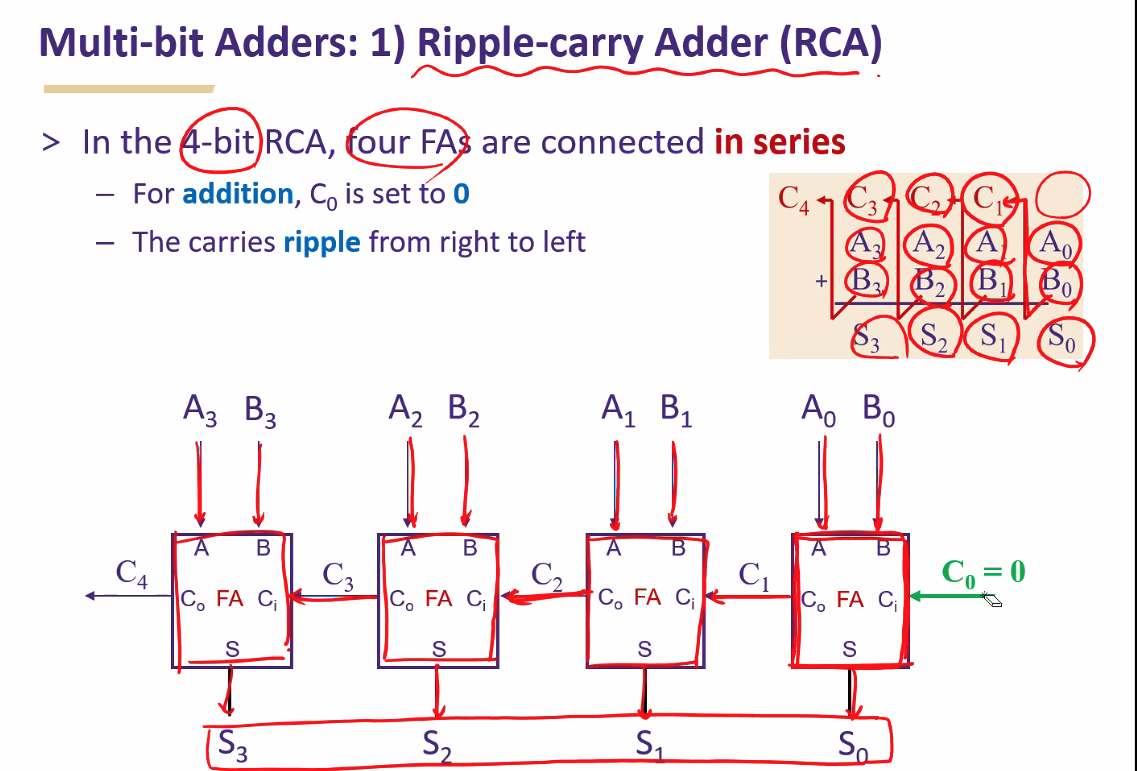

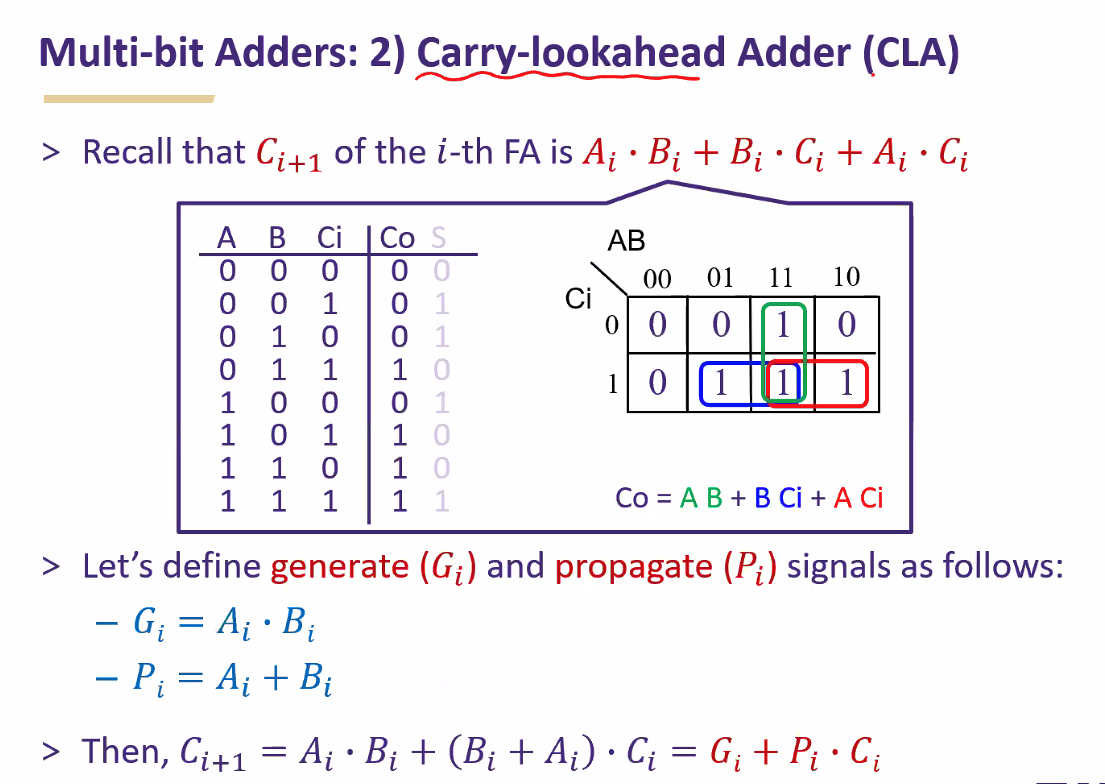

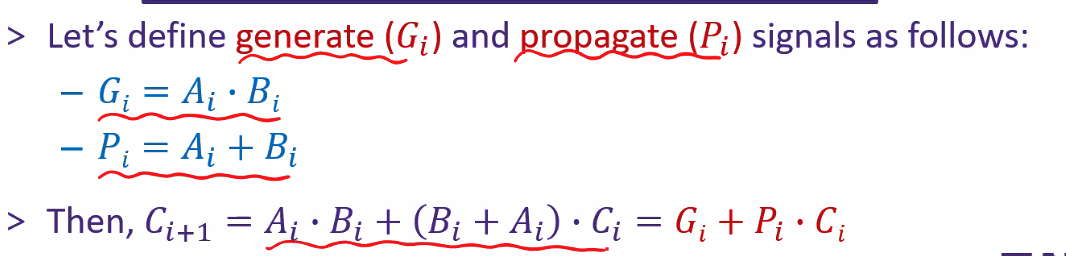

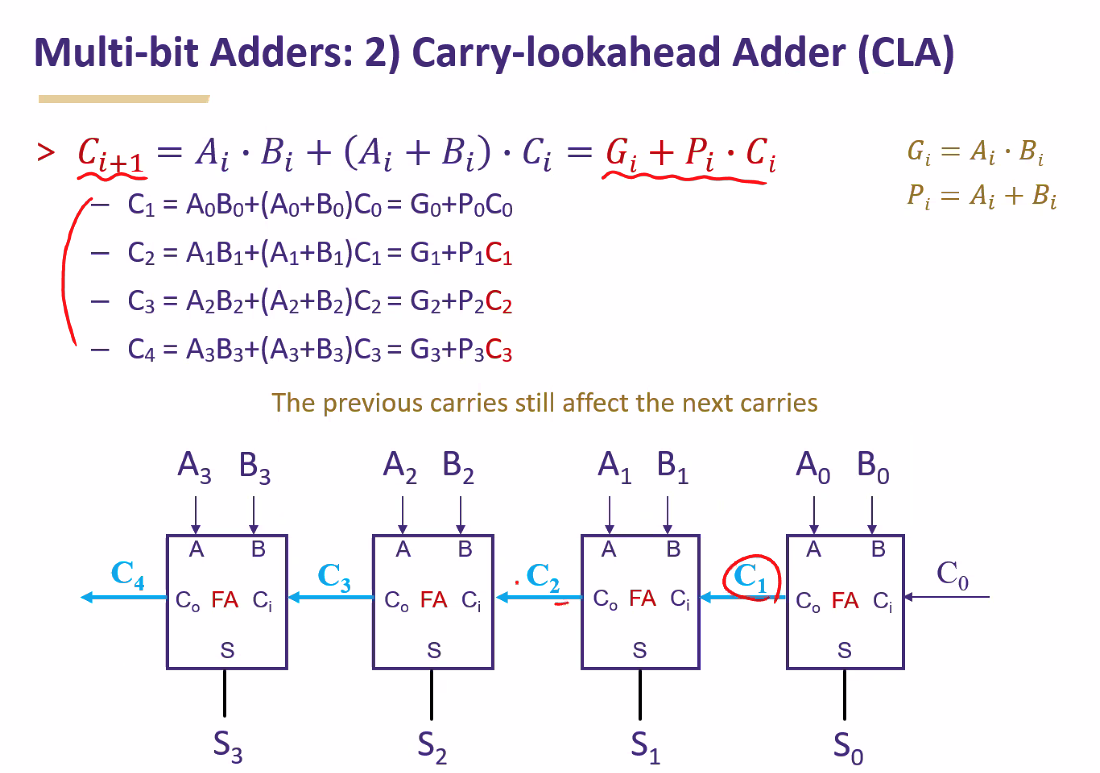

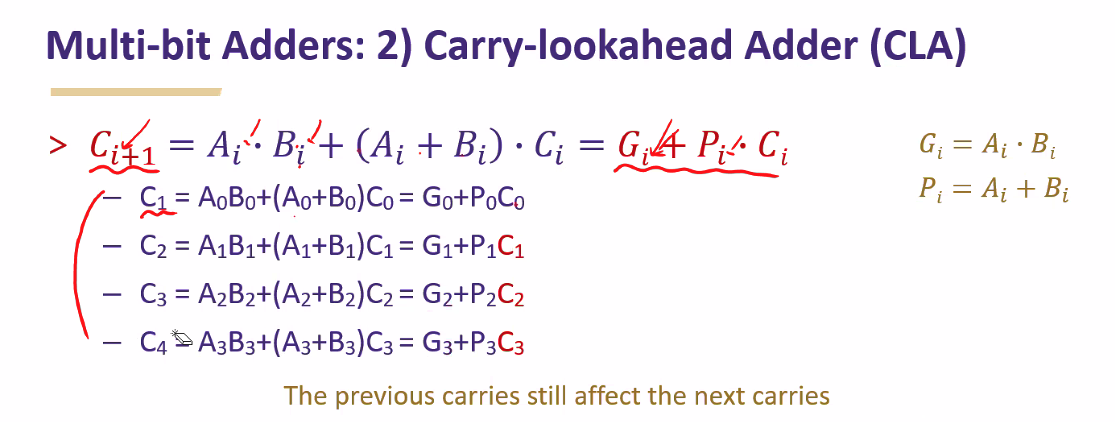

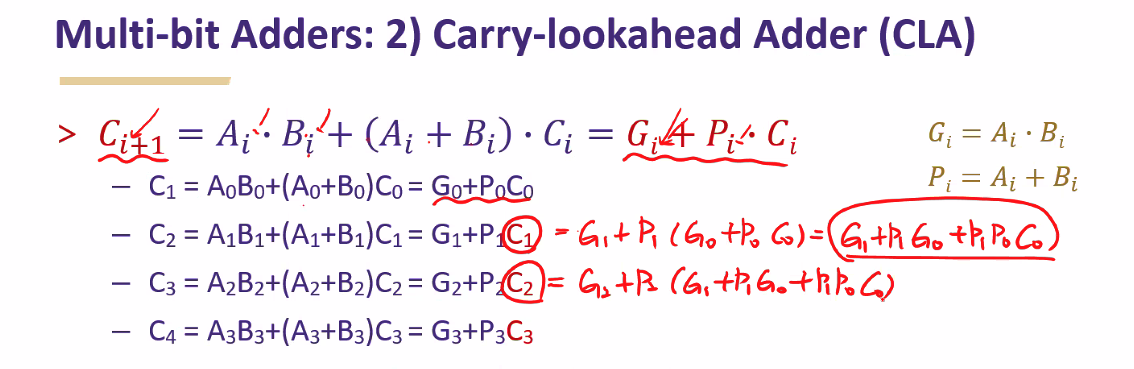

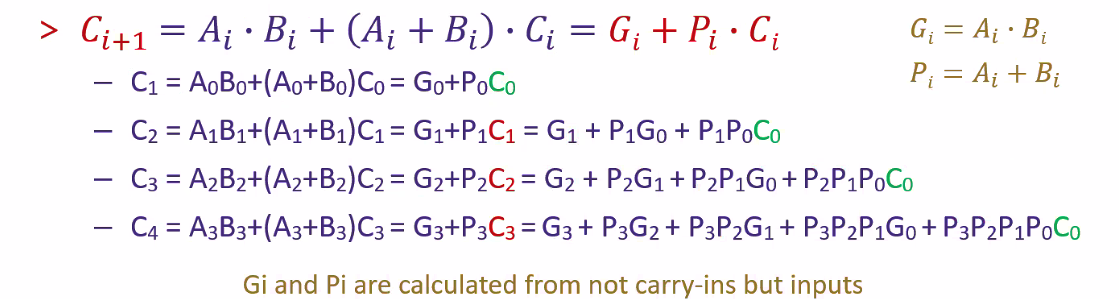

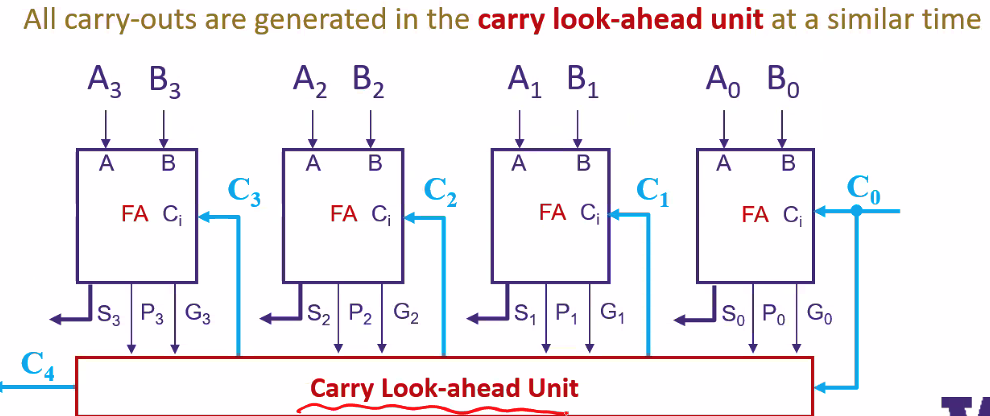

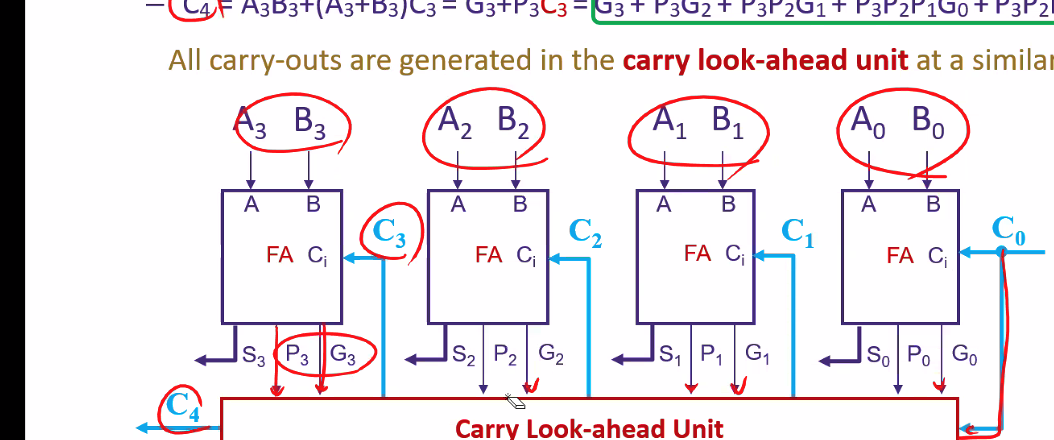

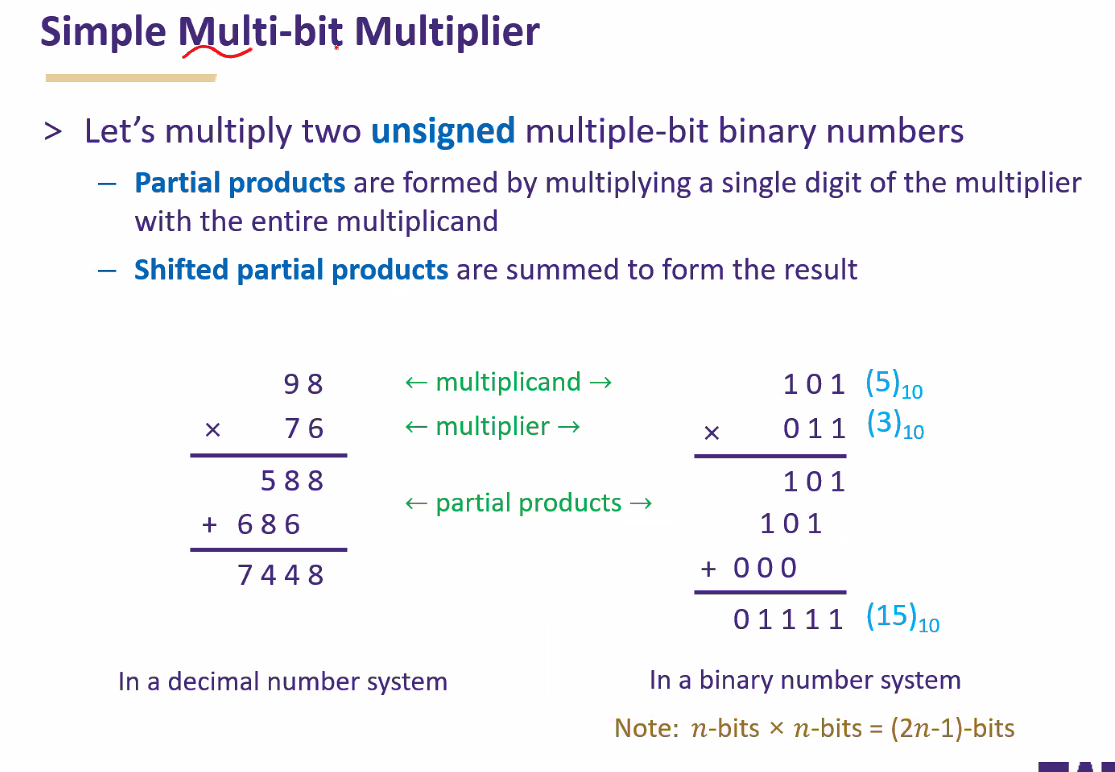

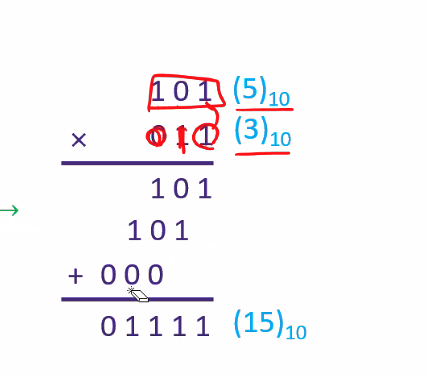

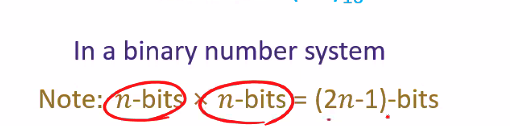

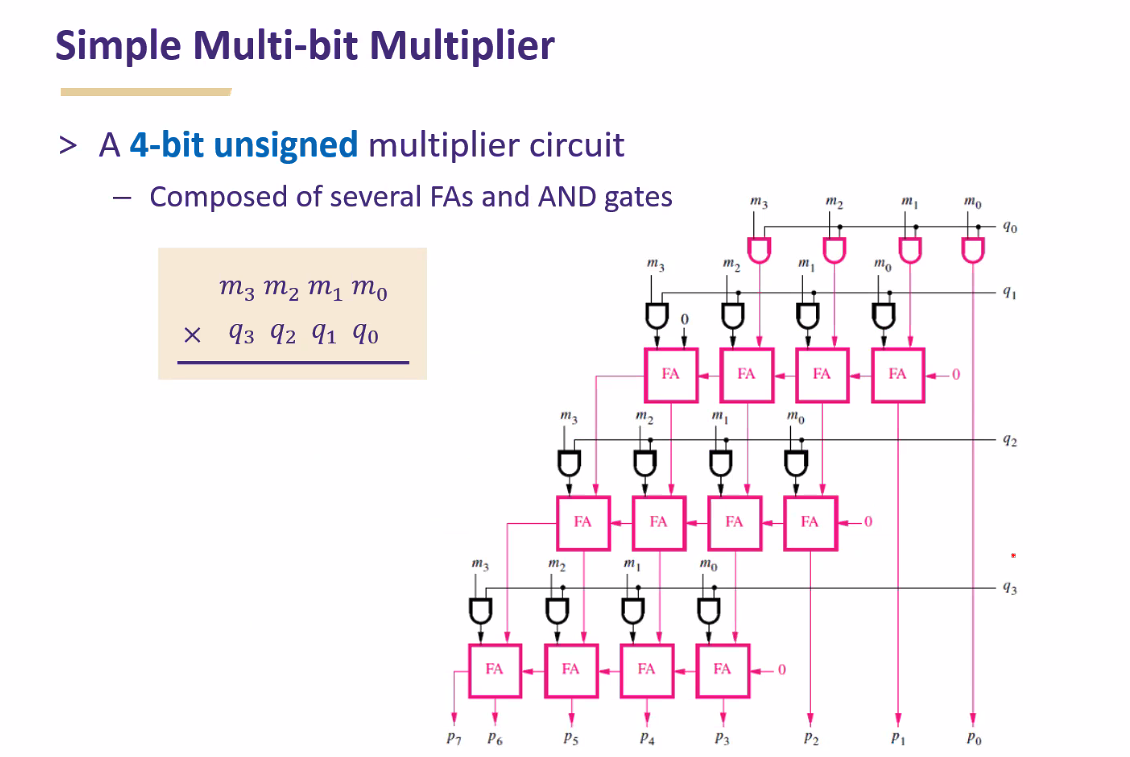

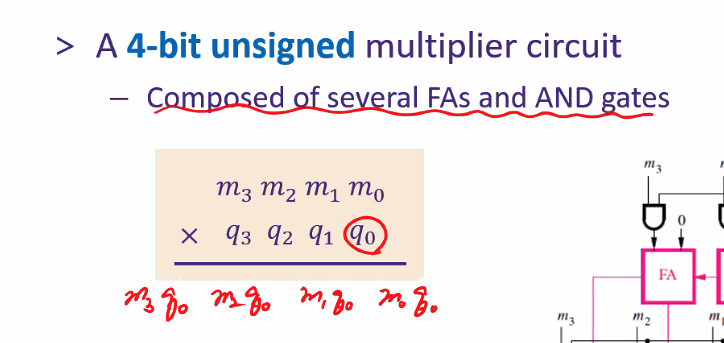

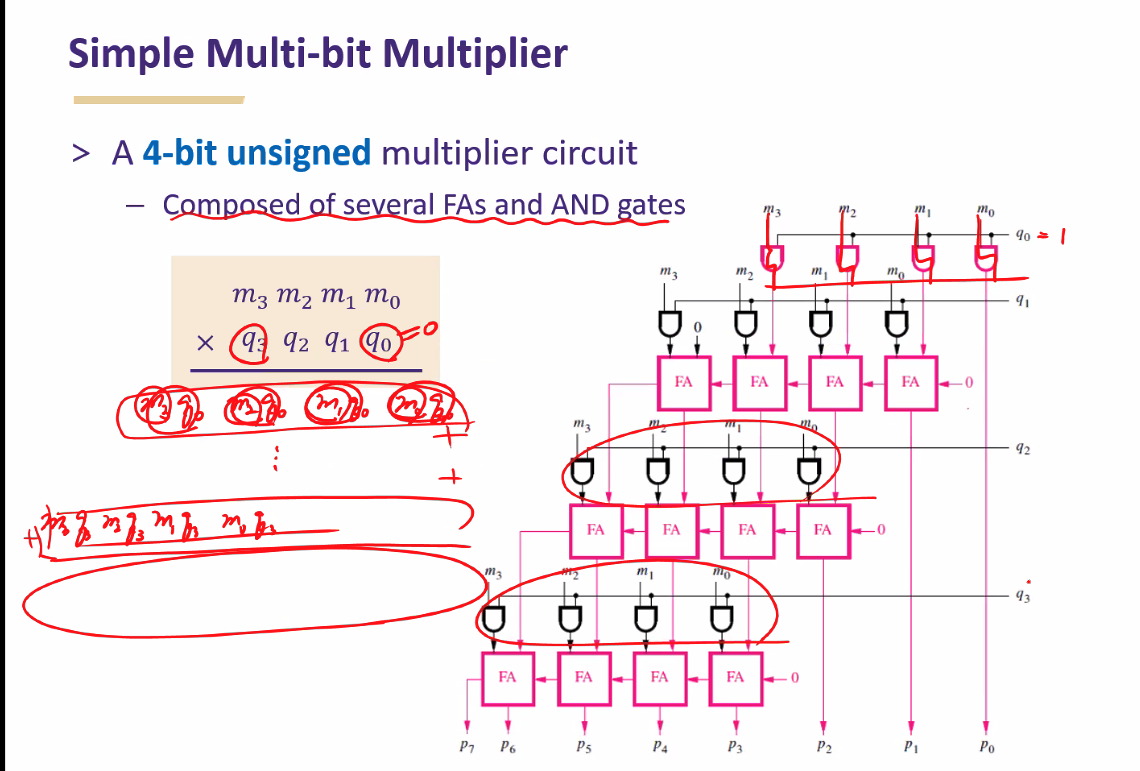

Half adder has 2 inputs, full adder has 3

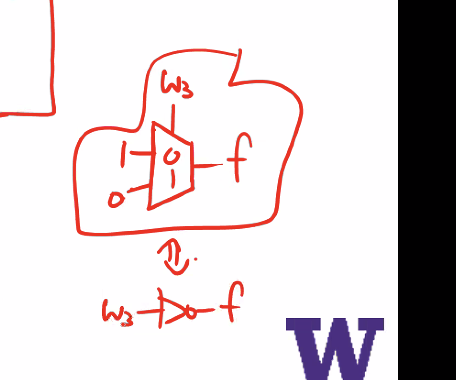

XOR gate

Lecture 8

Lecture 9

Lecture 10

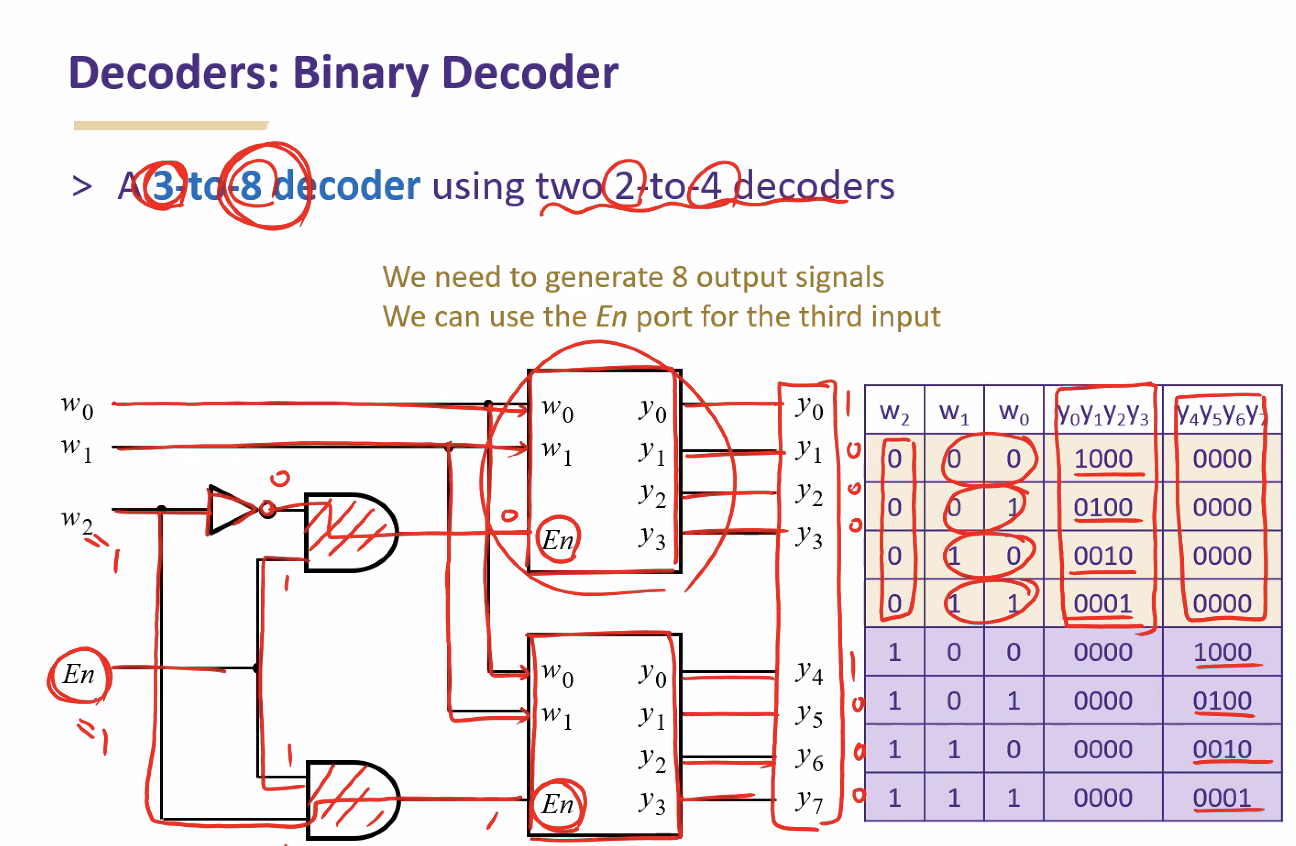

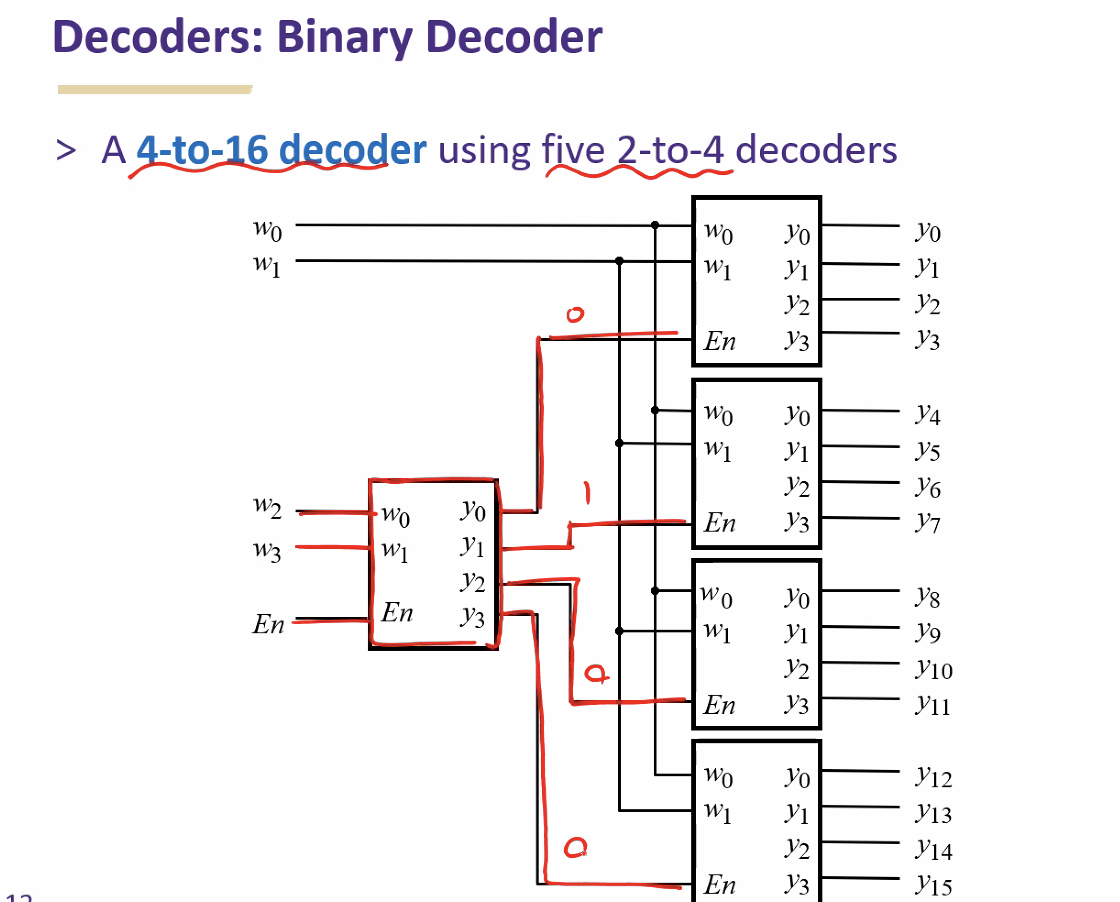

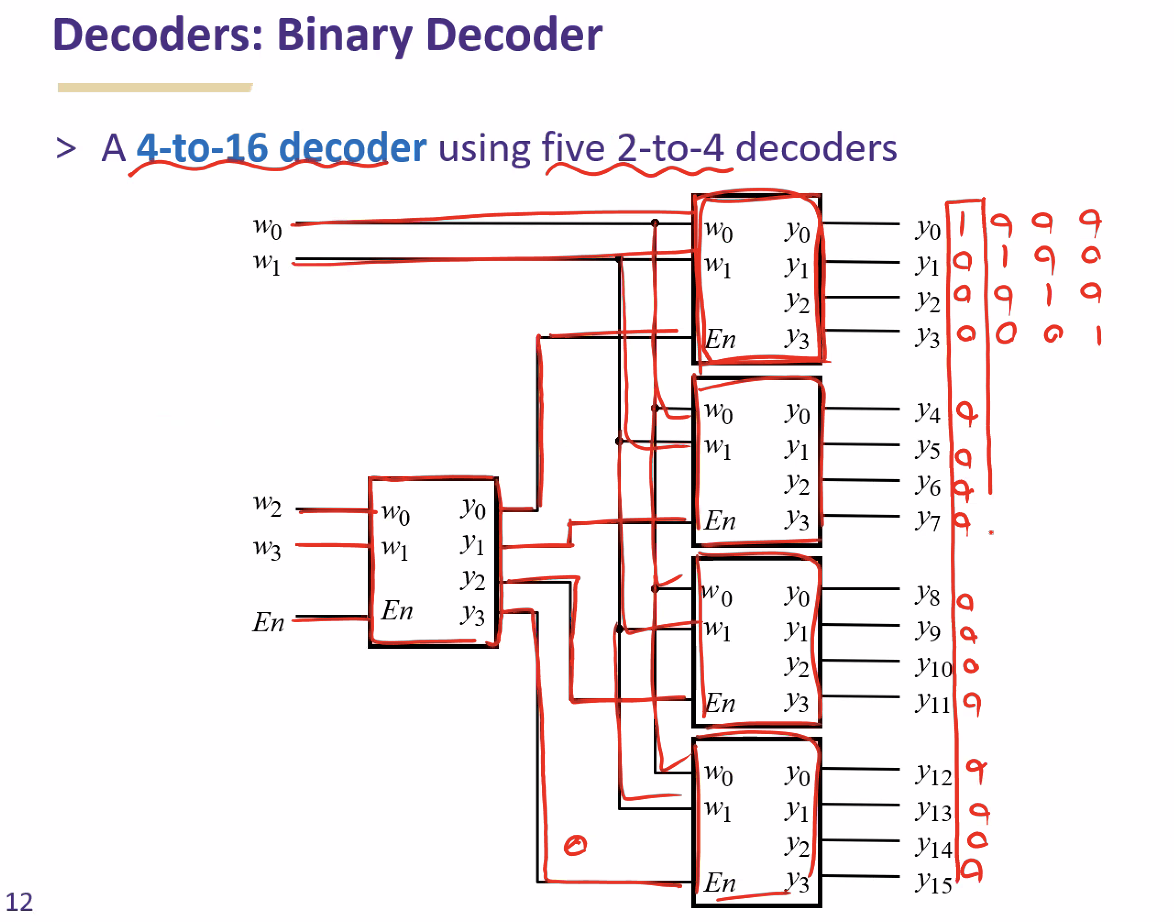

Review

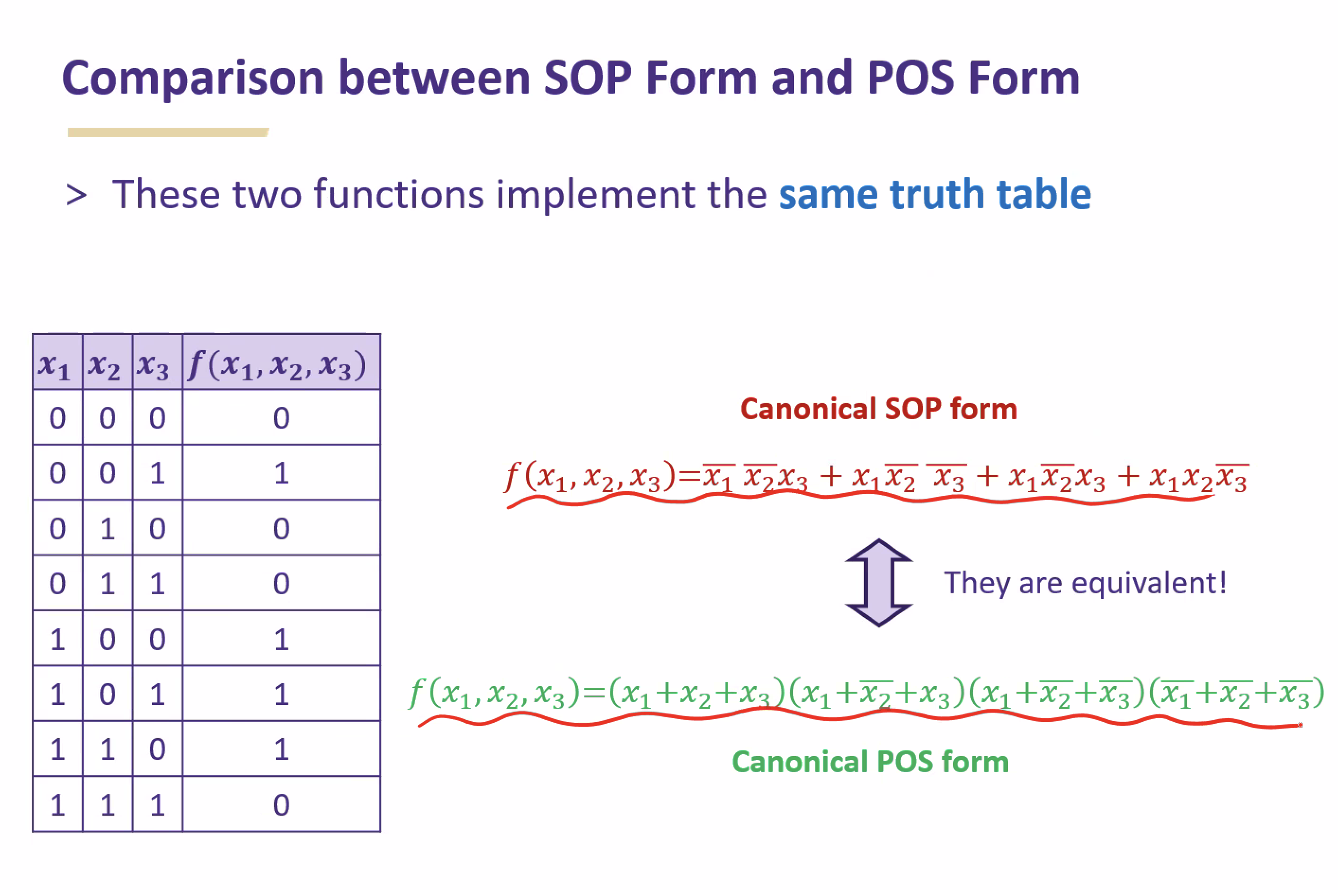

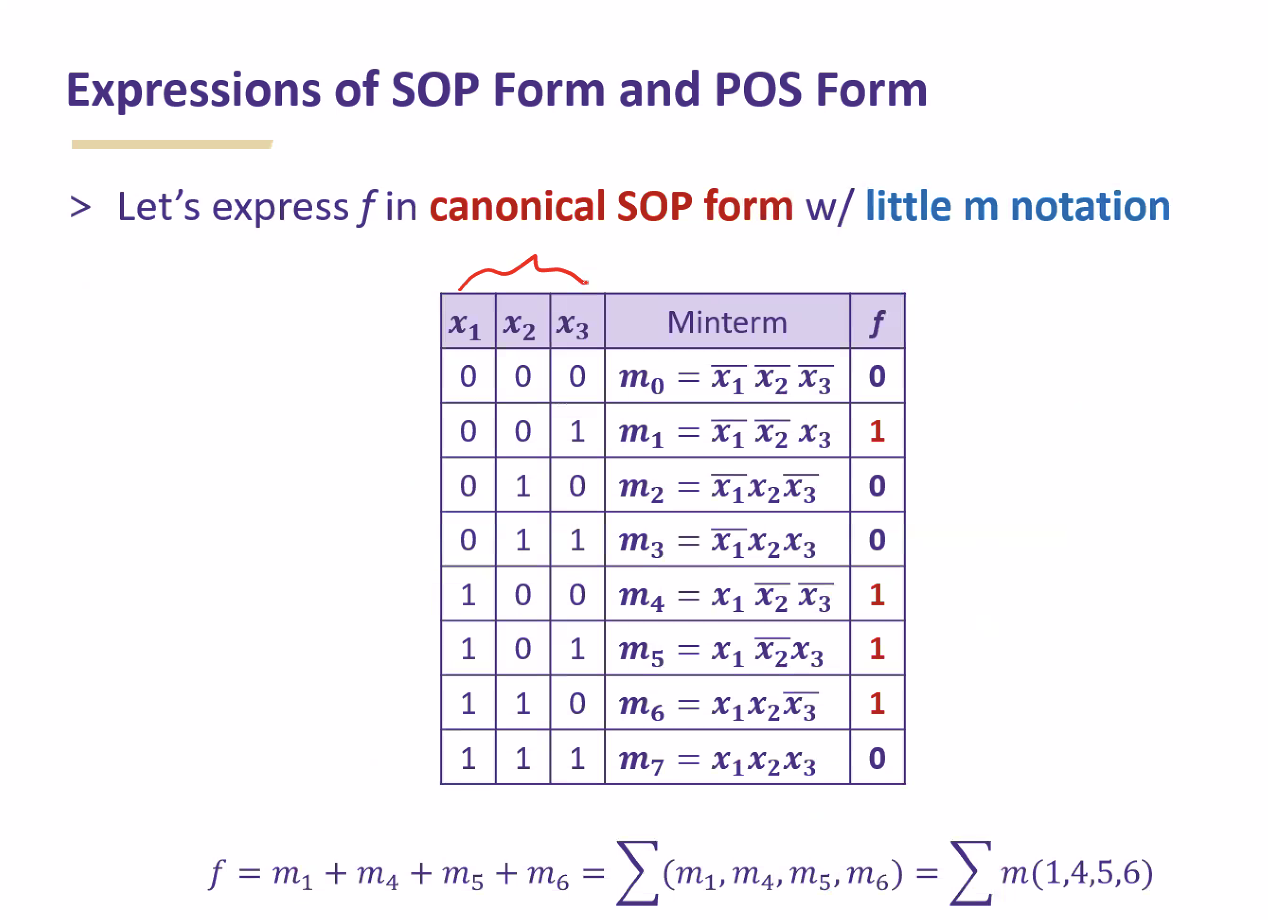

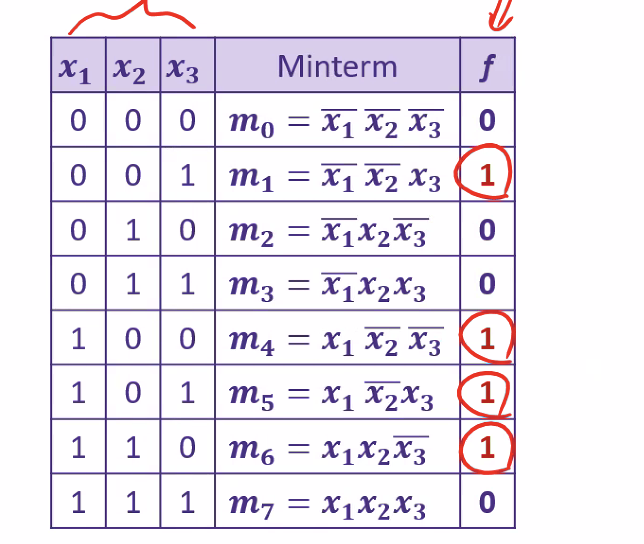

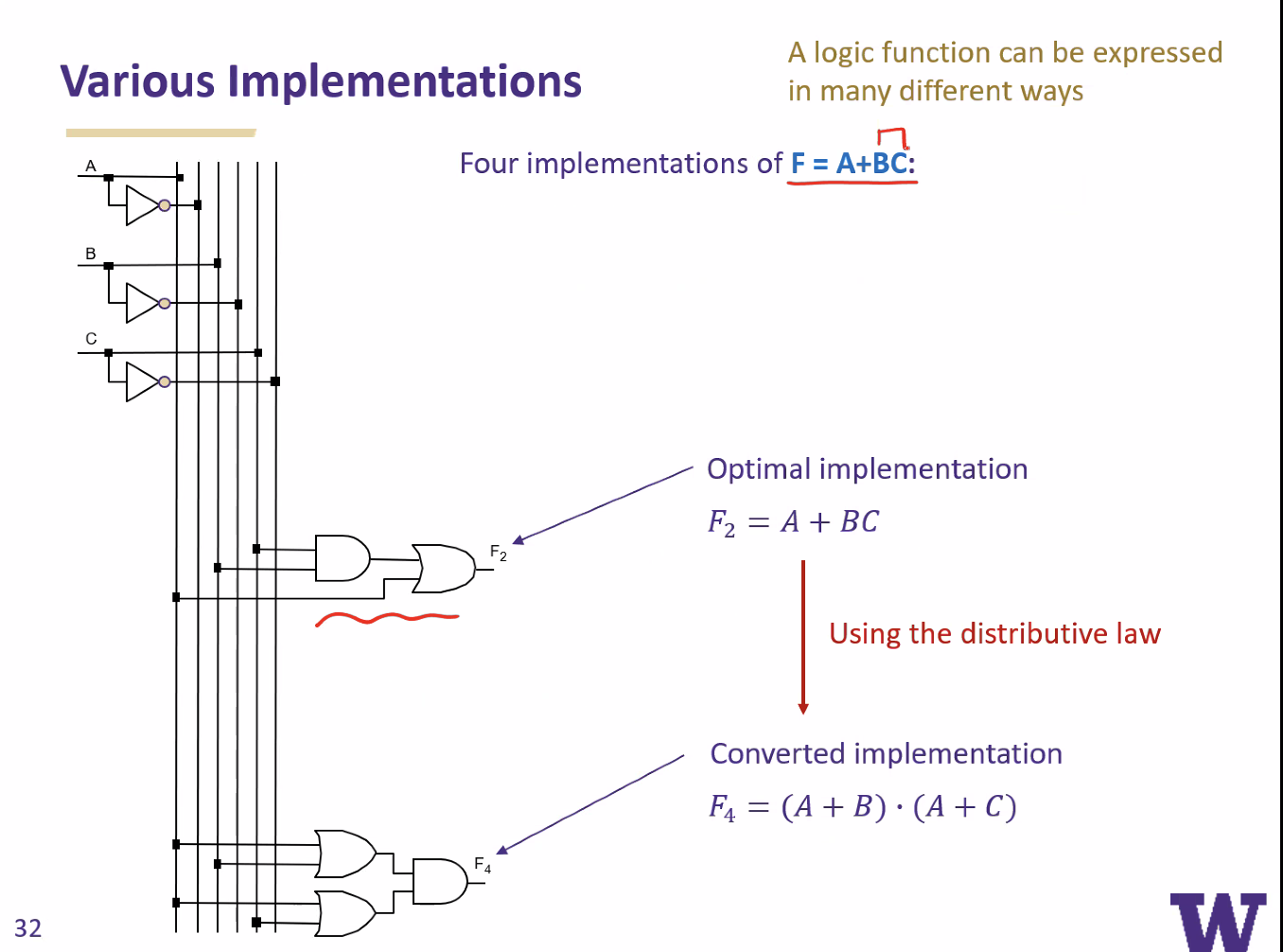

Product of Sums

NAND/NOR

Lecture 12

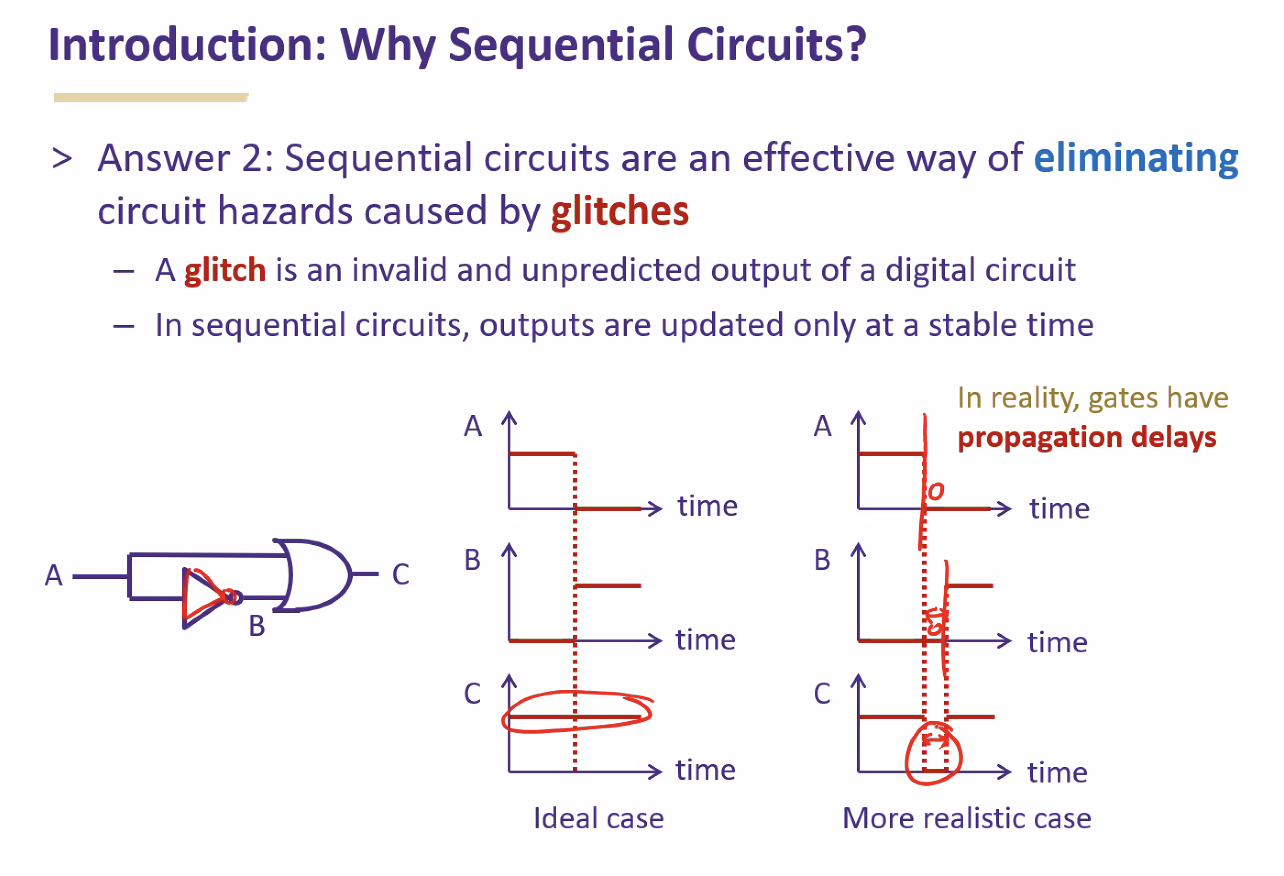

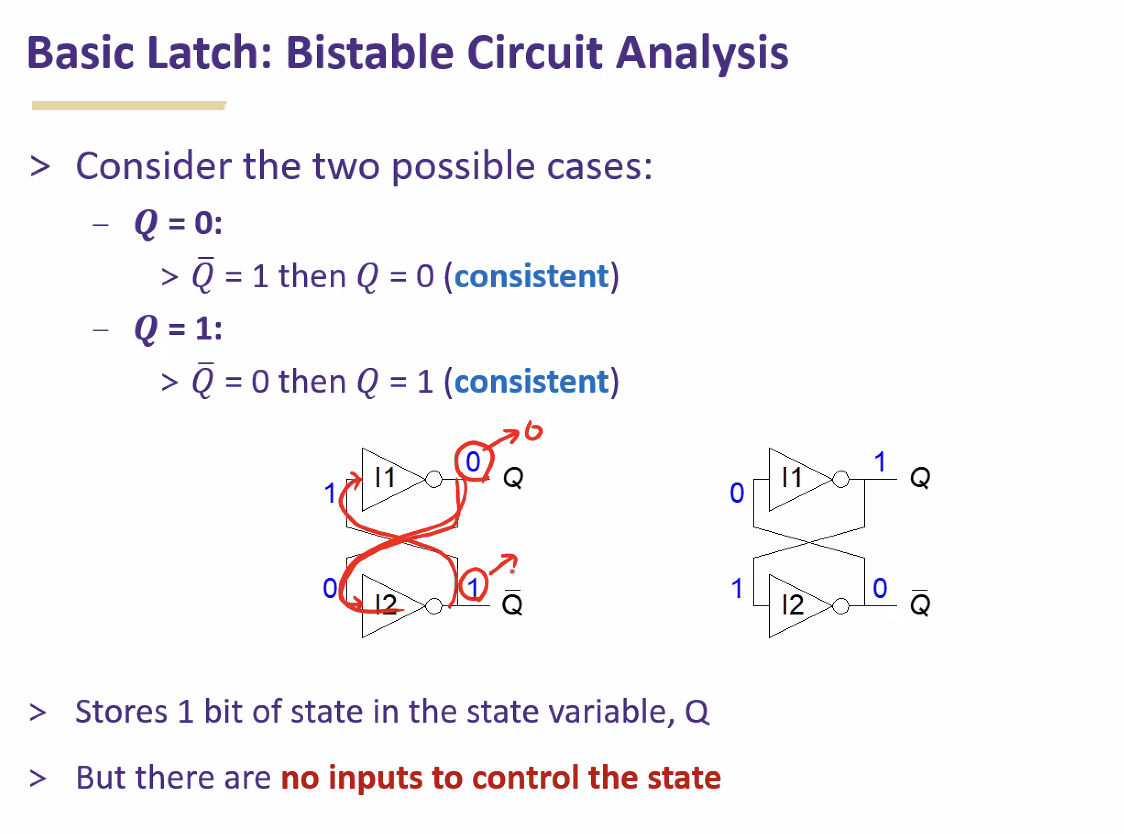

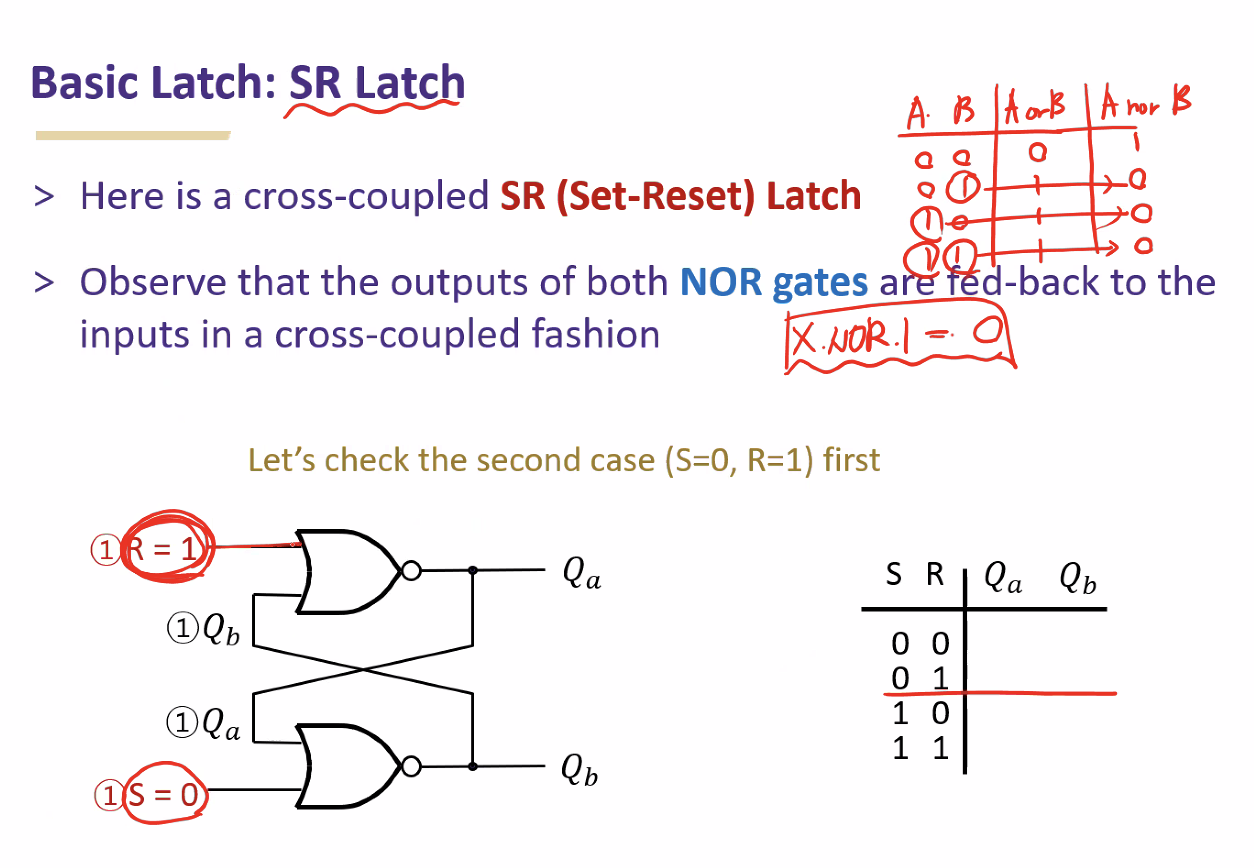

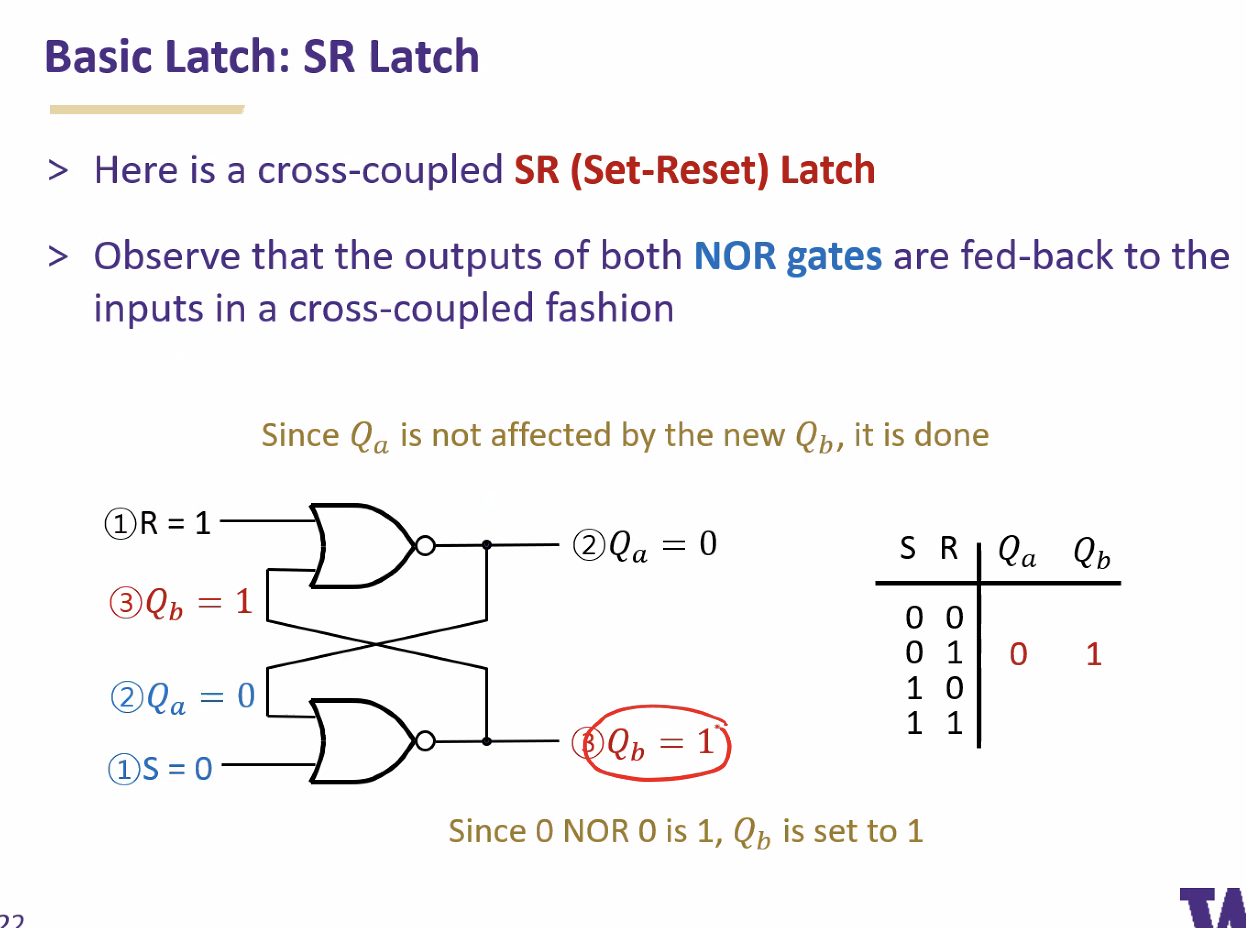

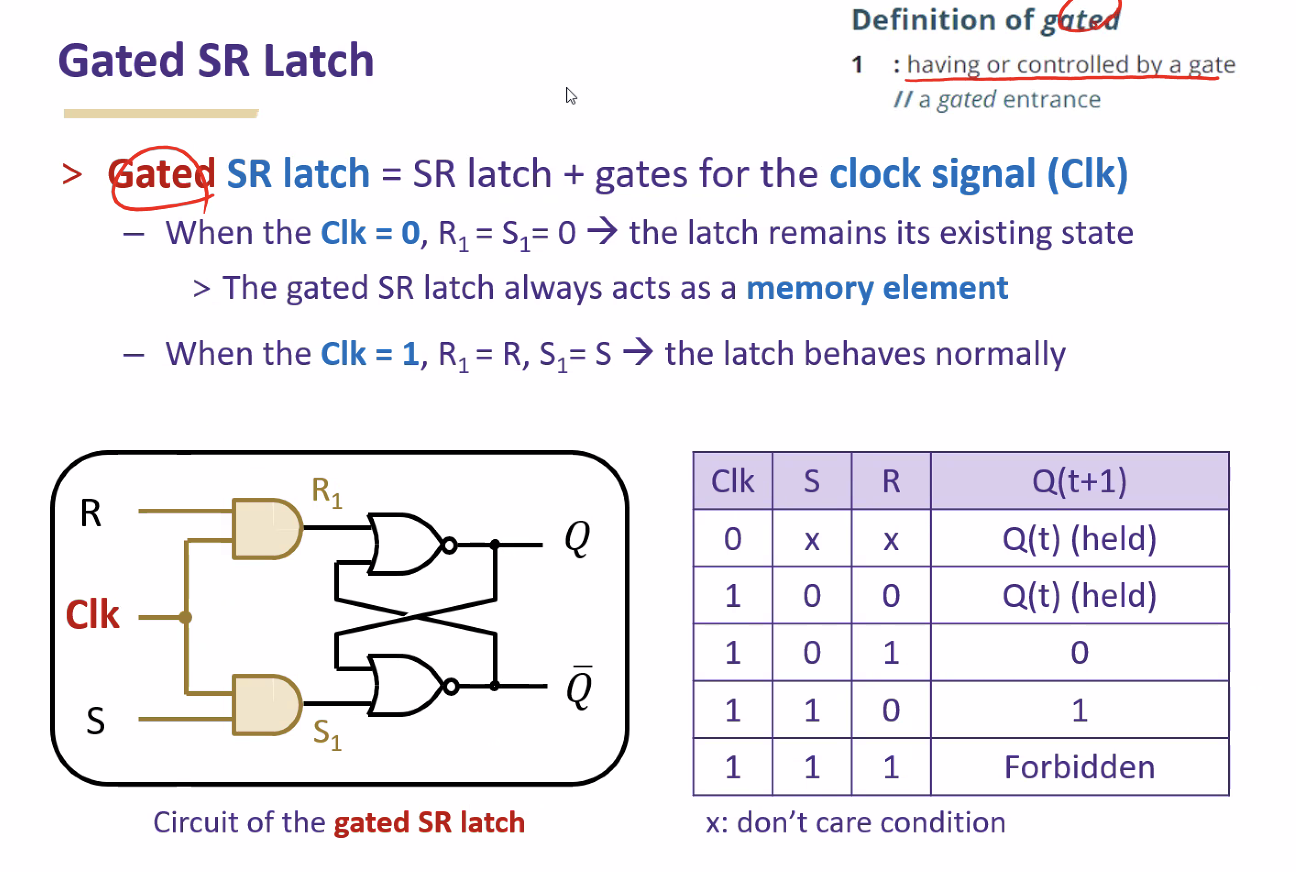

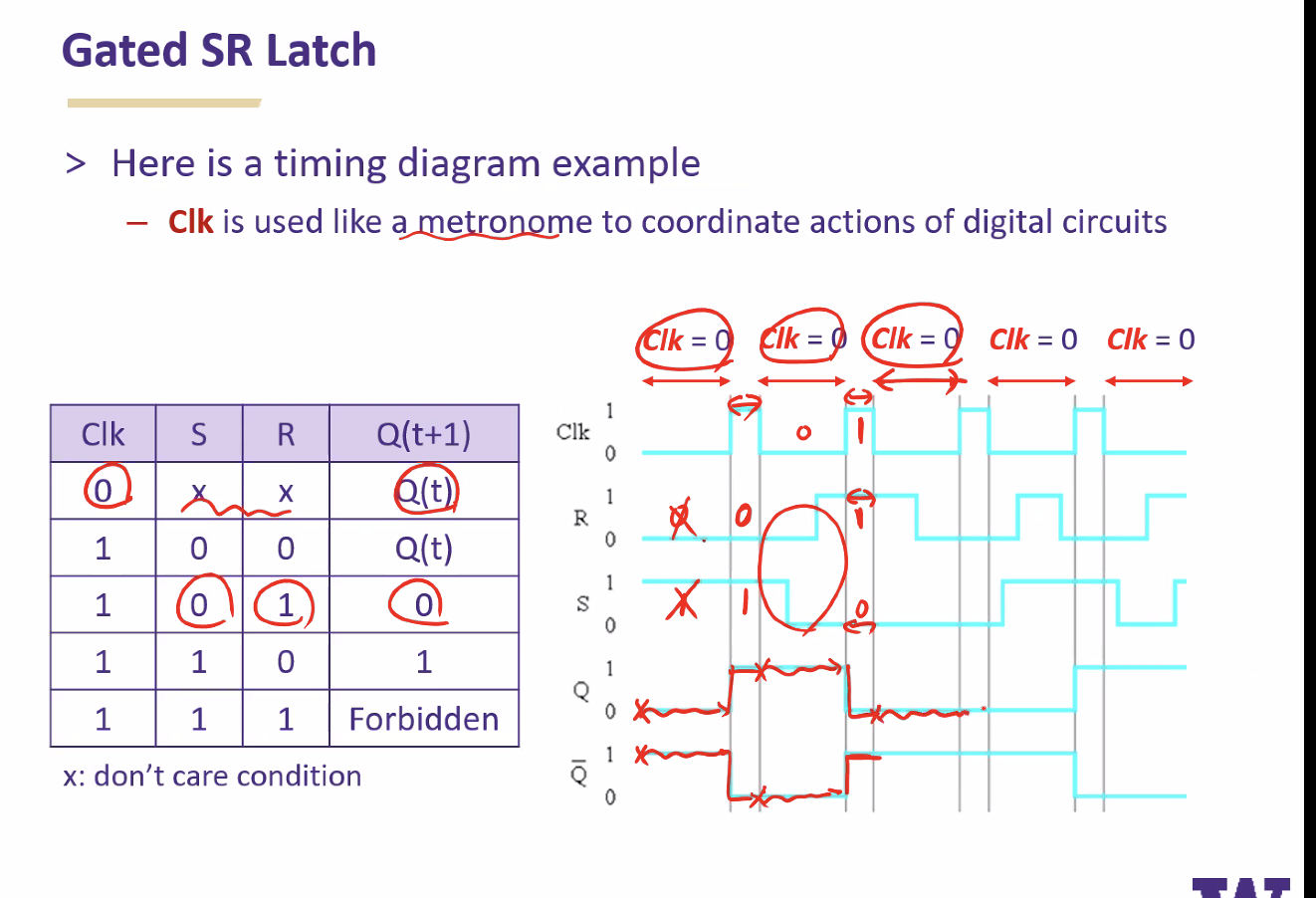

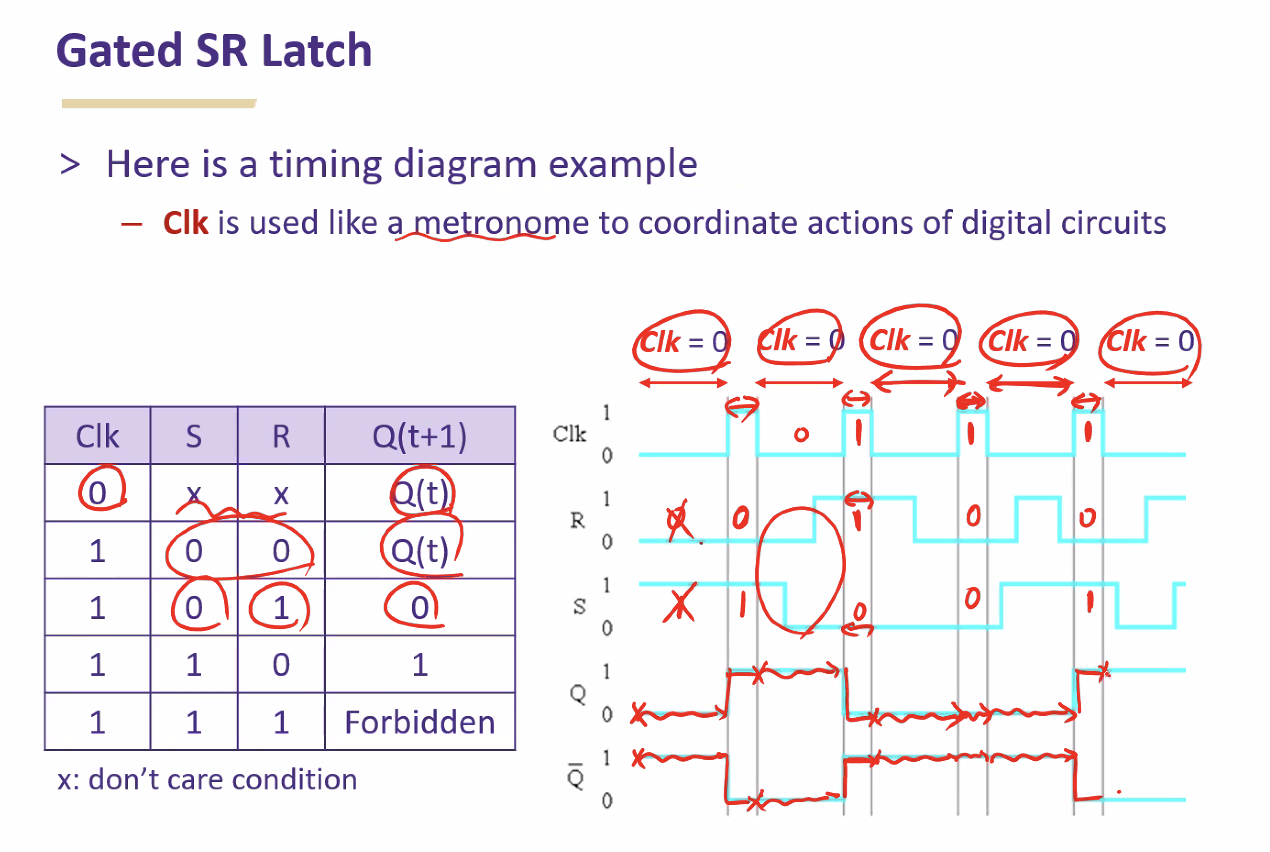

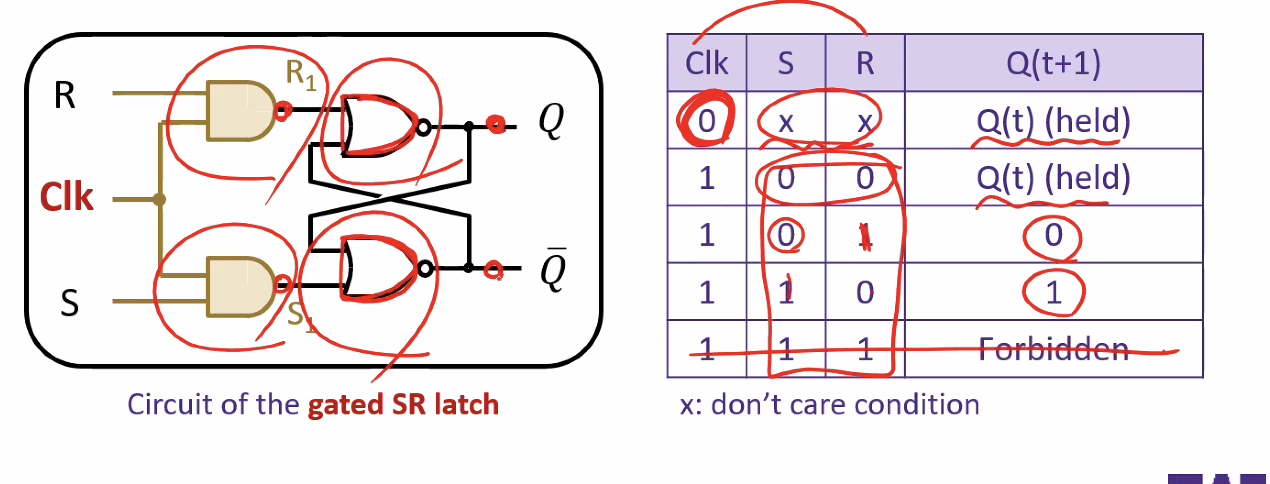

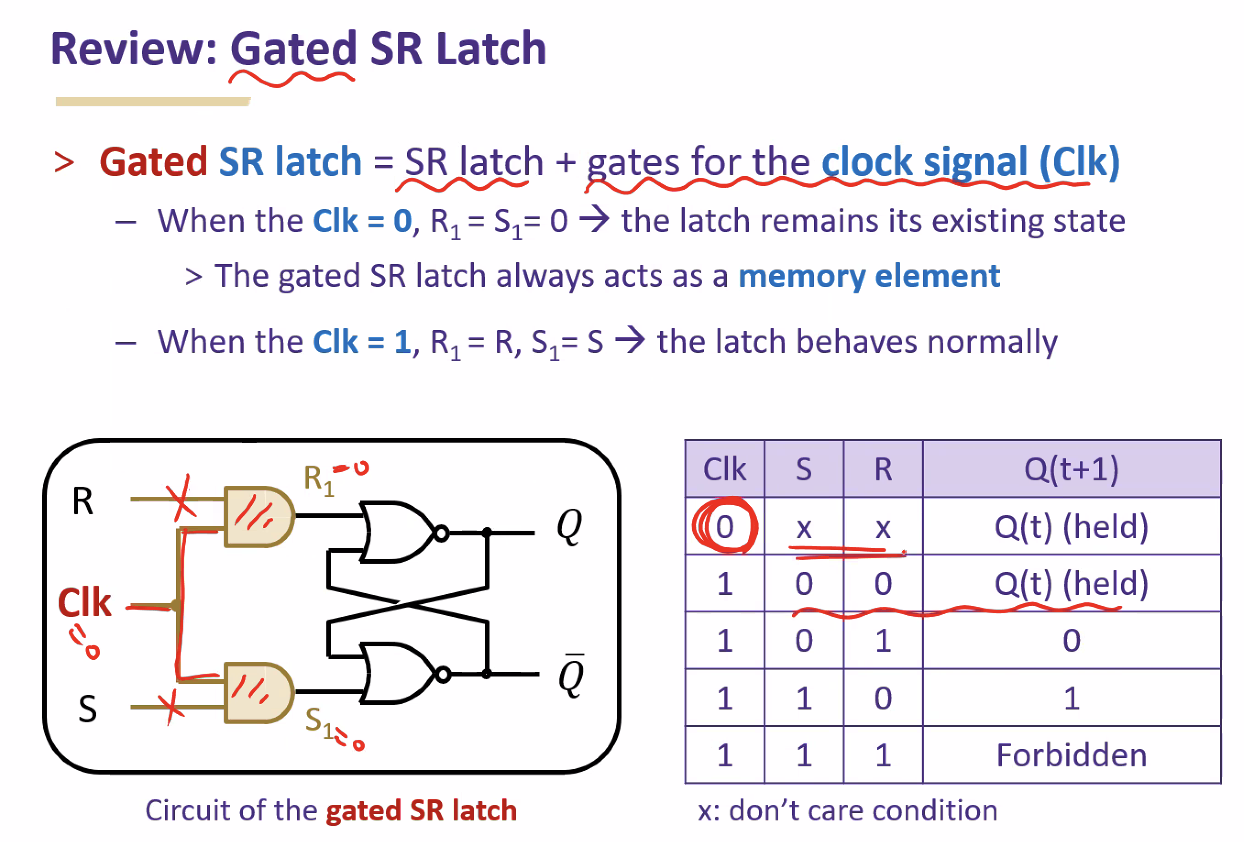

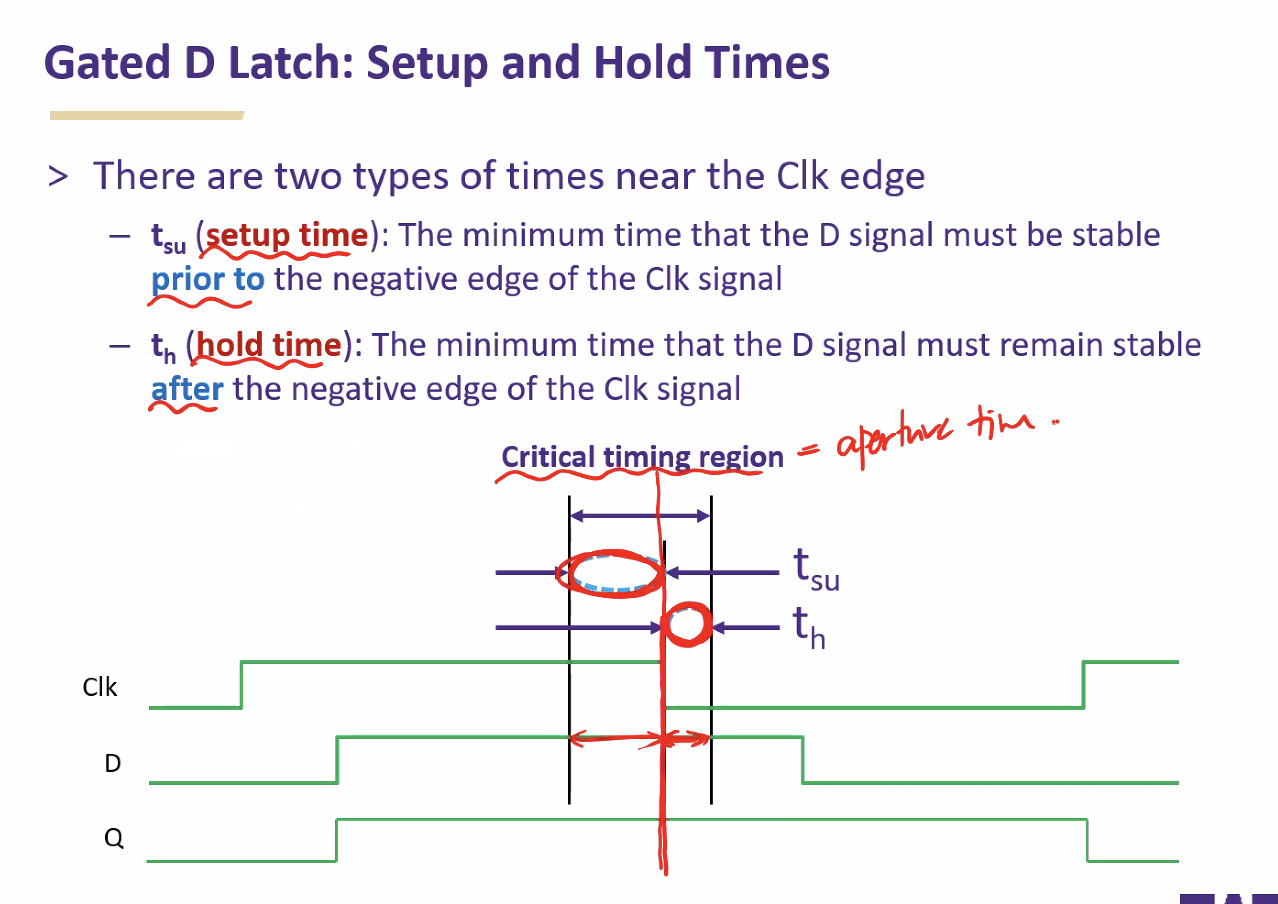

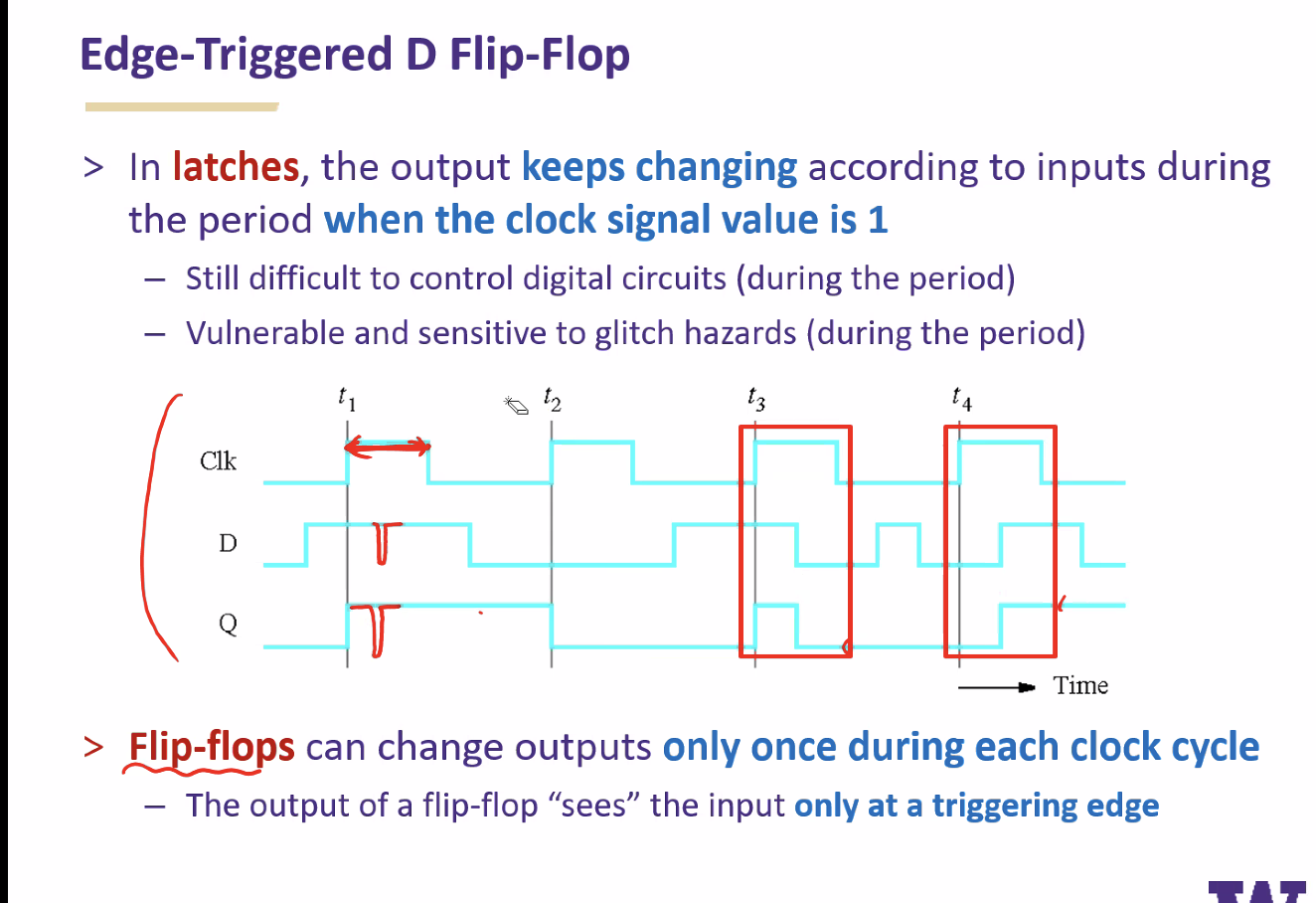

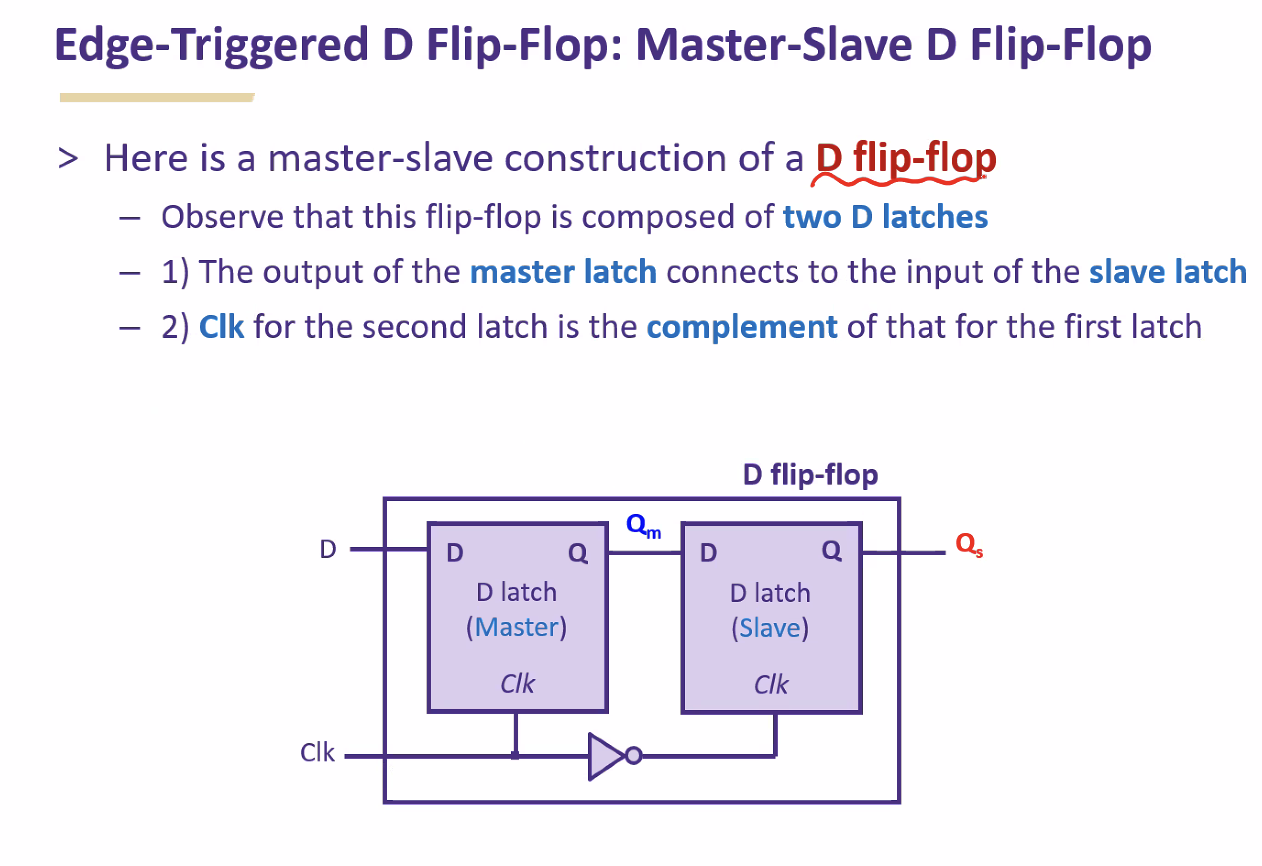

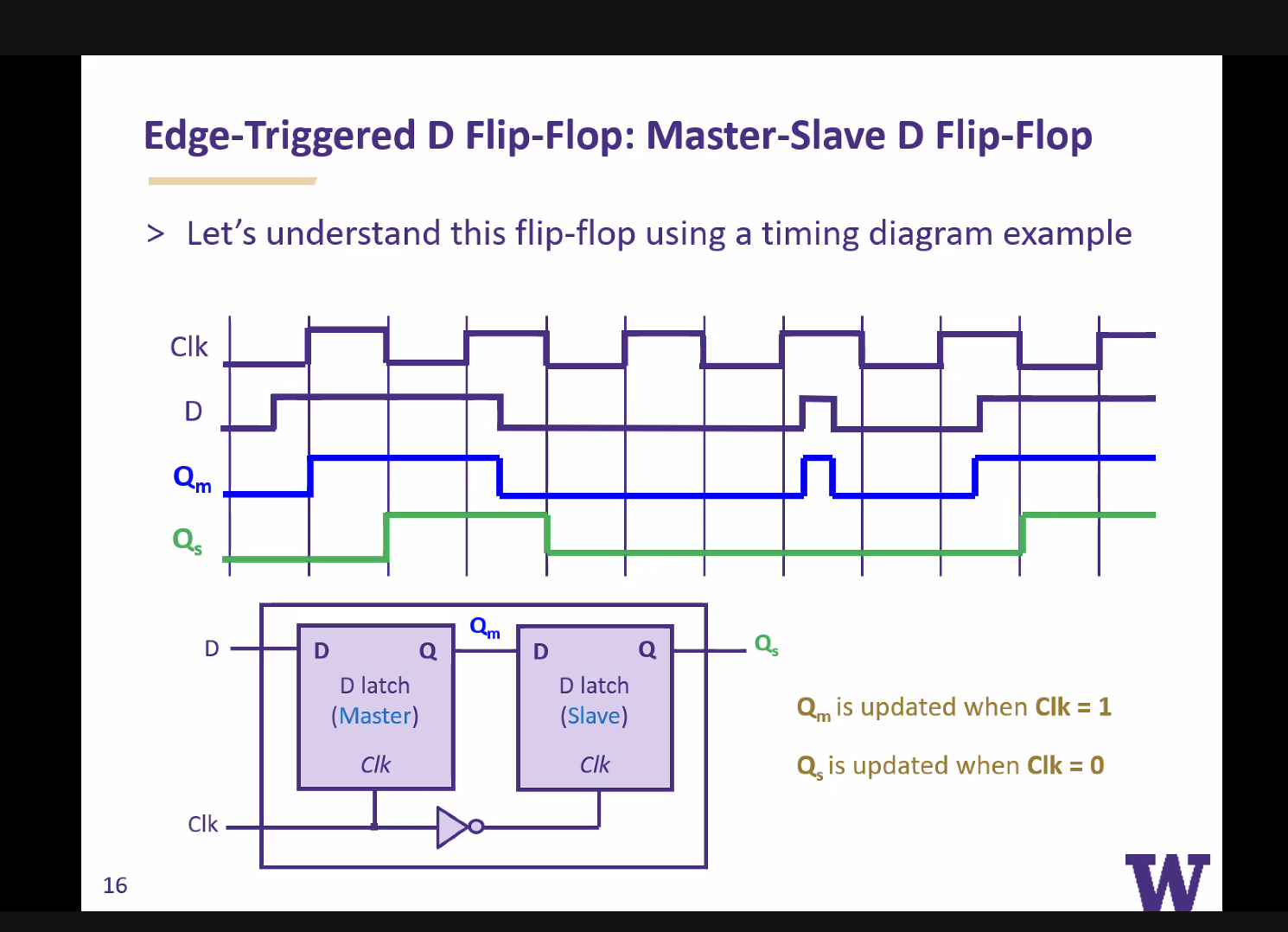

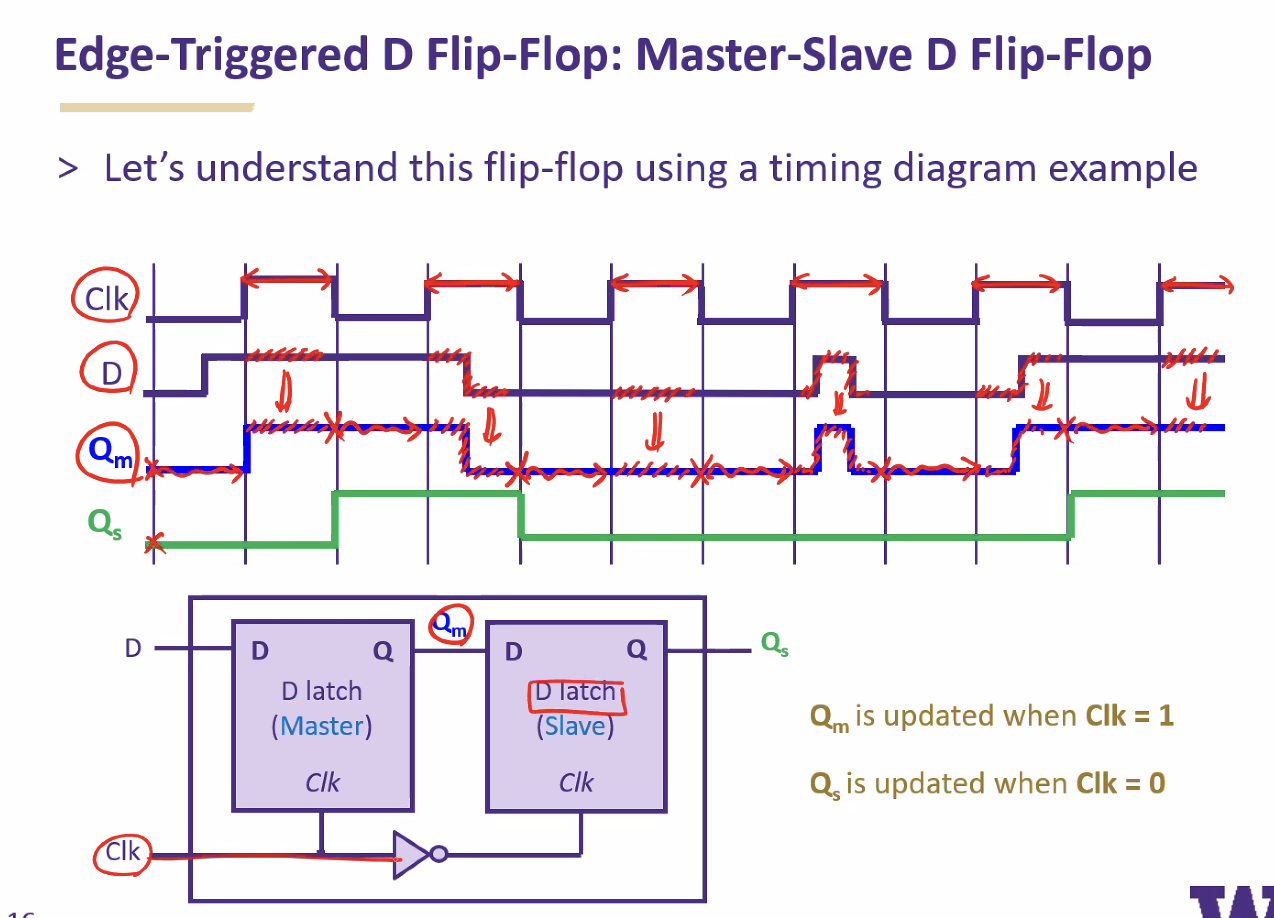

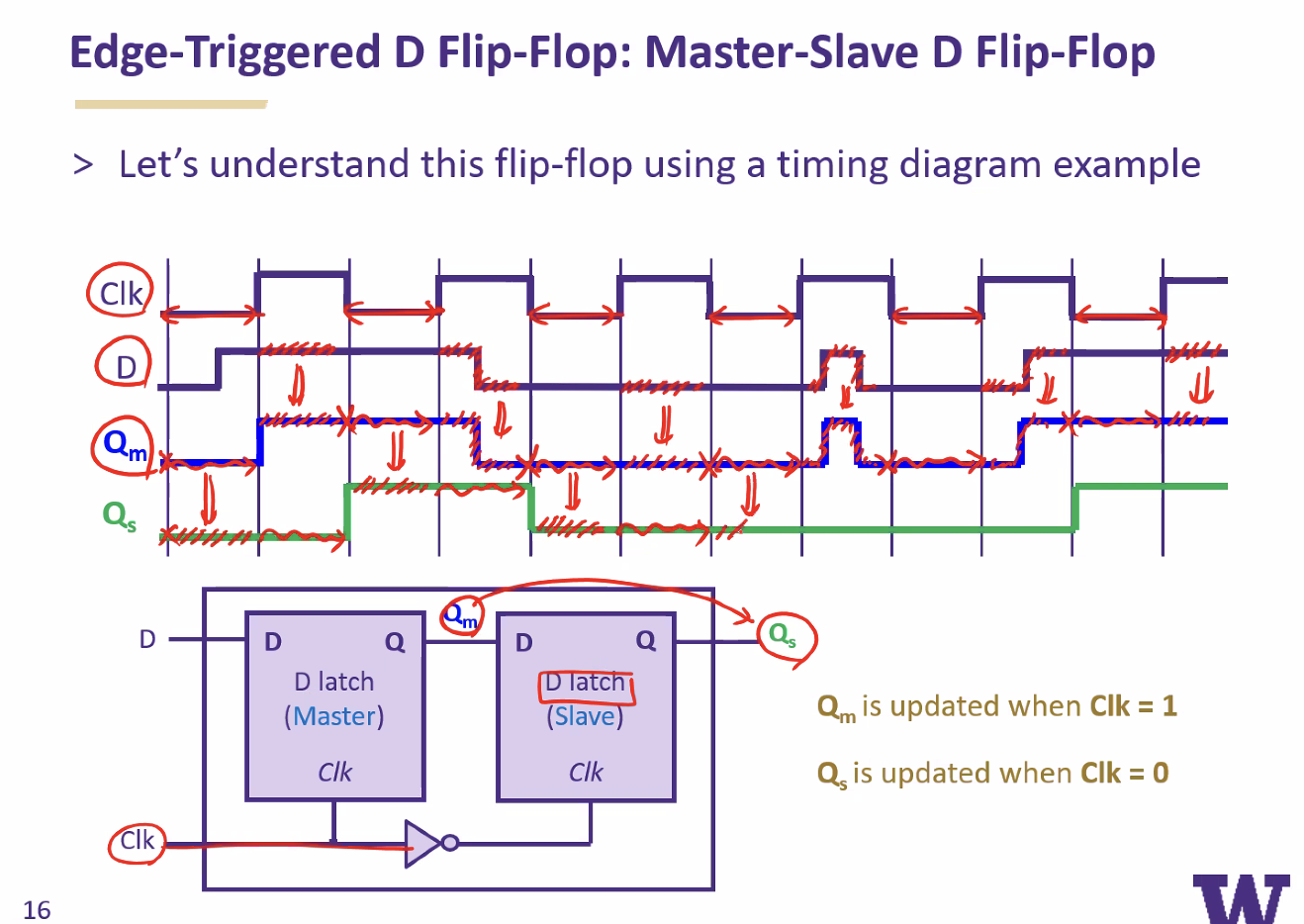

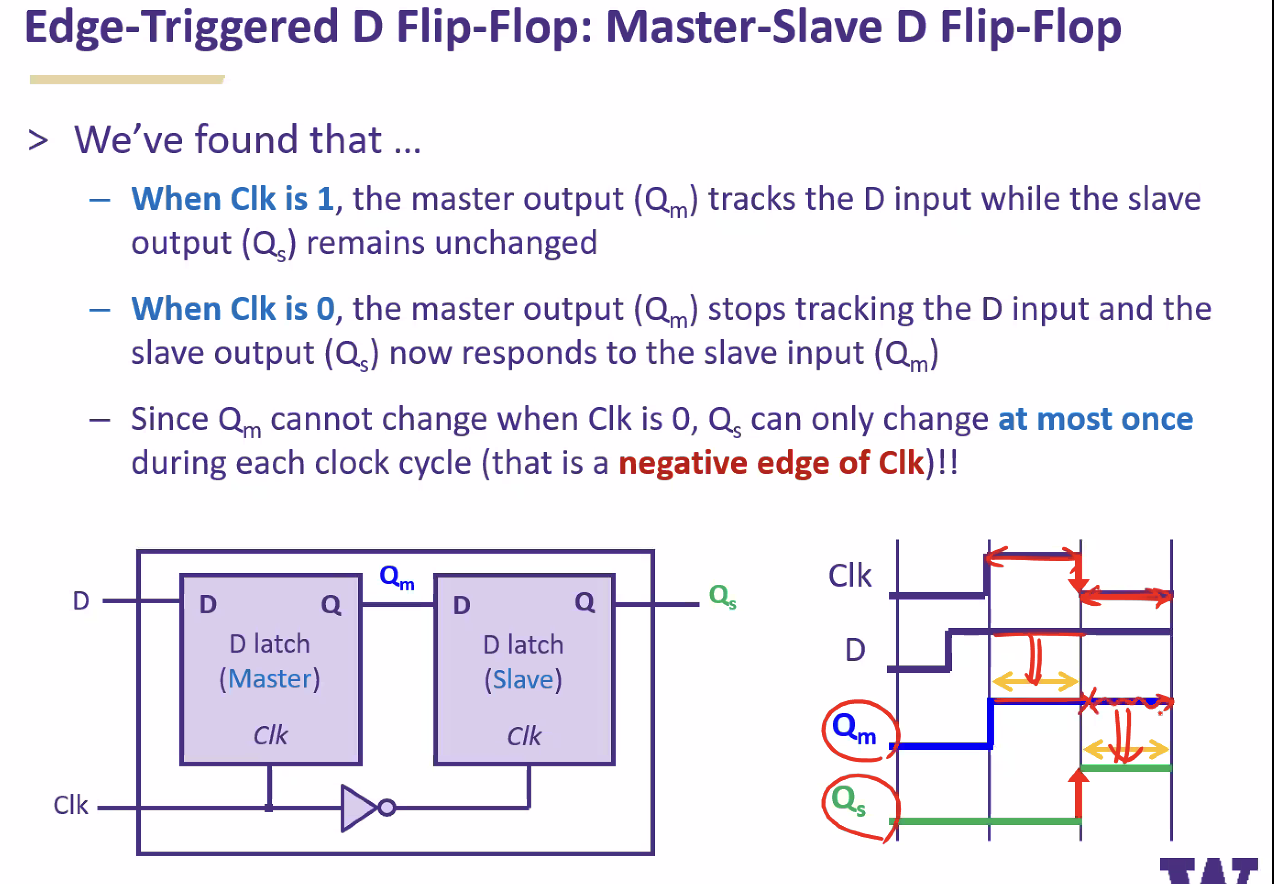

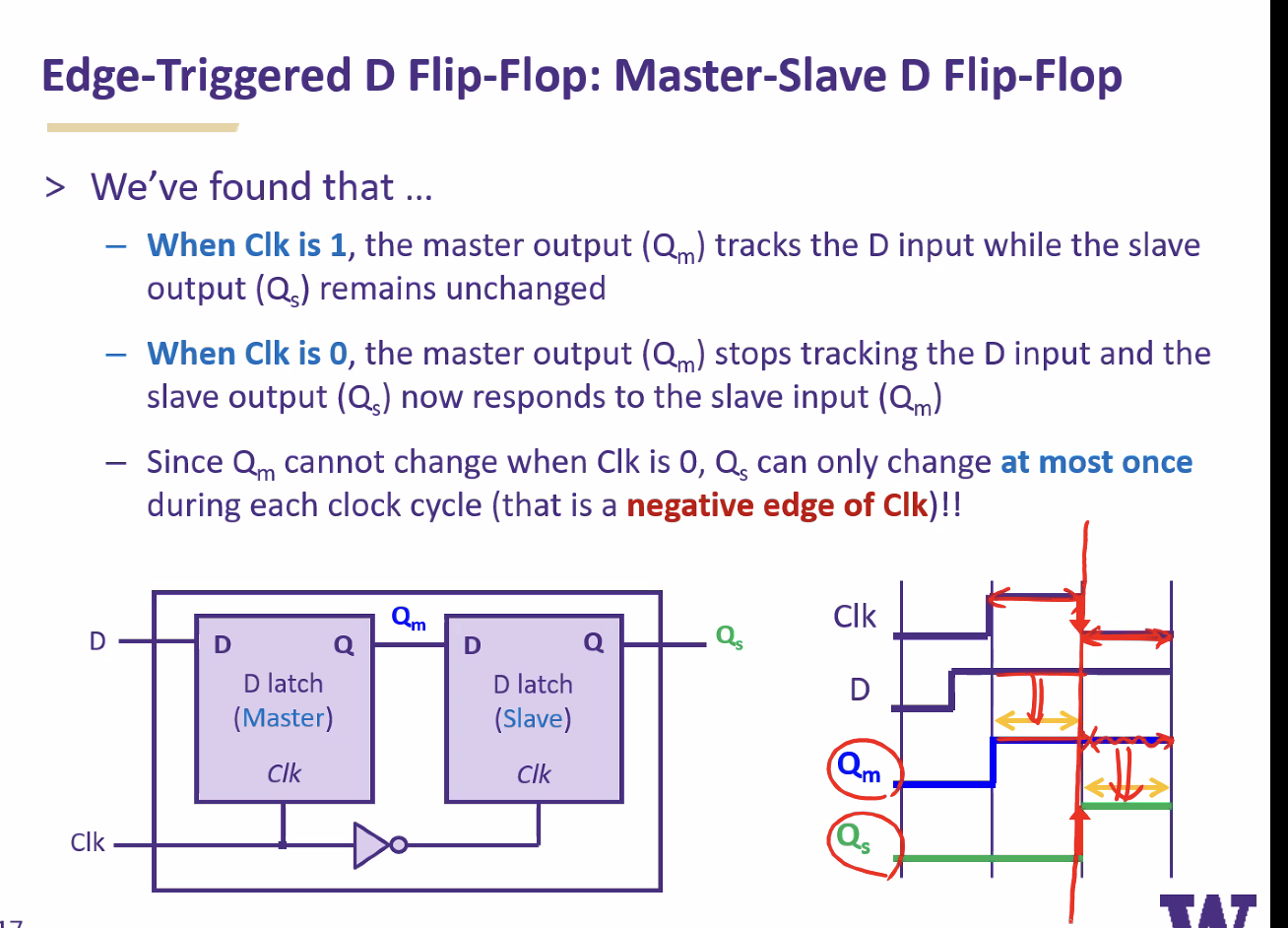

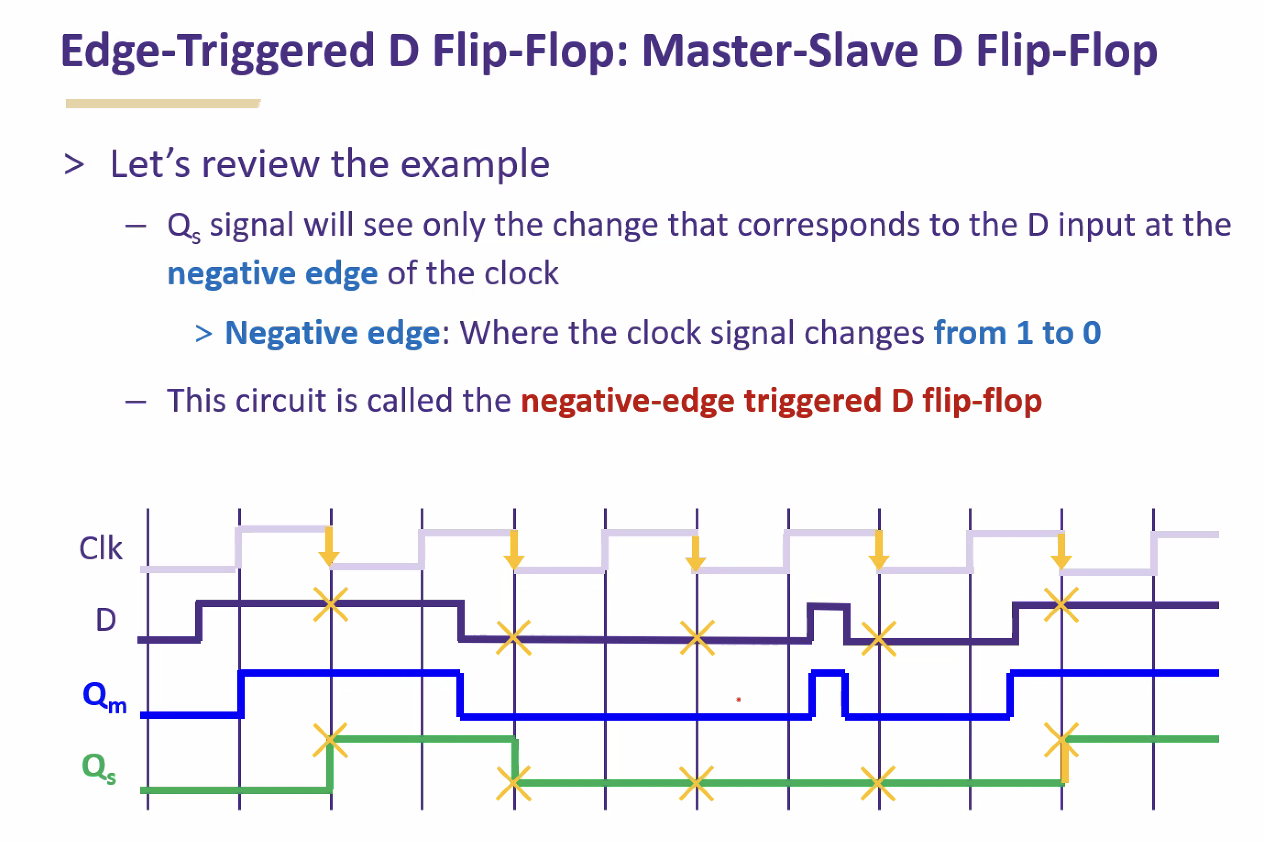

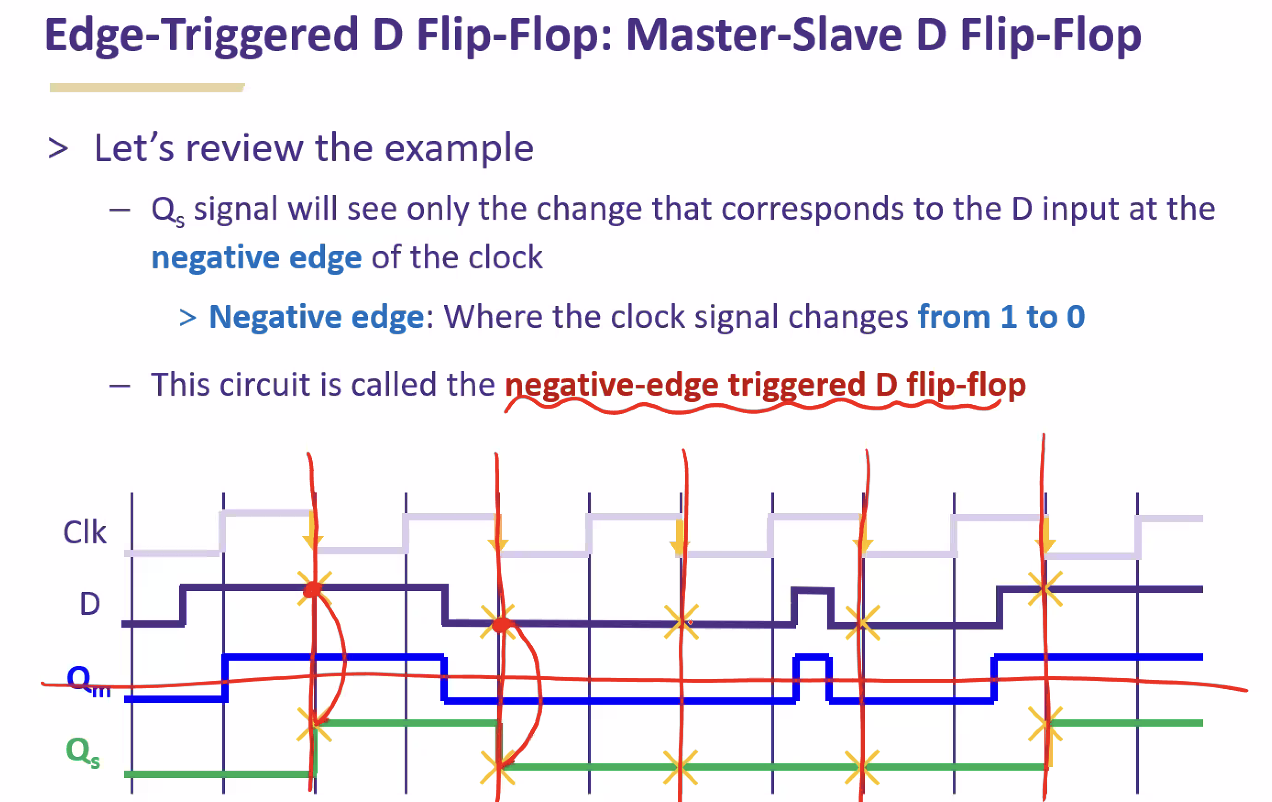

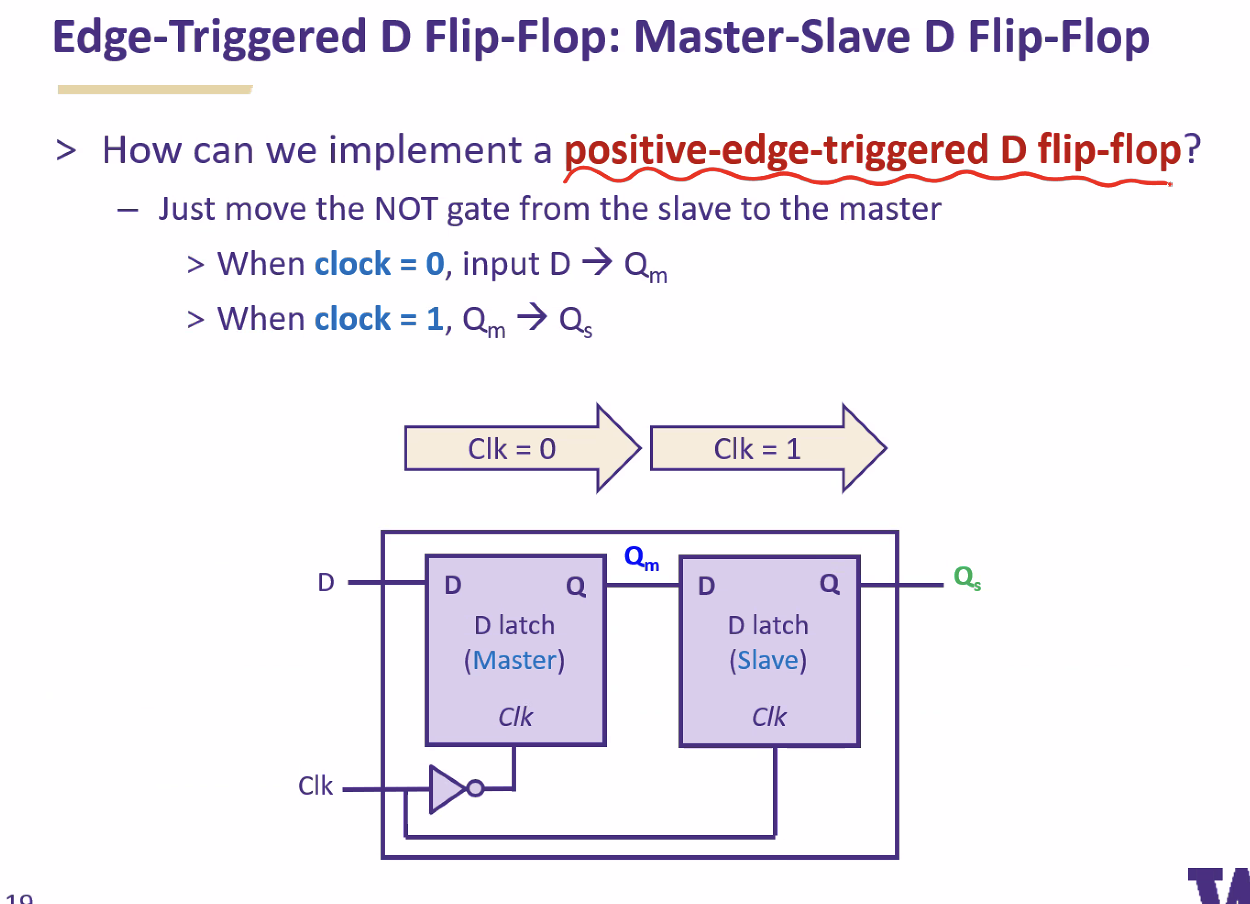

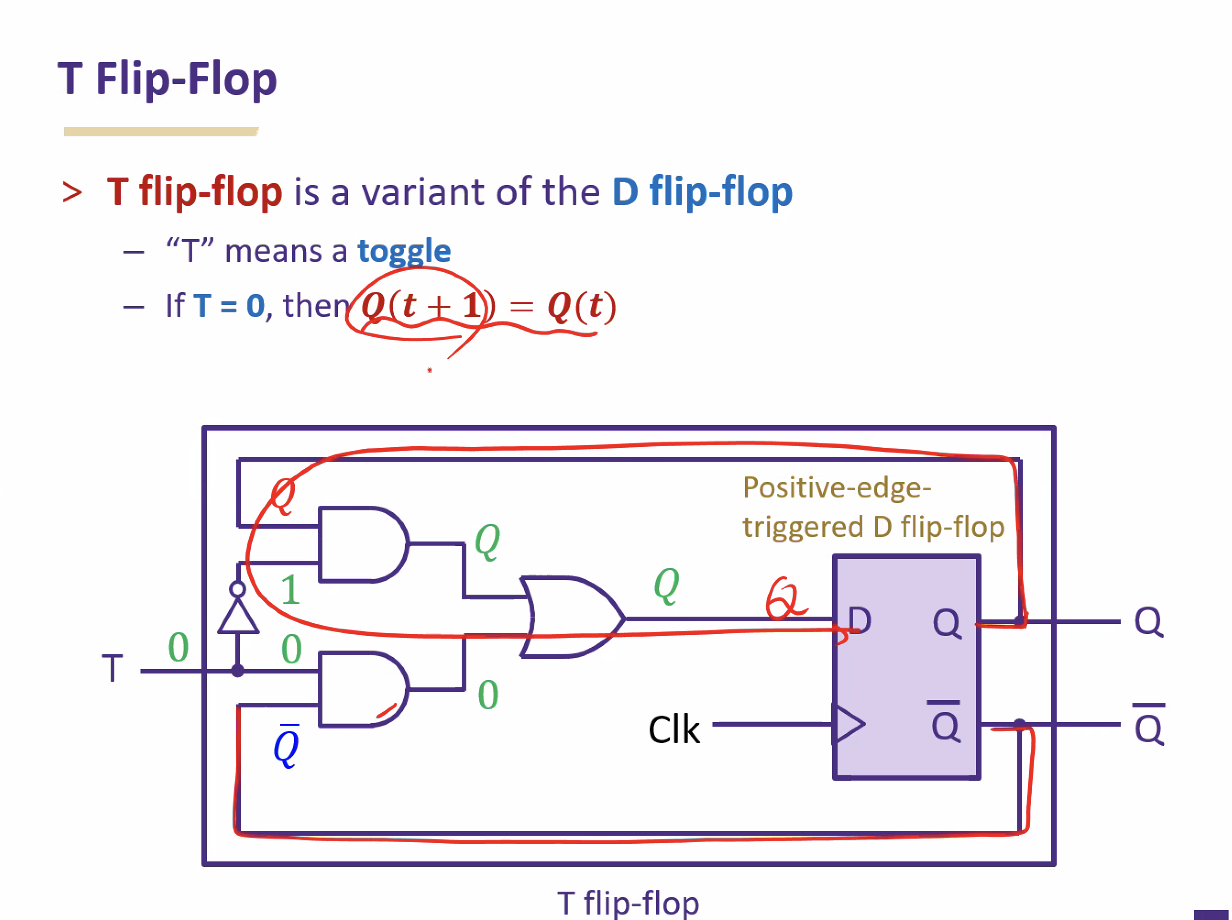

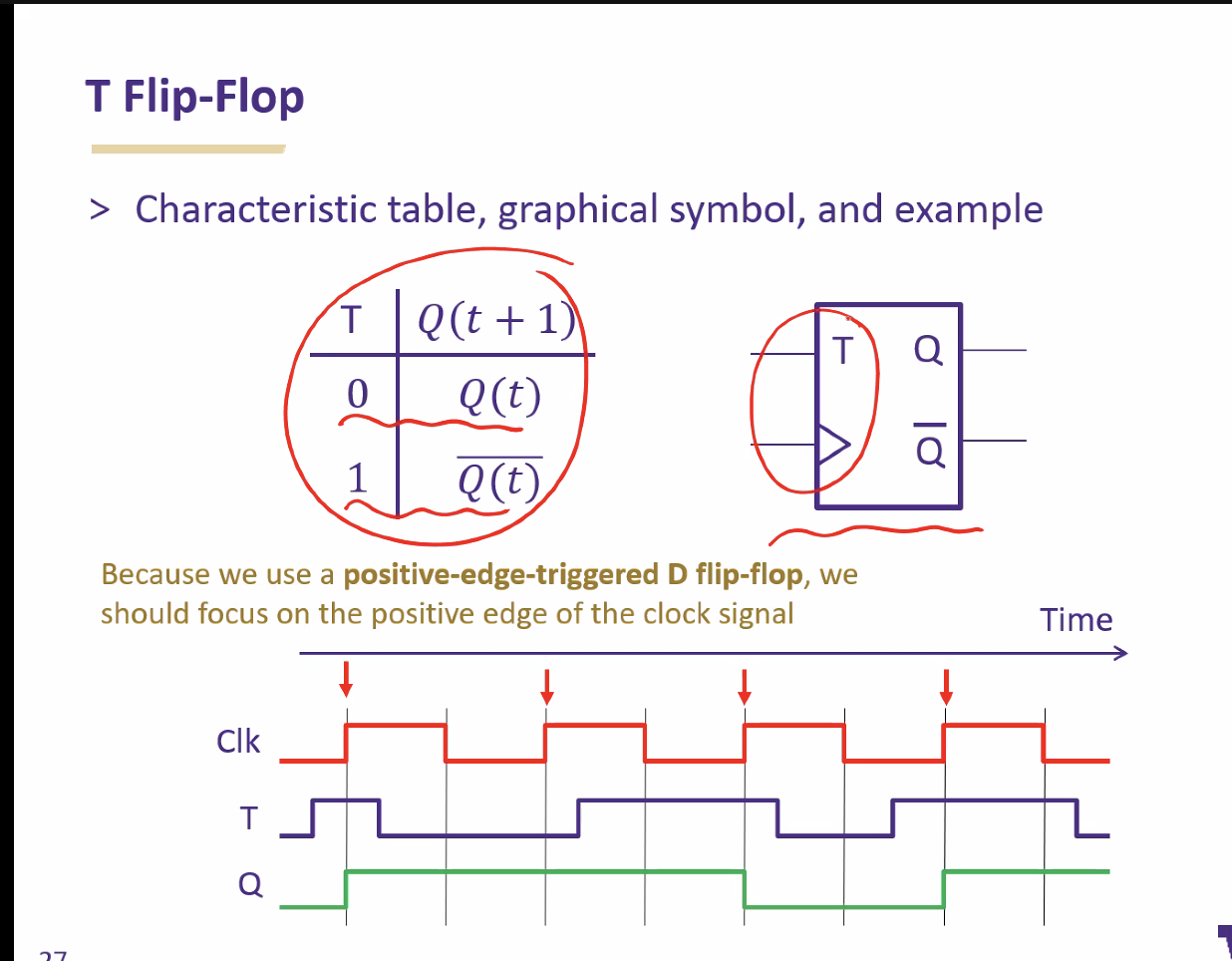

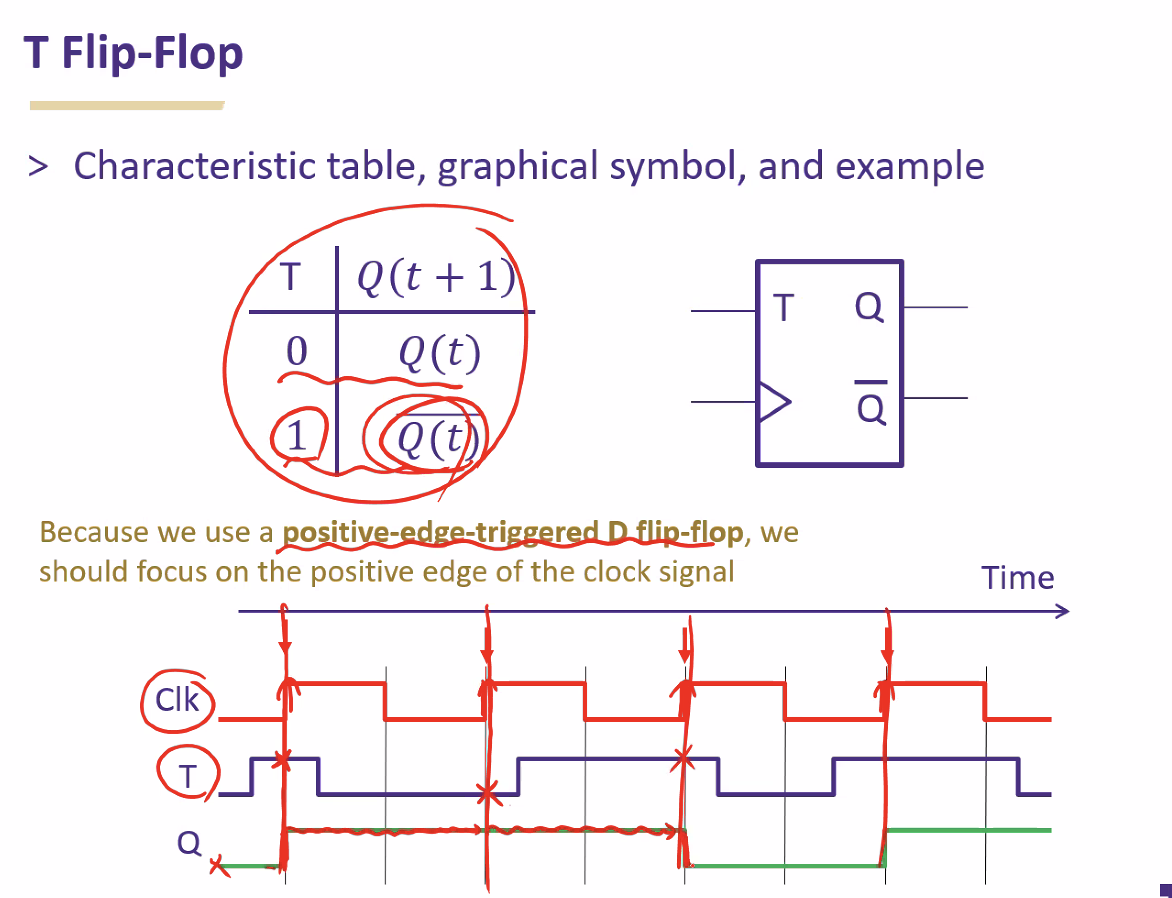

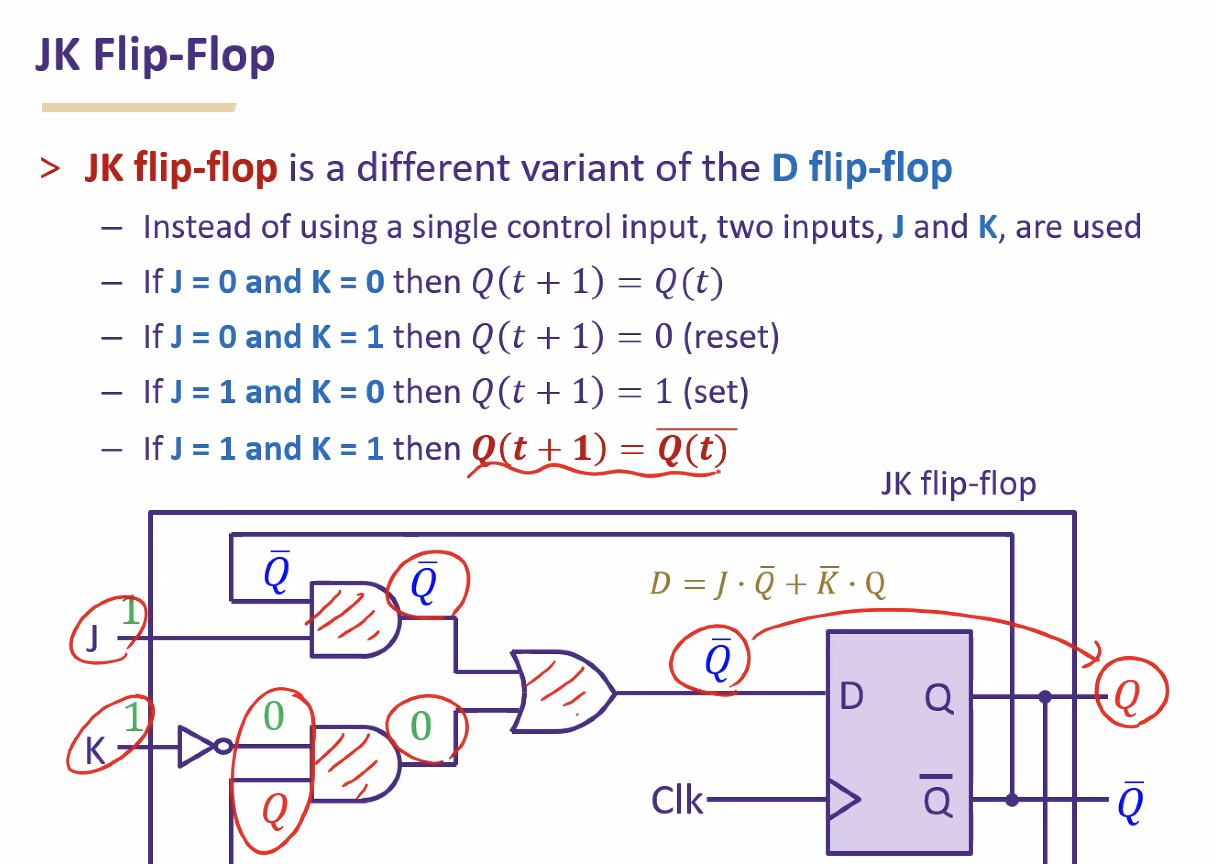

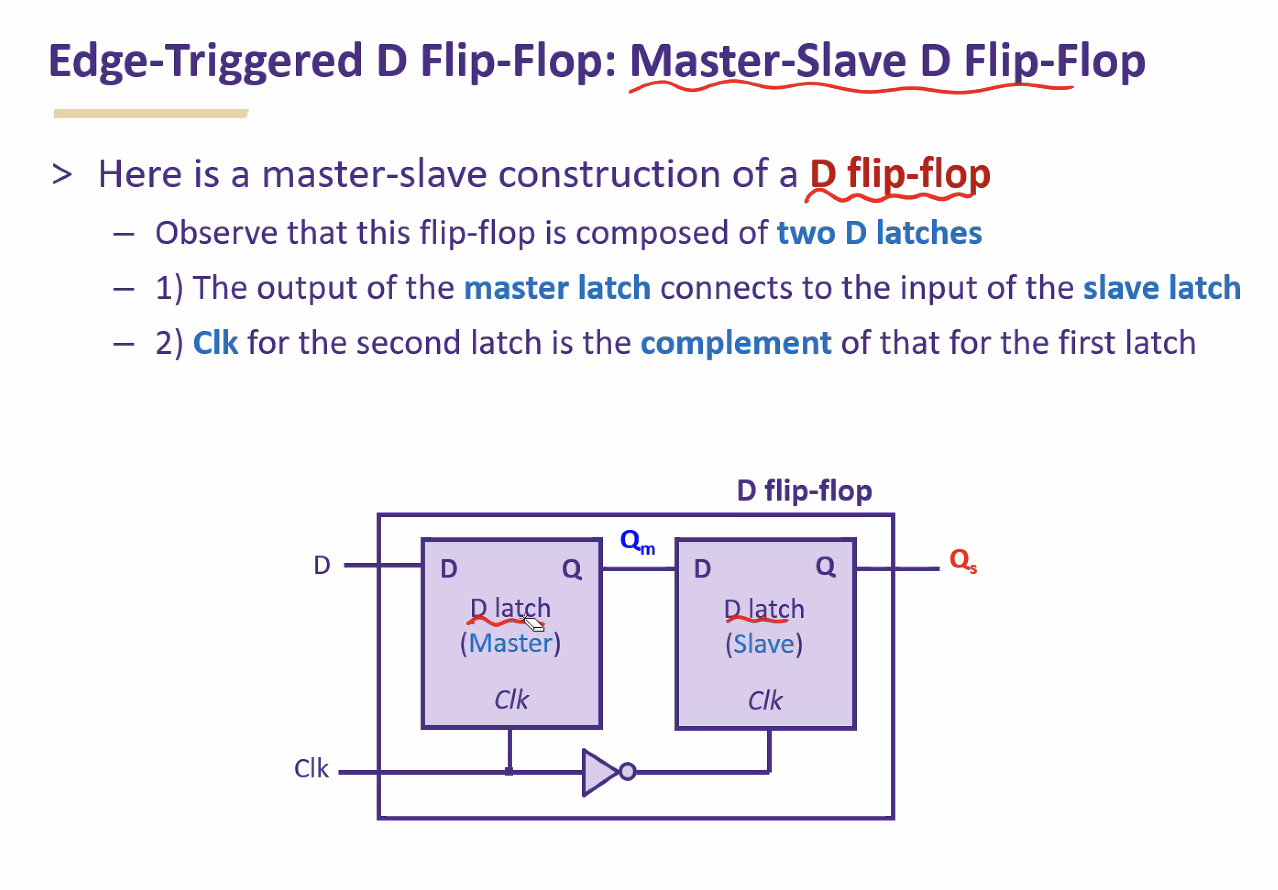

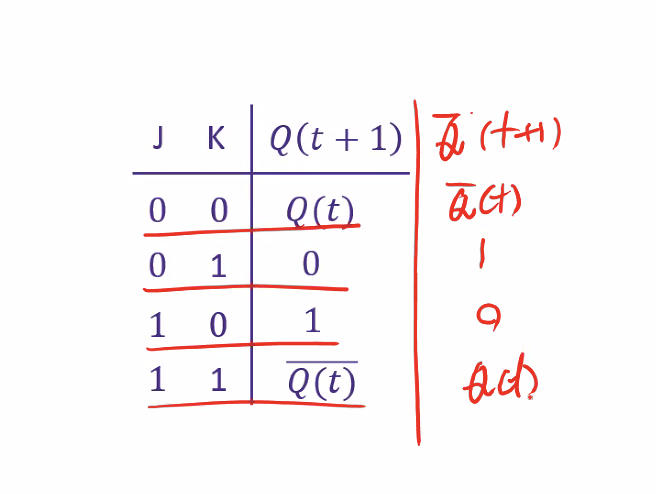

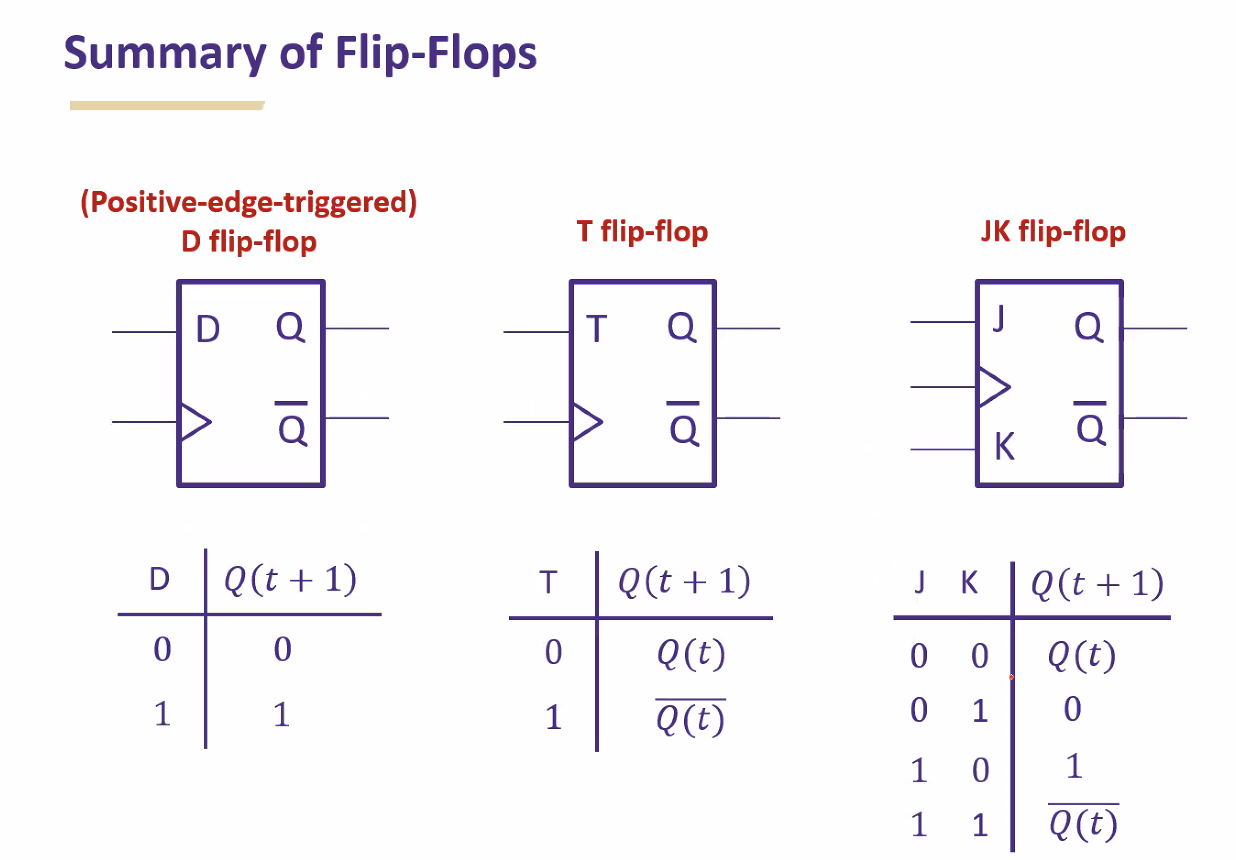

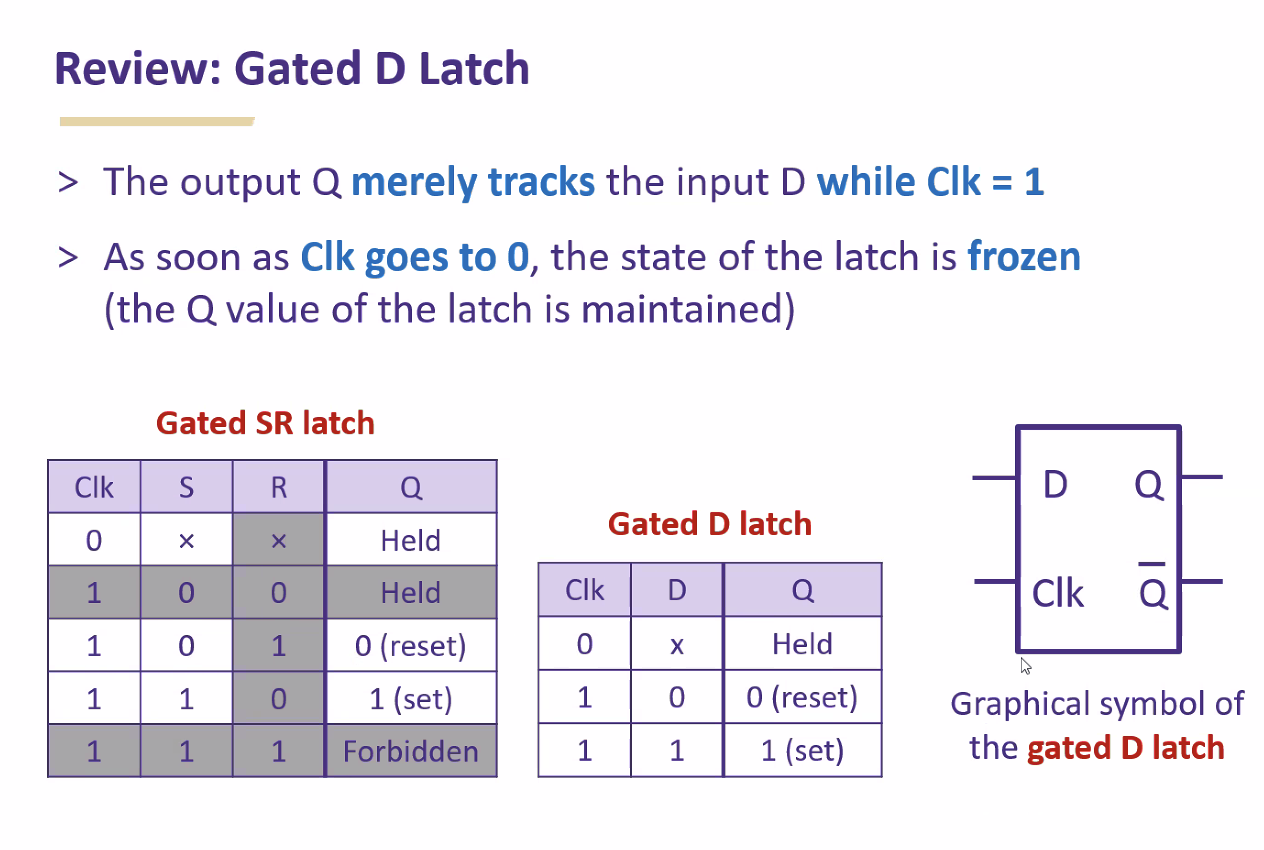

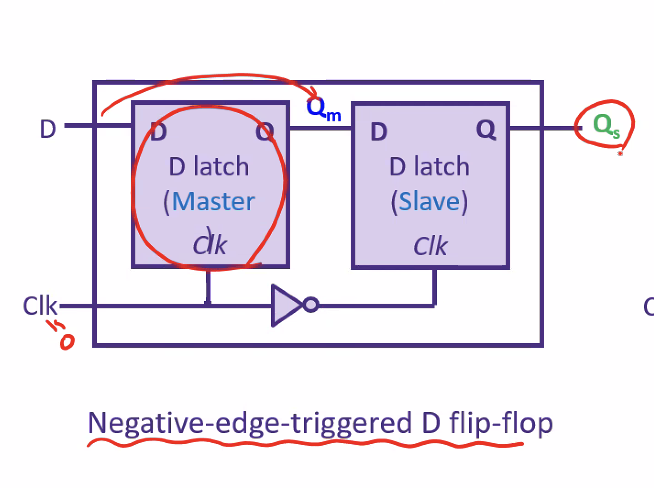

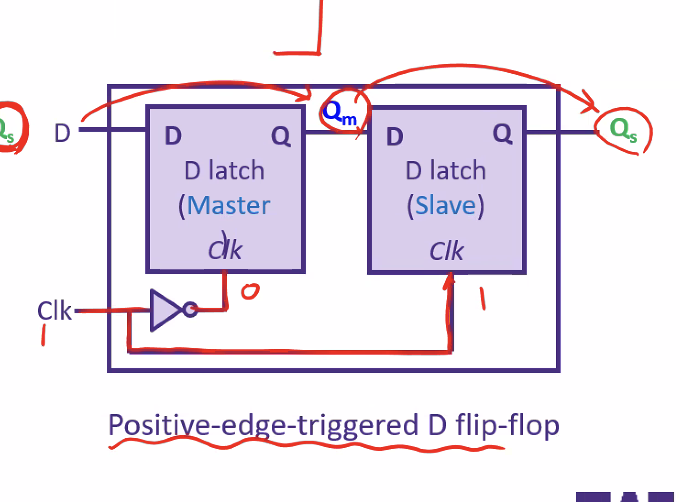

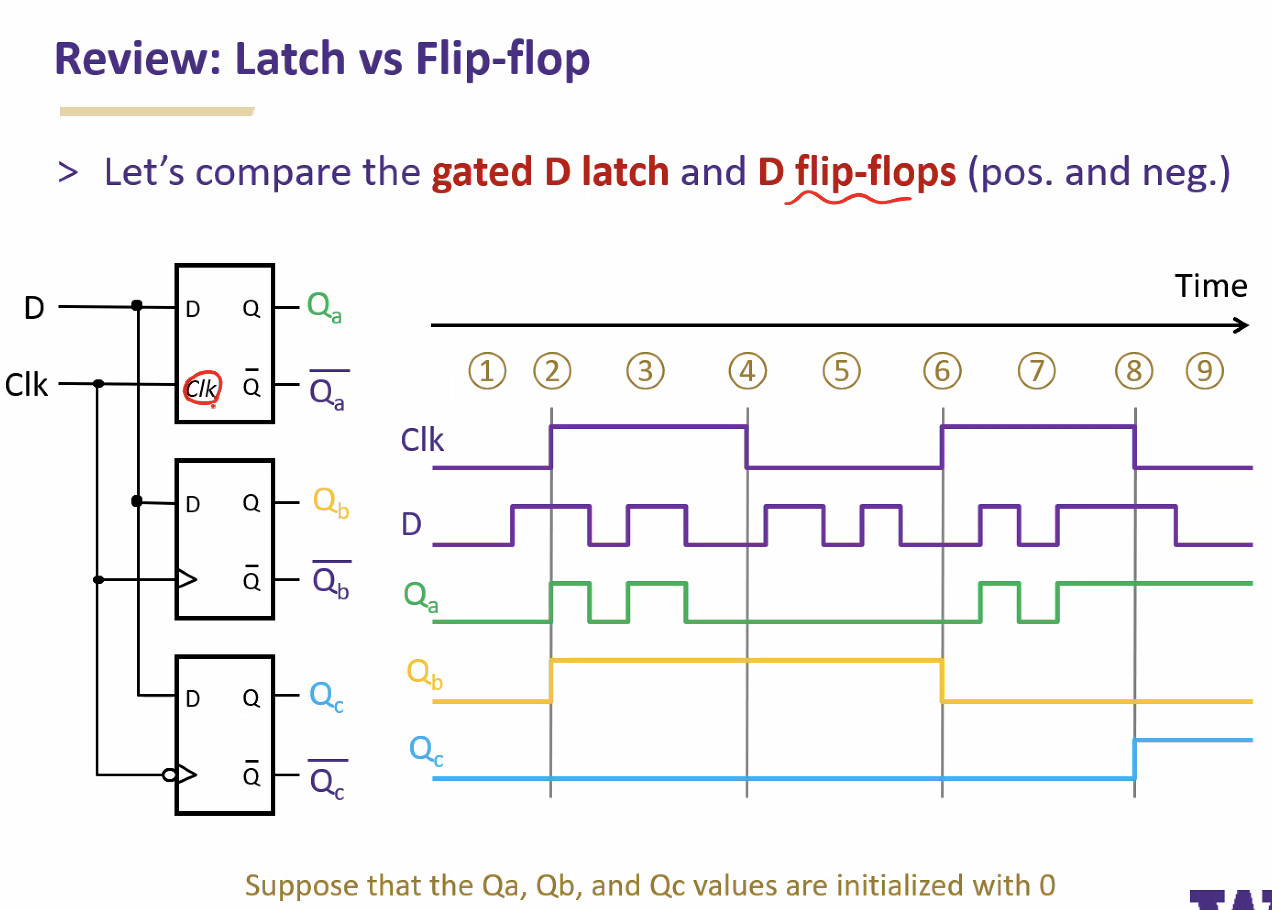

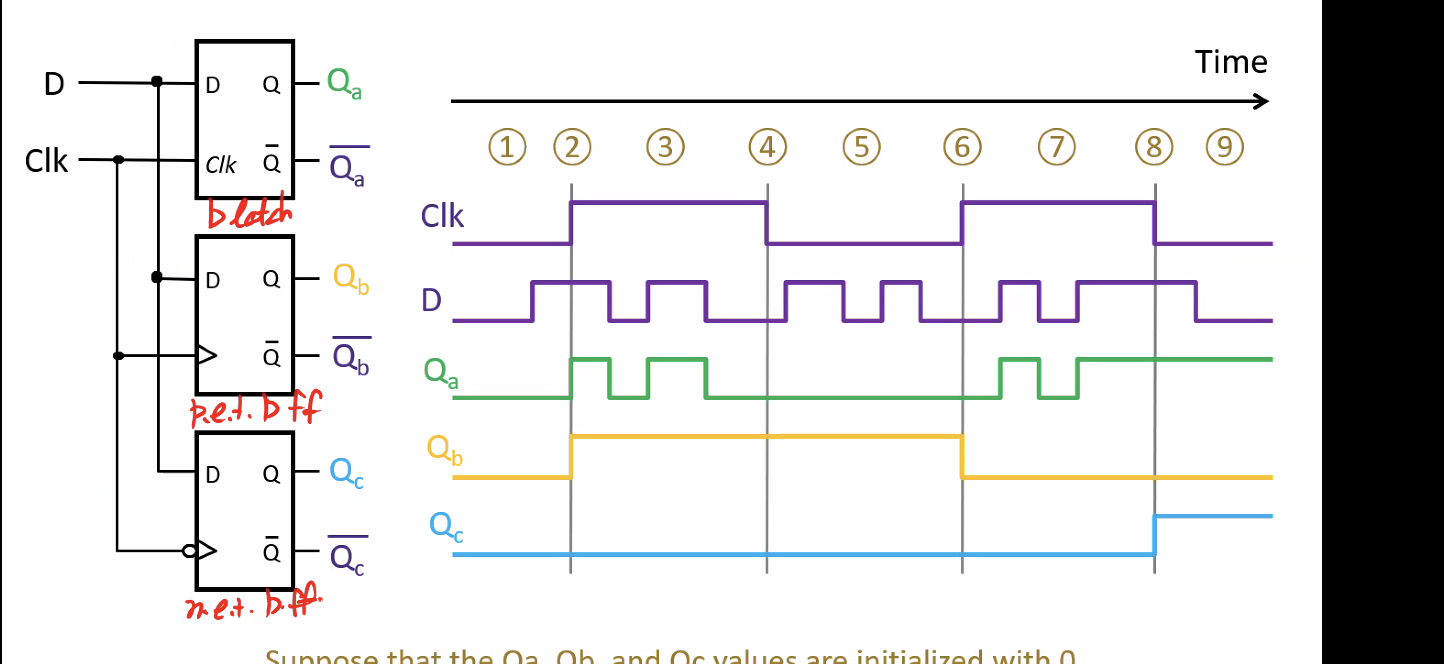

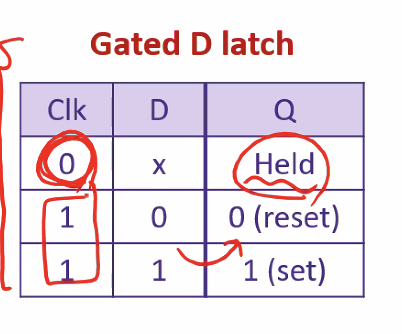

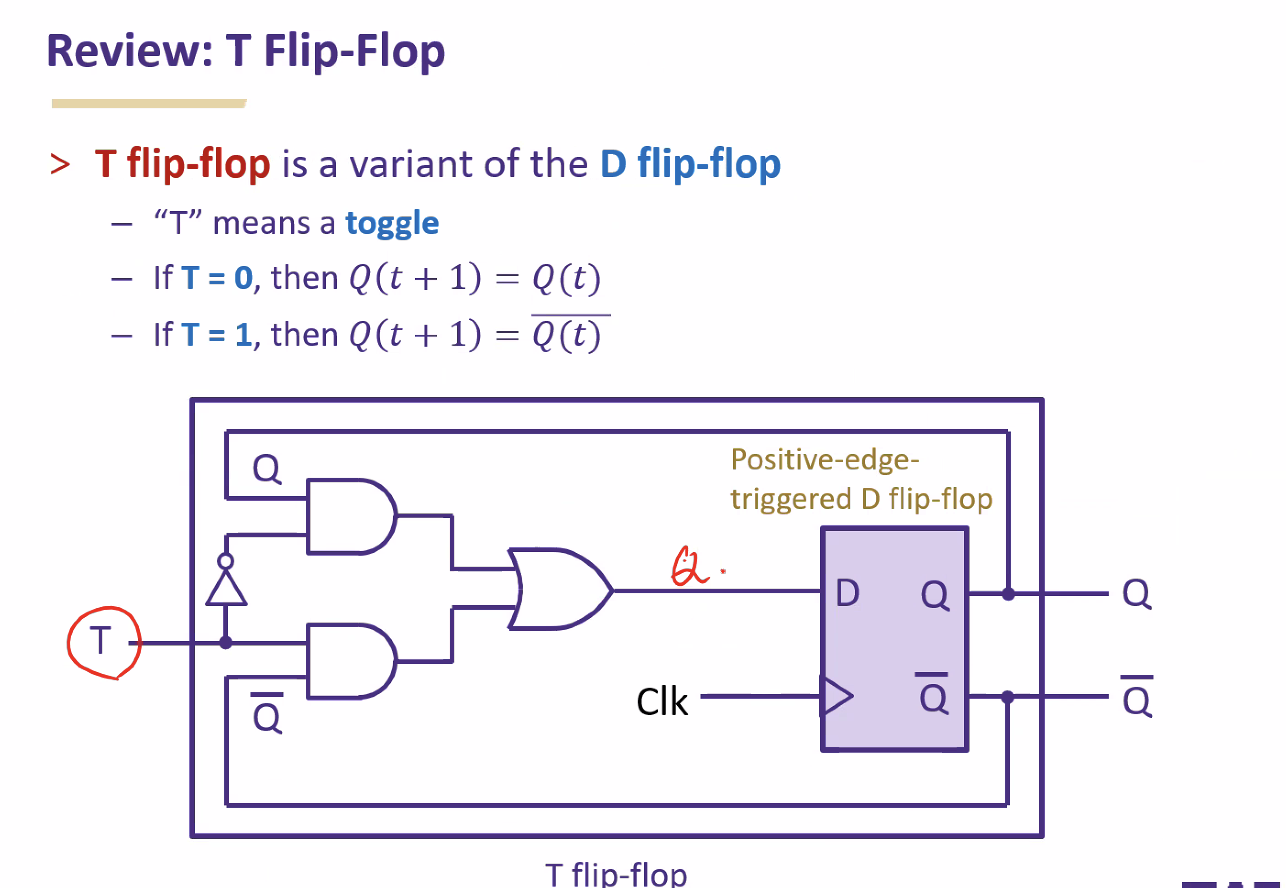

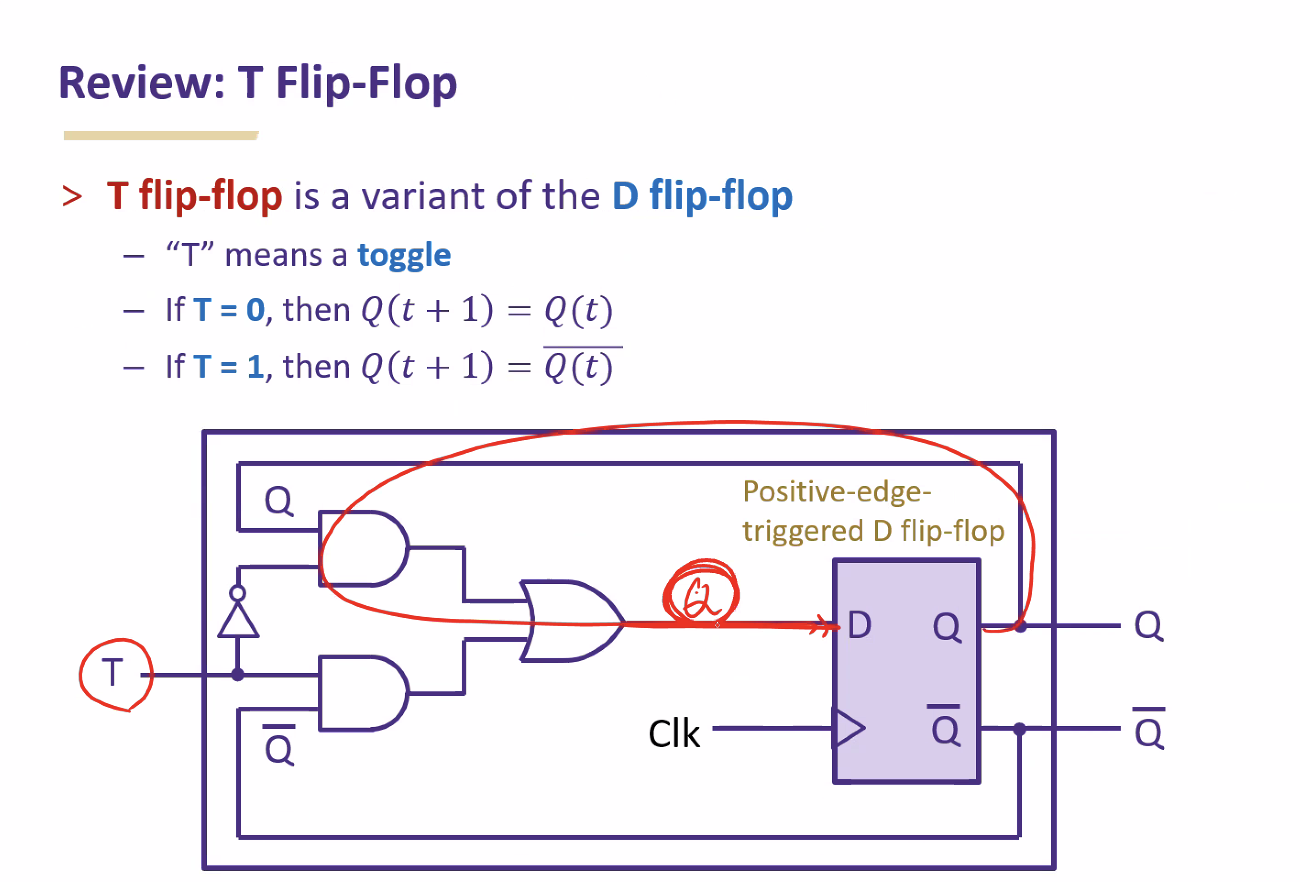

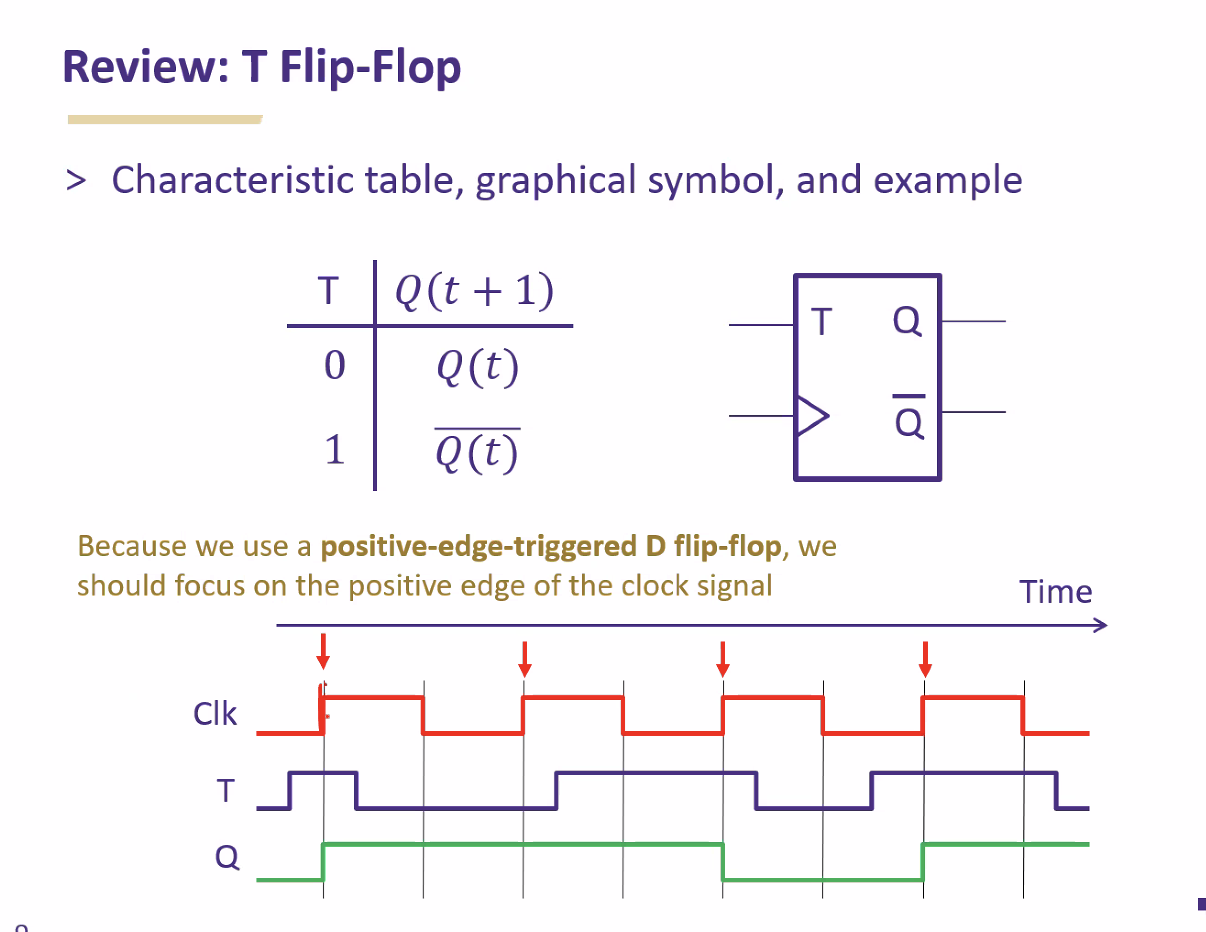

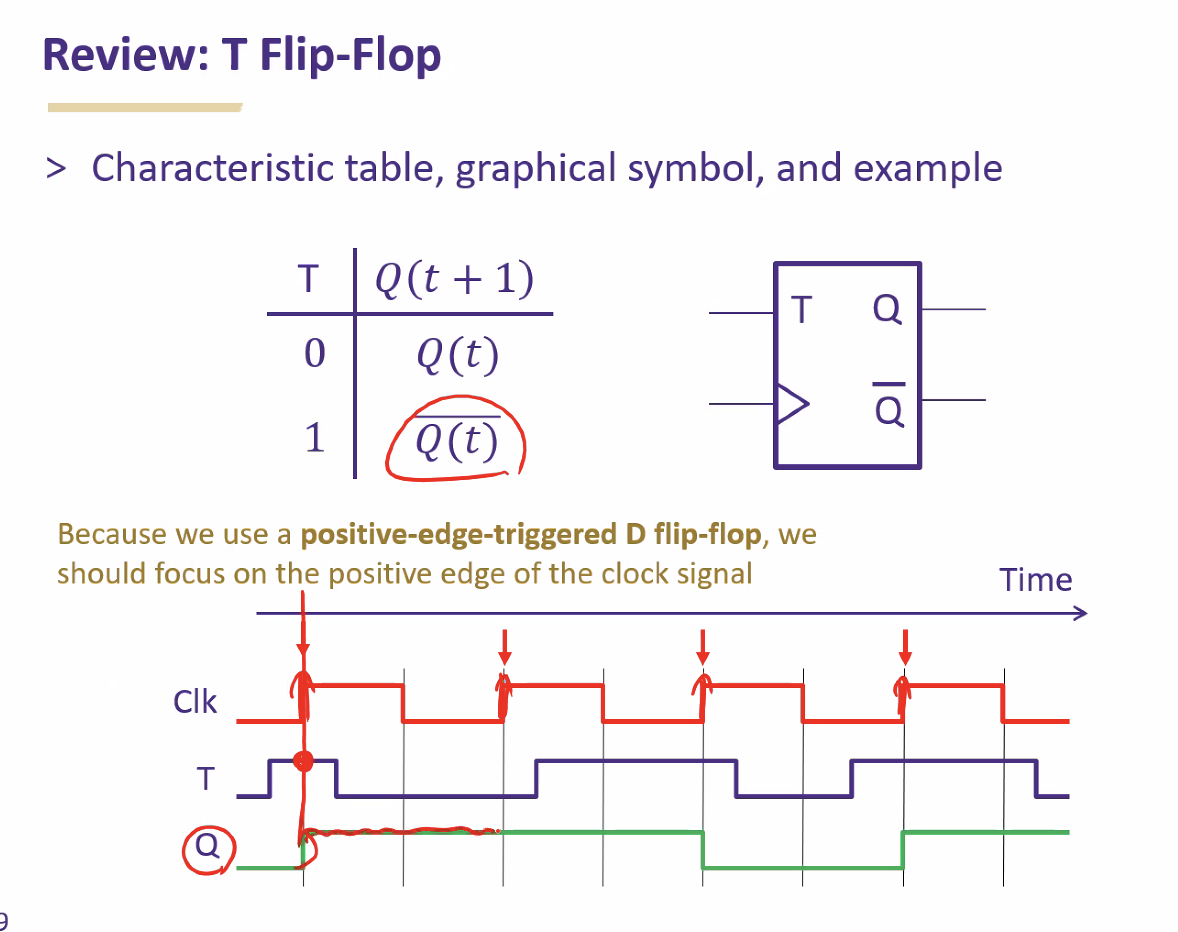

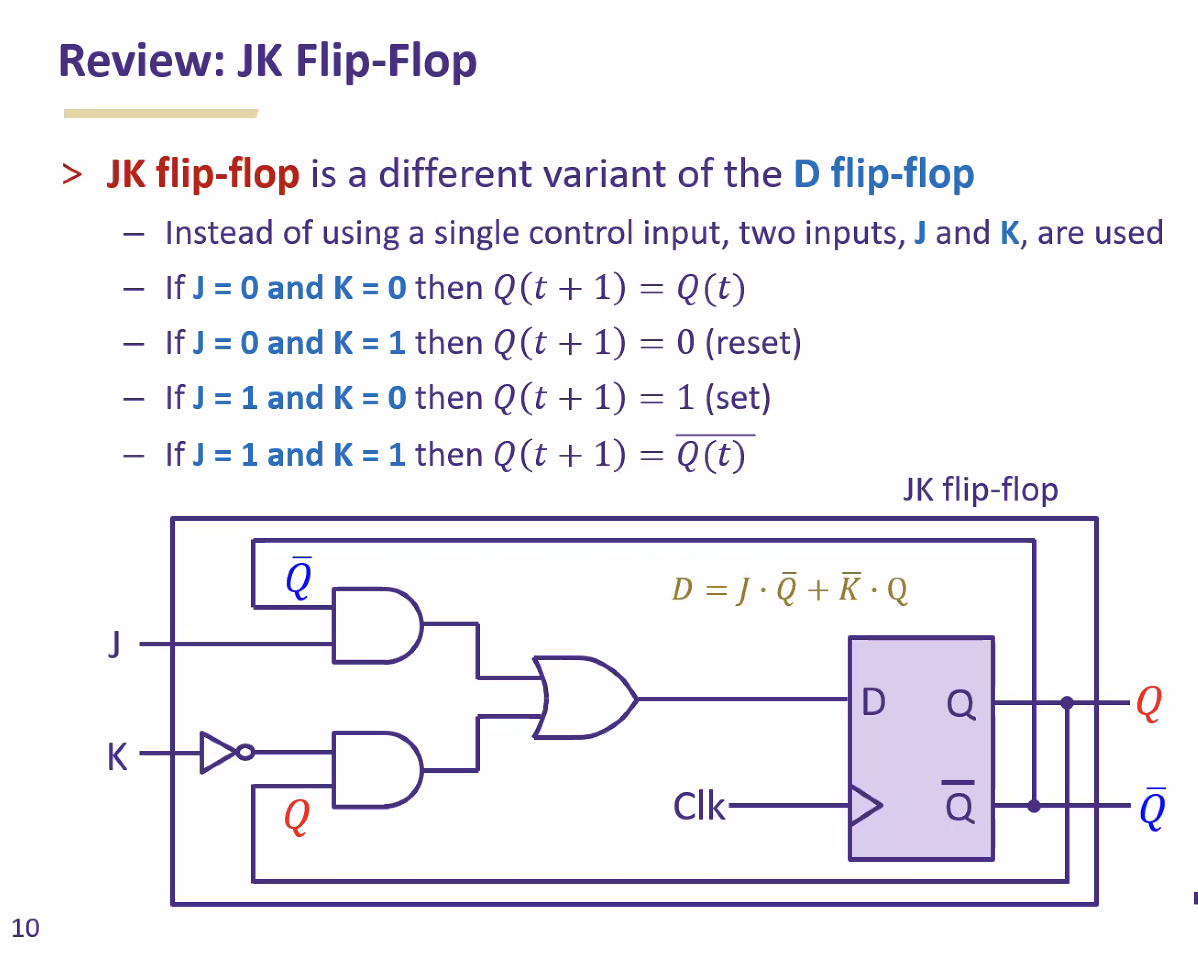

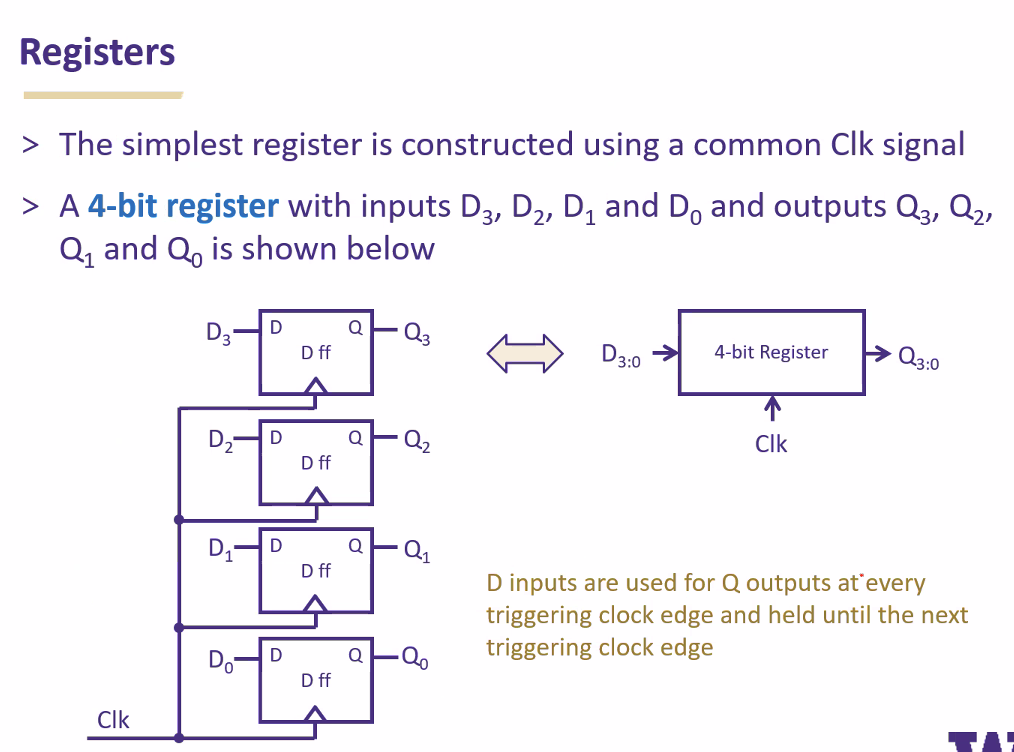

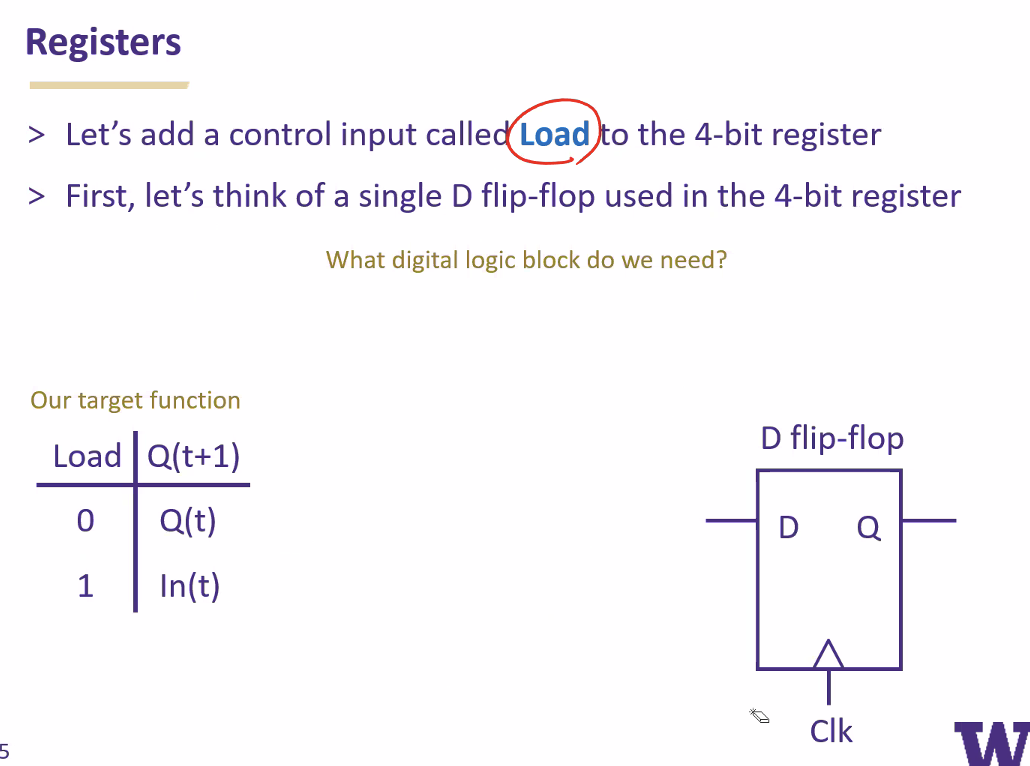

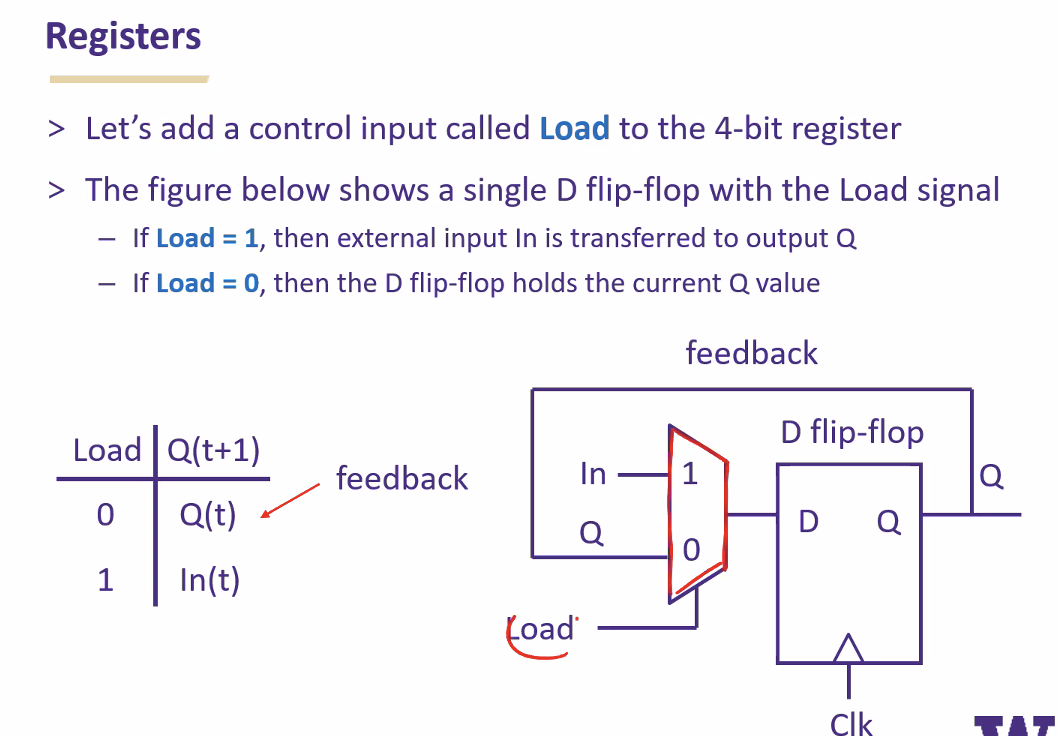

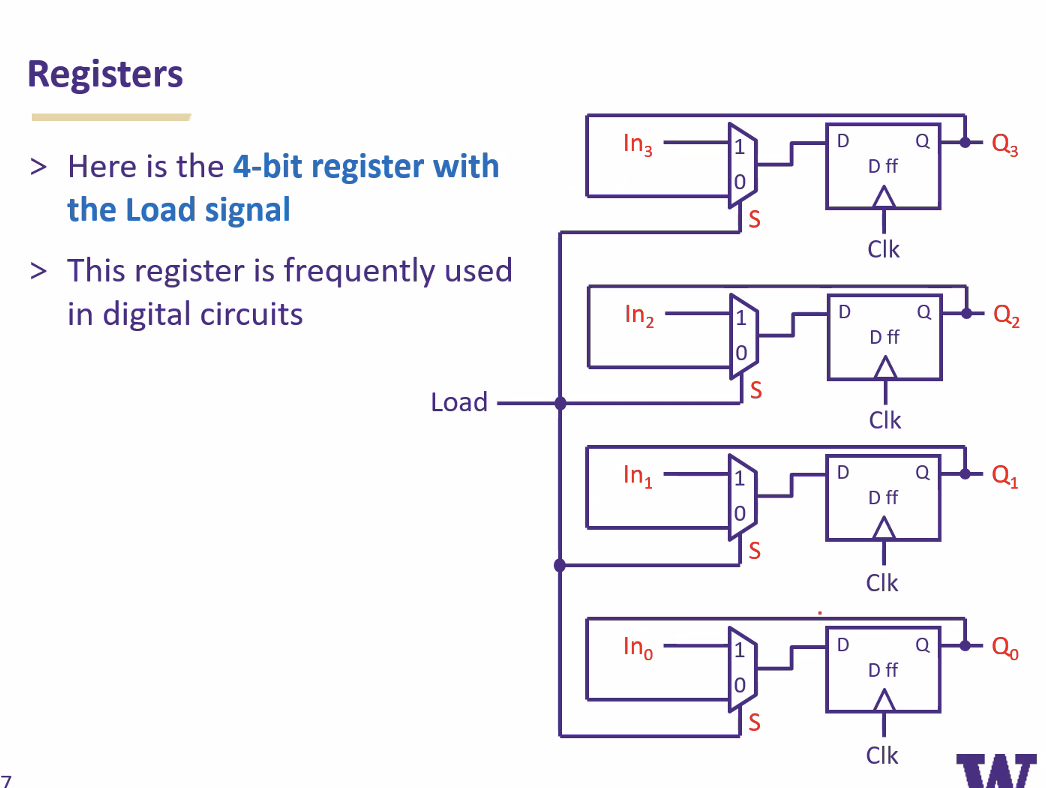

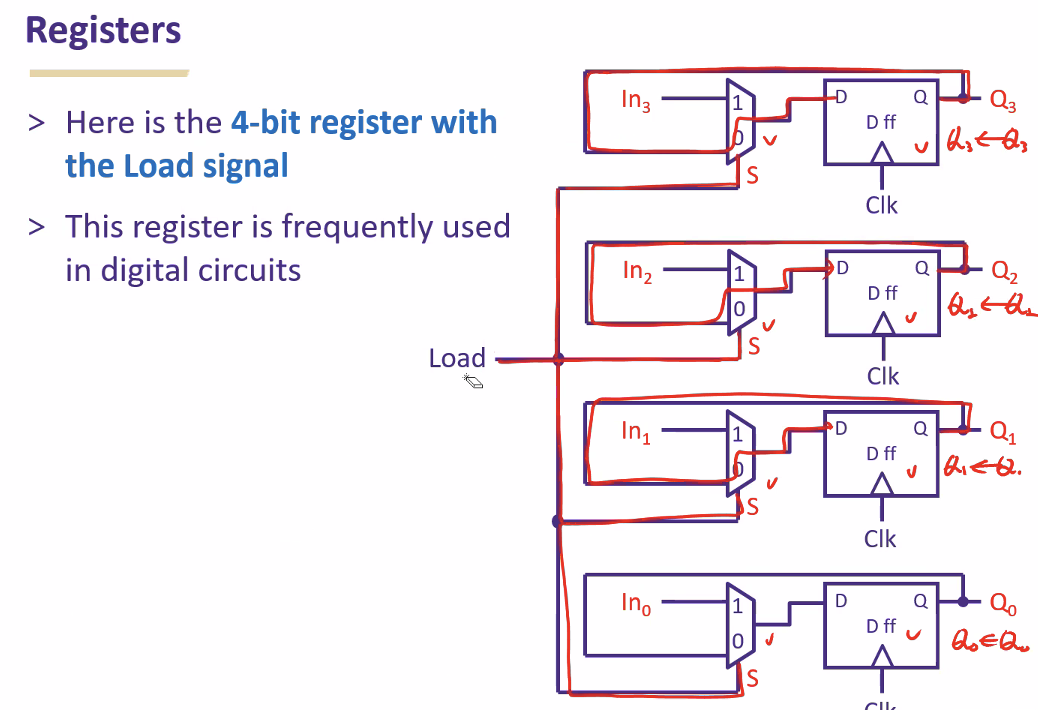

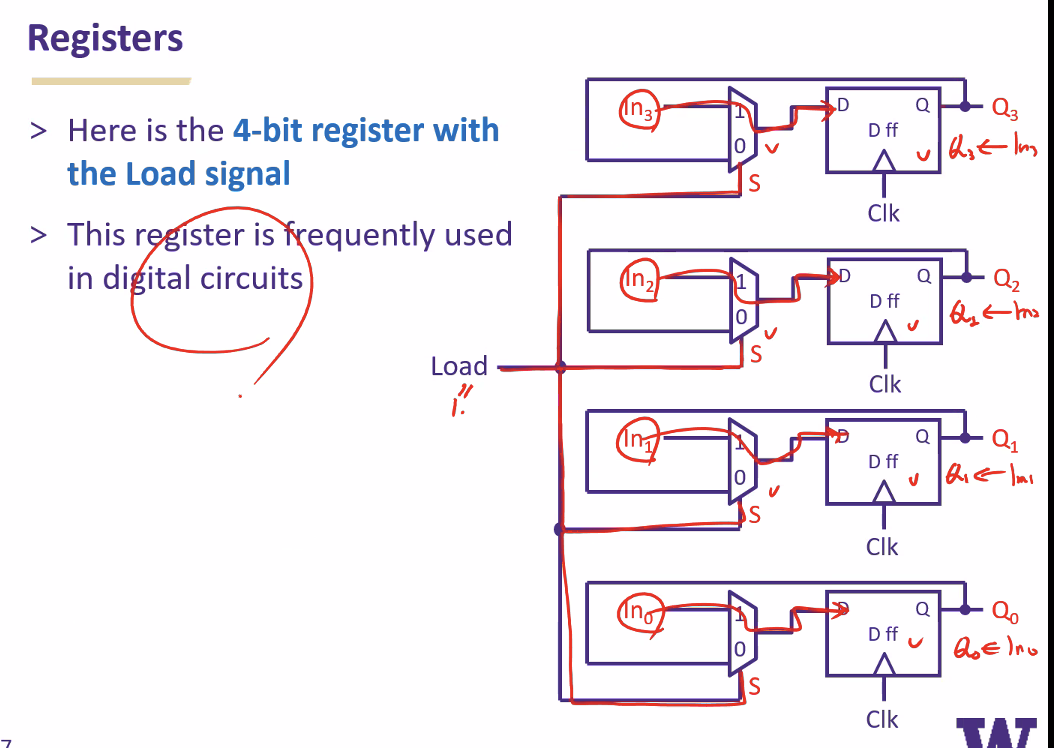

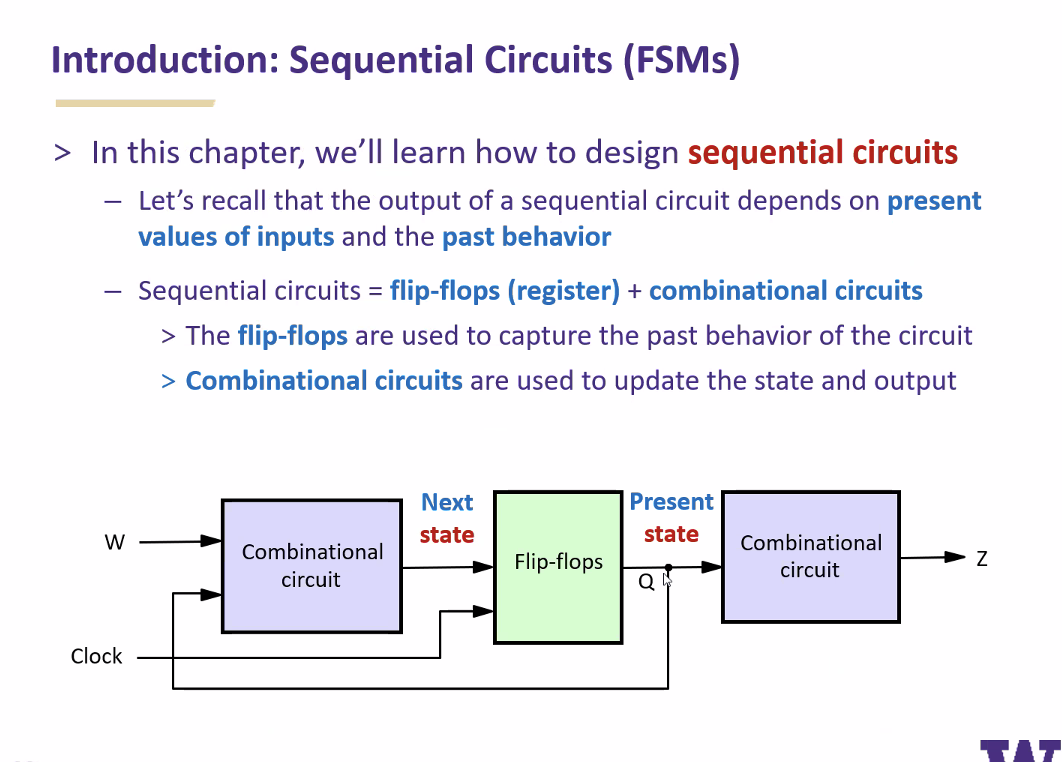

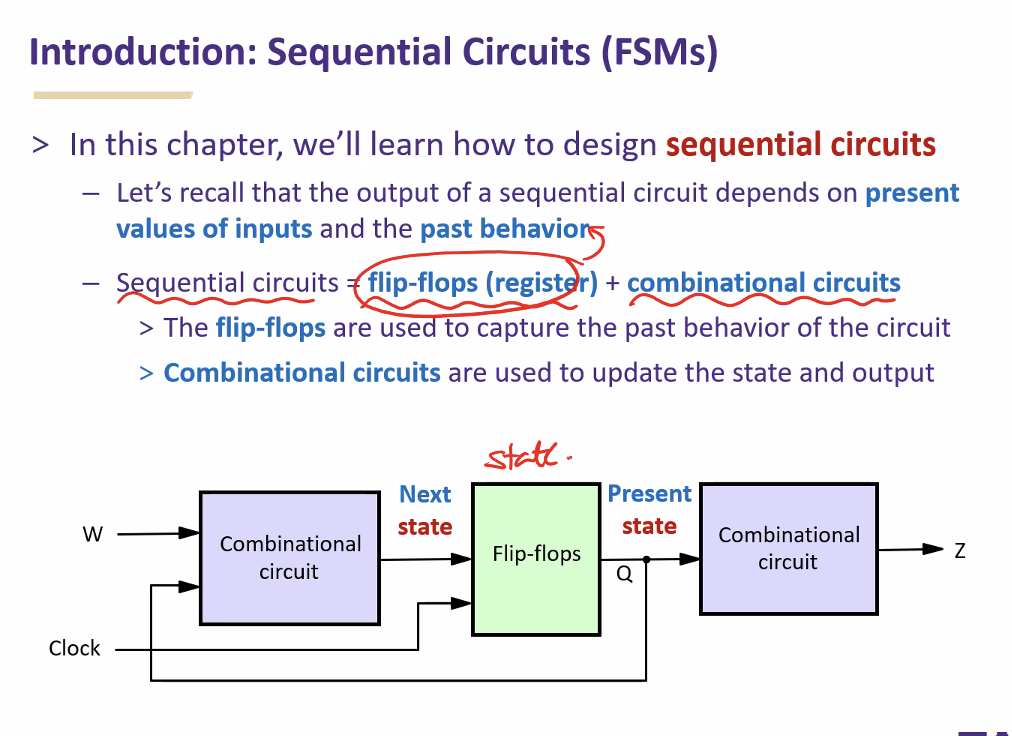

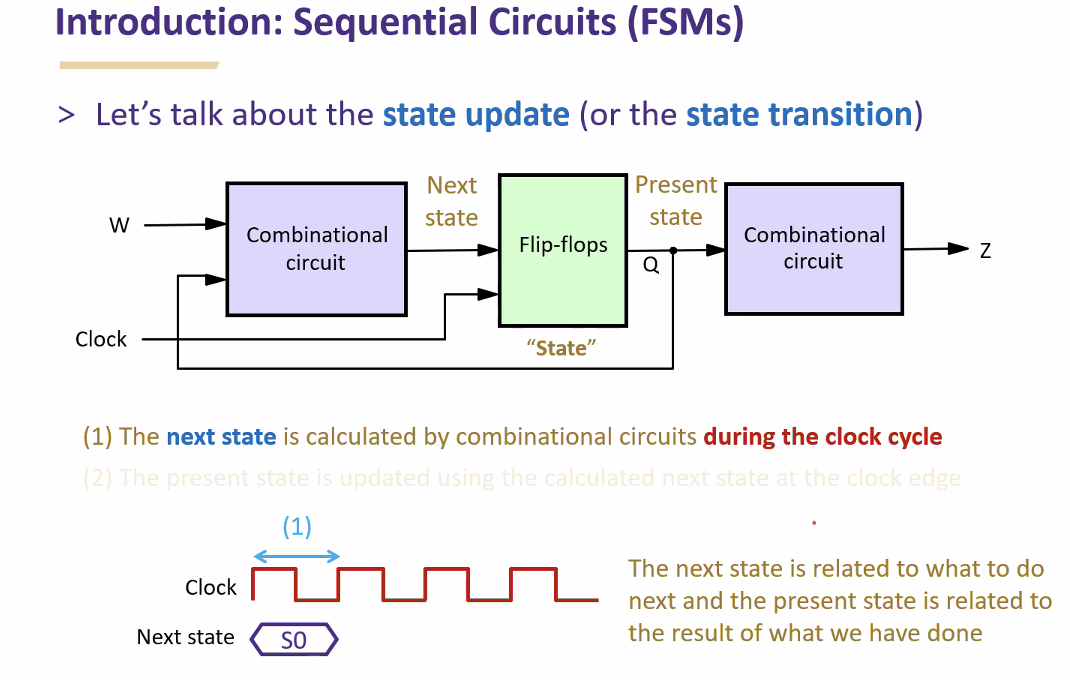

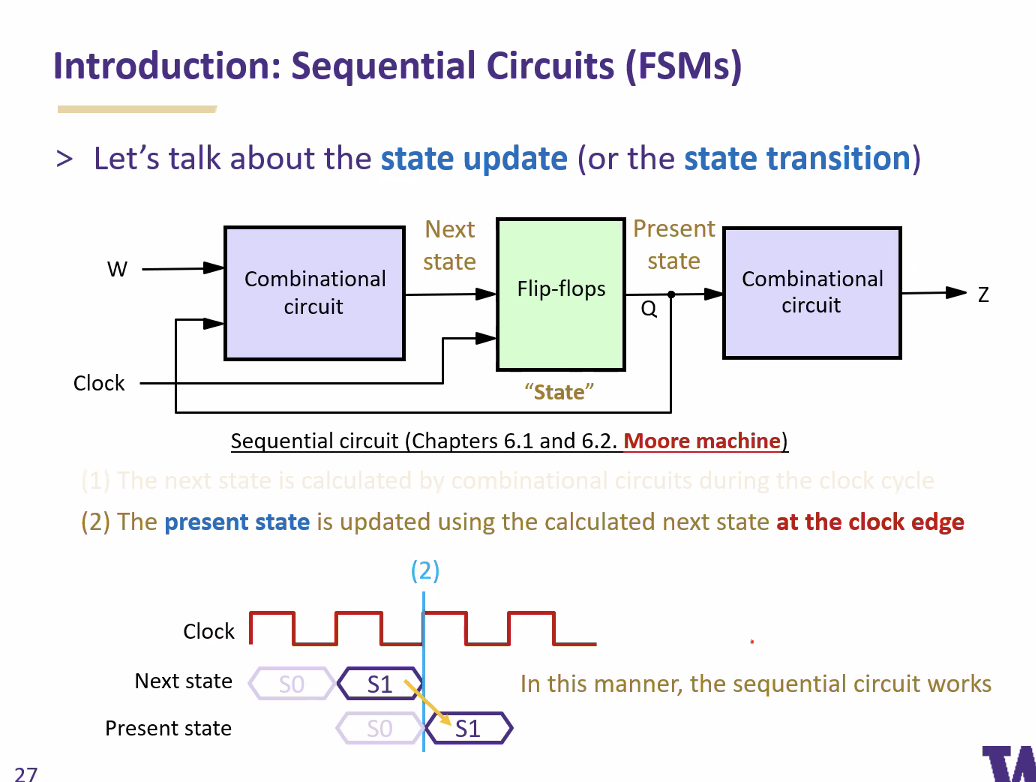

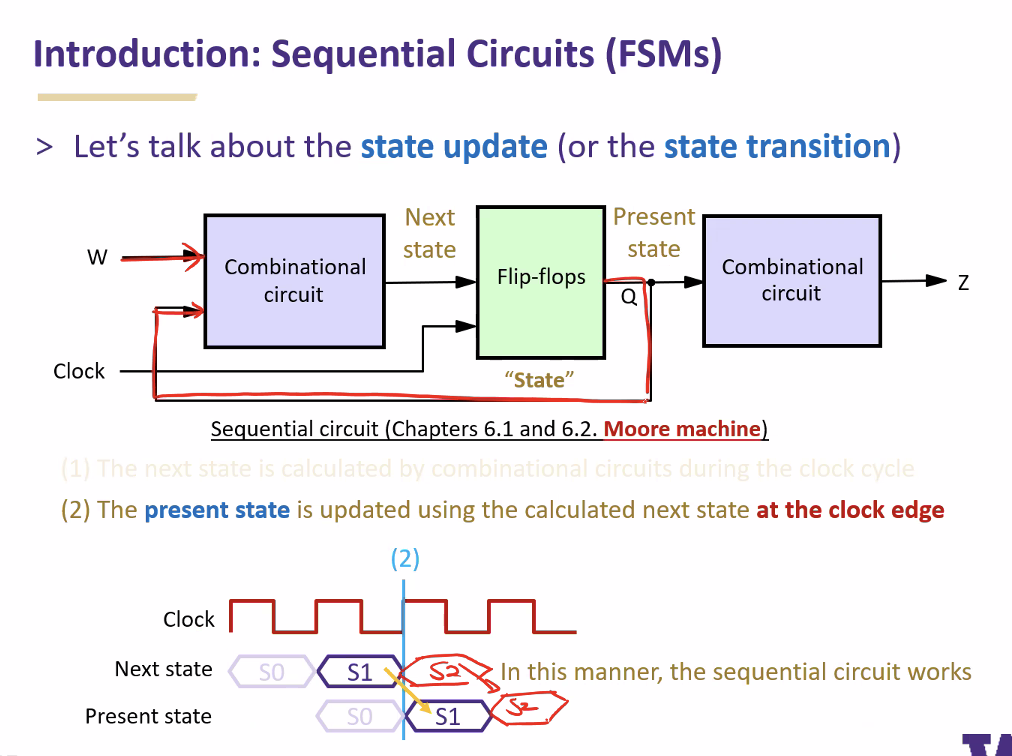

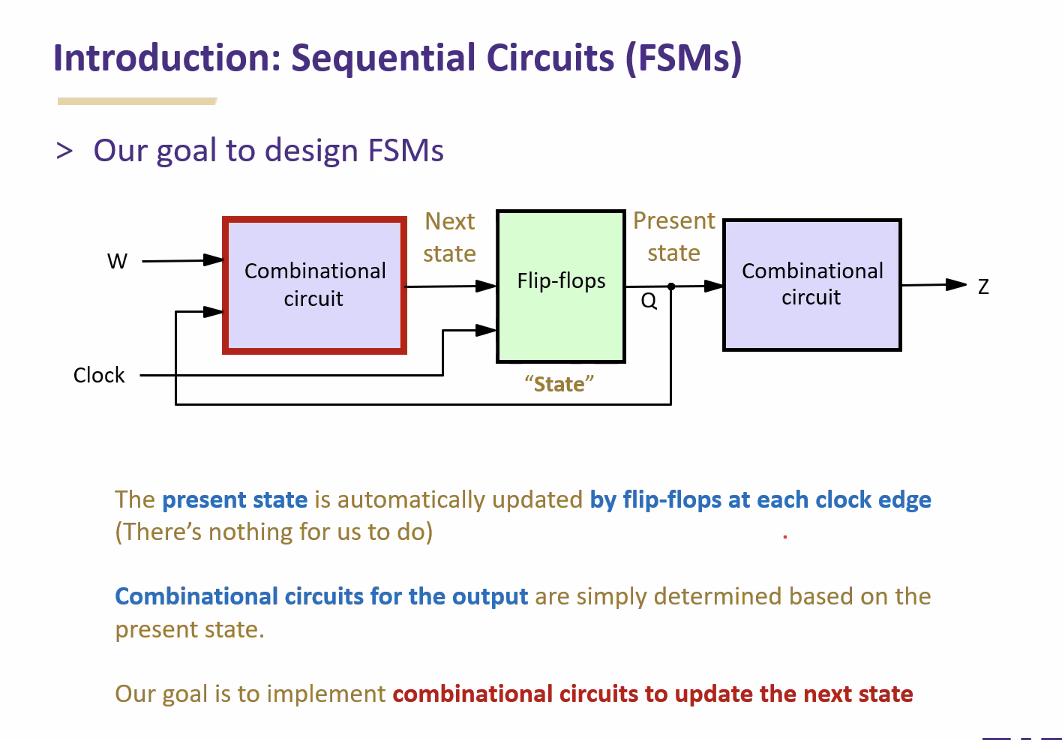

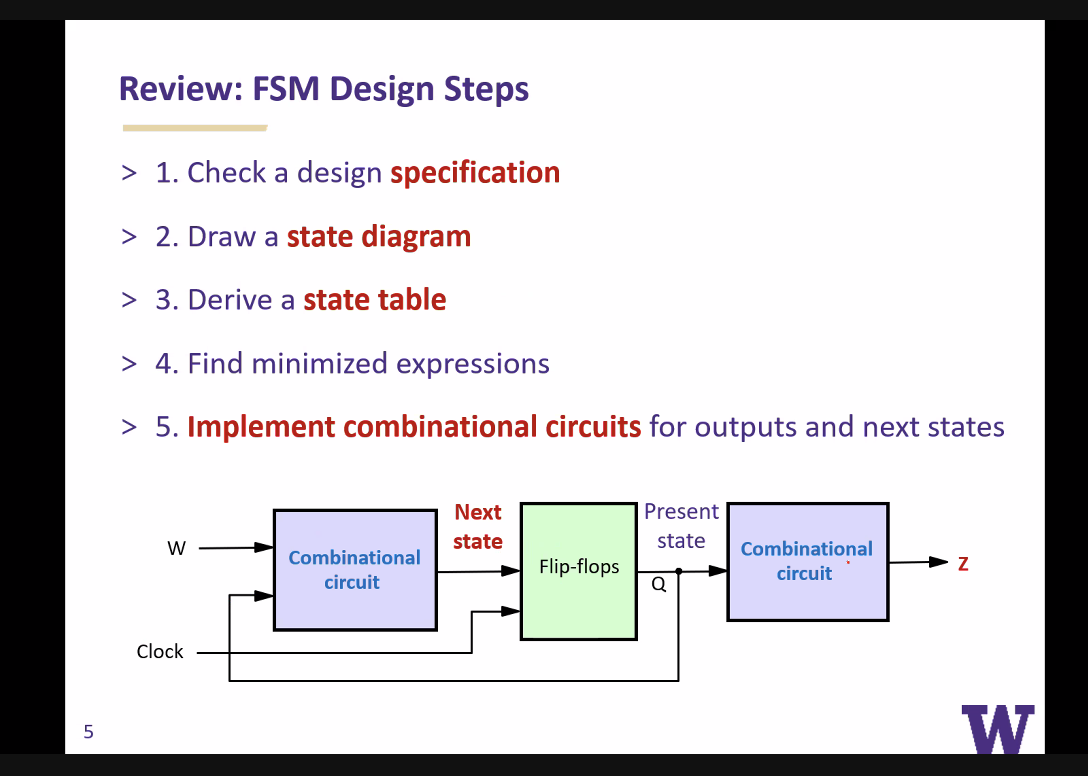

Can only update values at clock edges

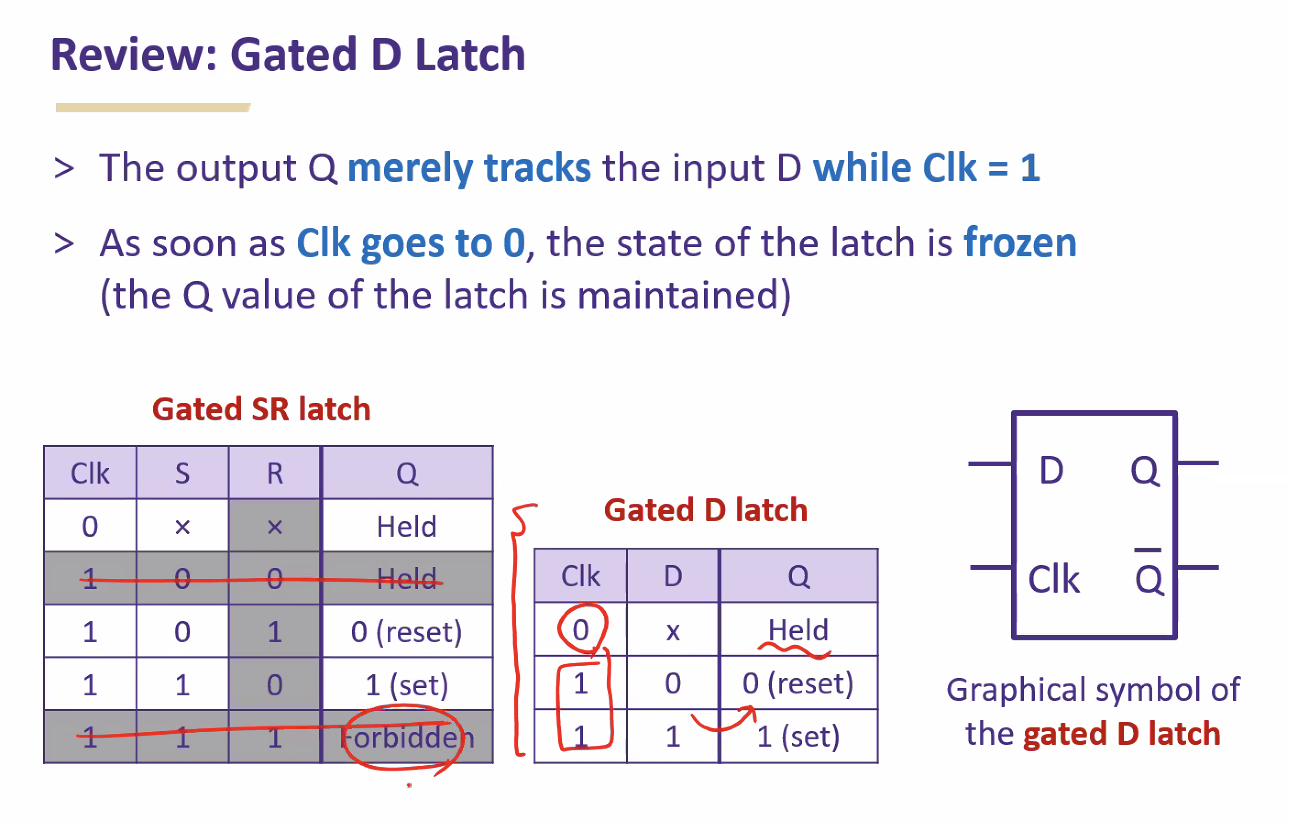

clk is just latch

bubble is negative edge d flip flop

triangle is positive edge d flipflop

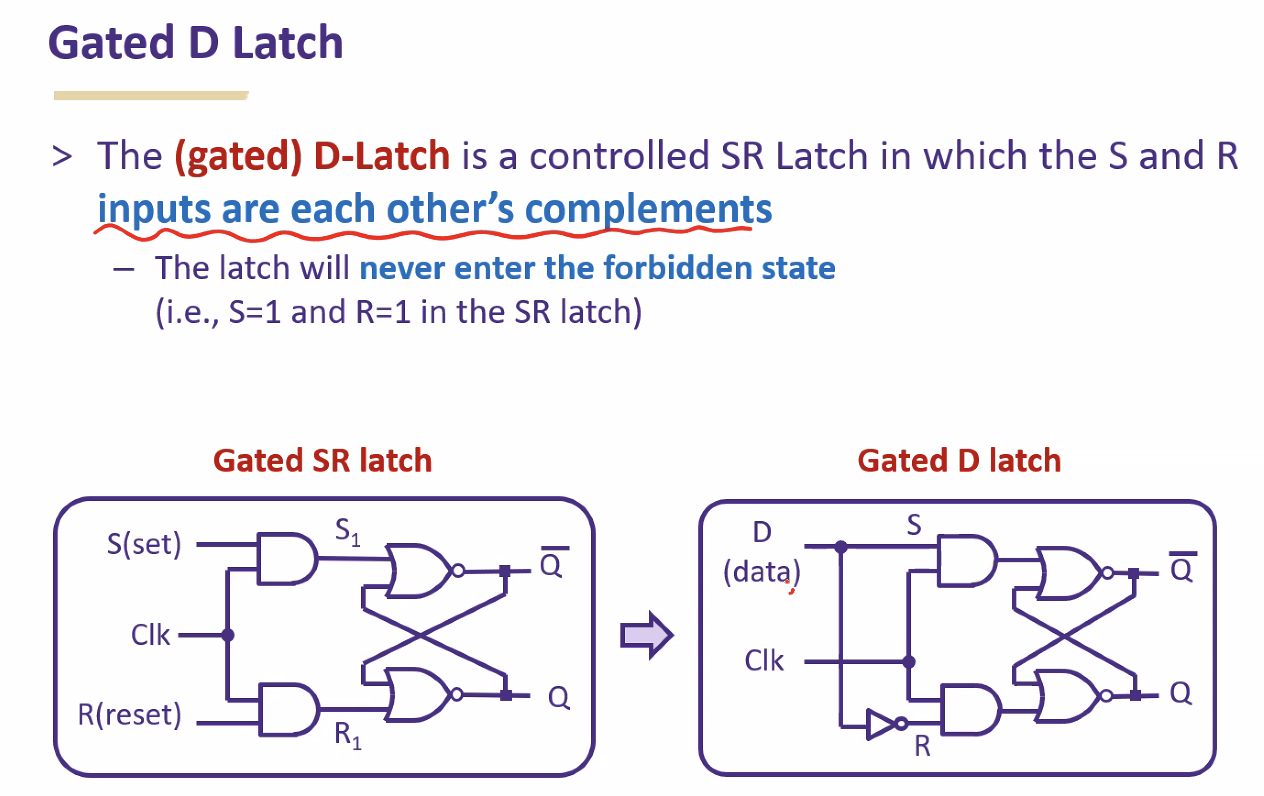

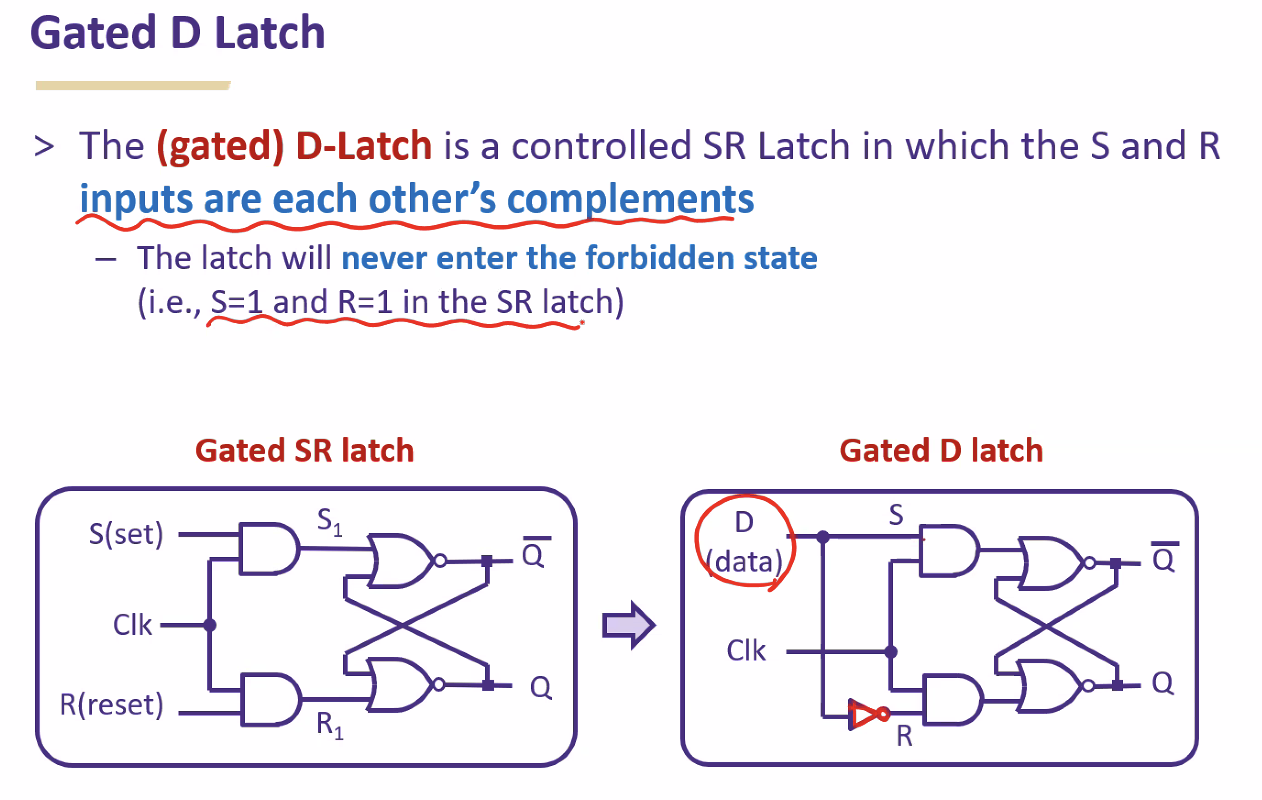

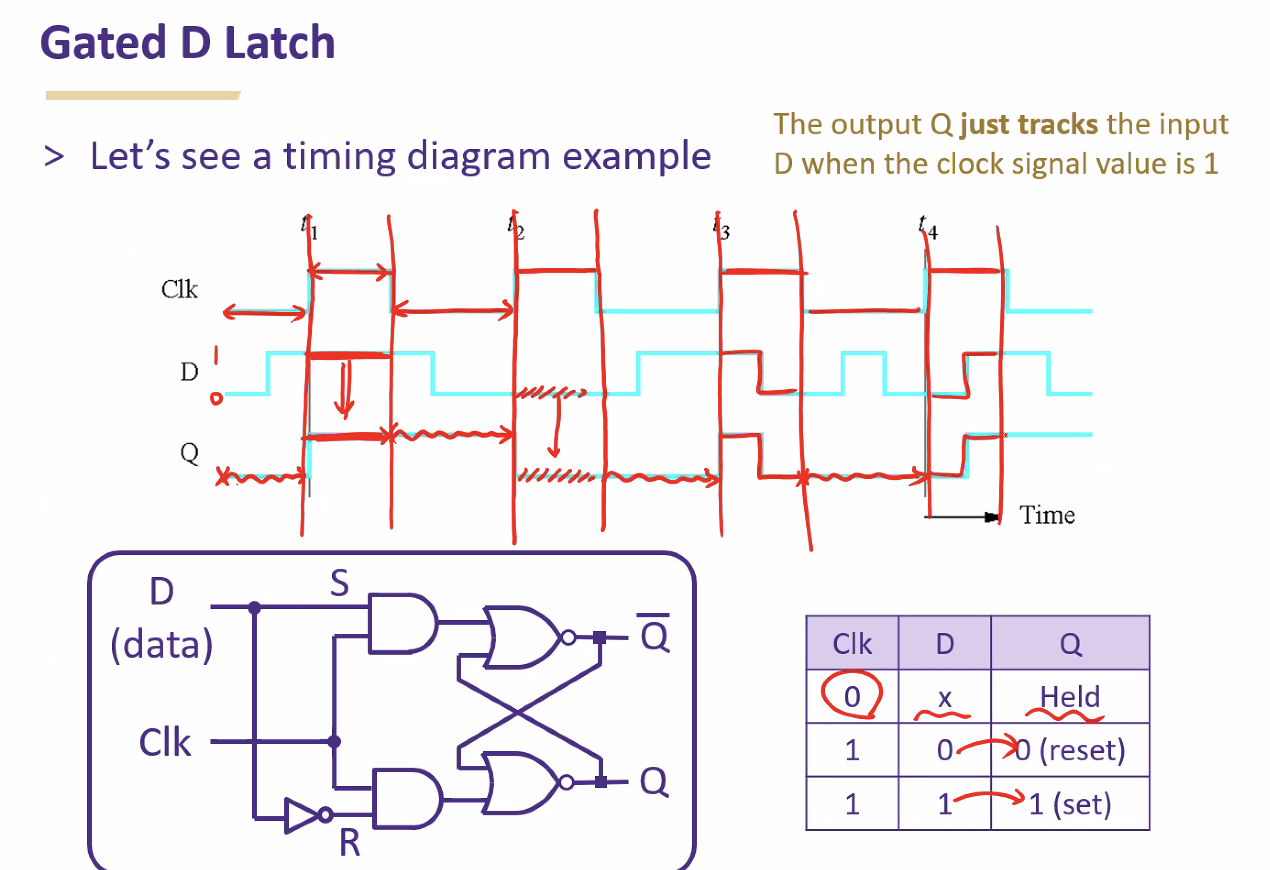

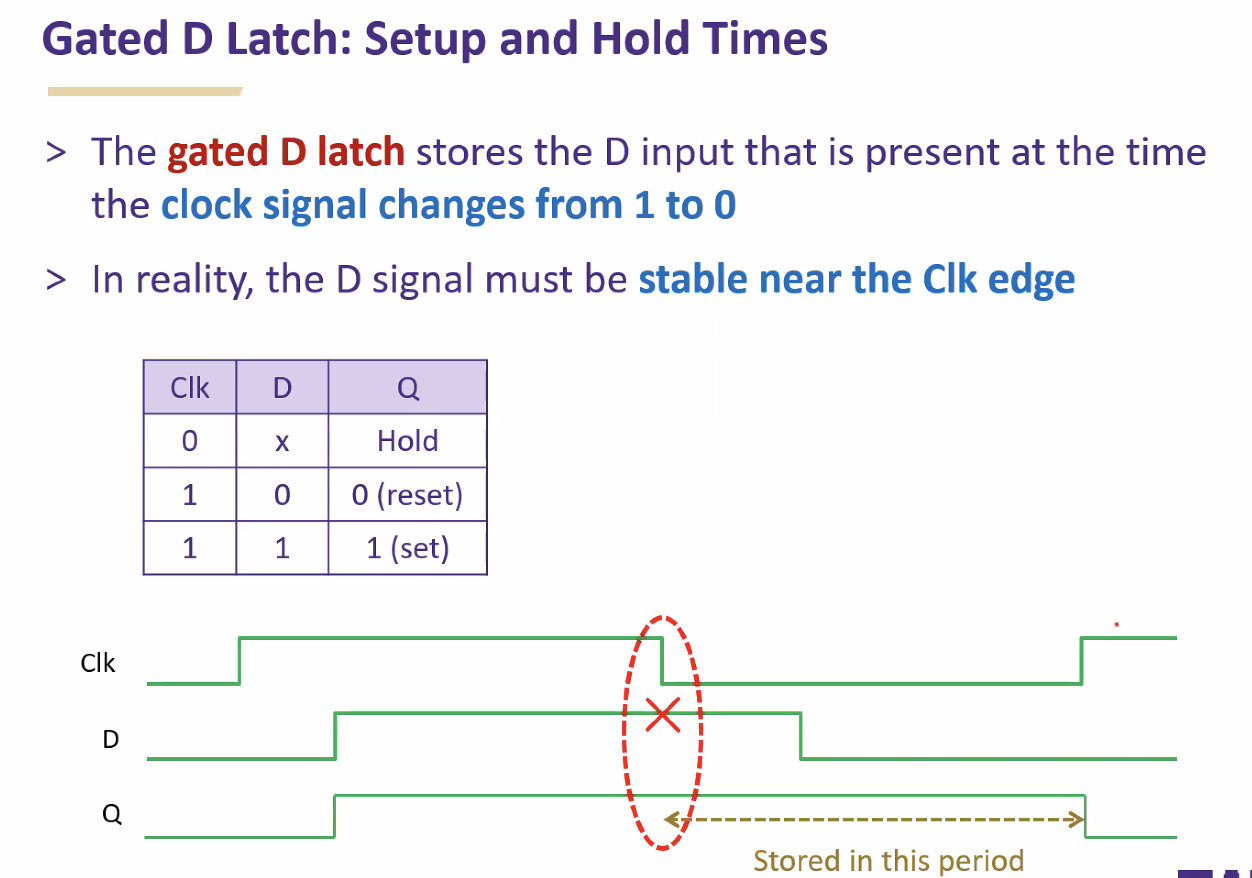

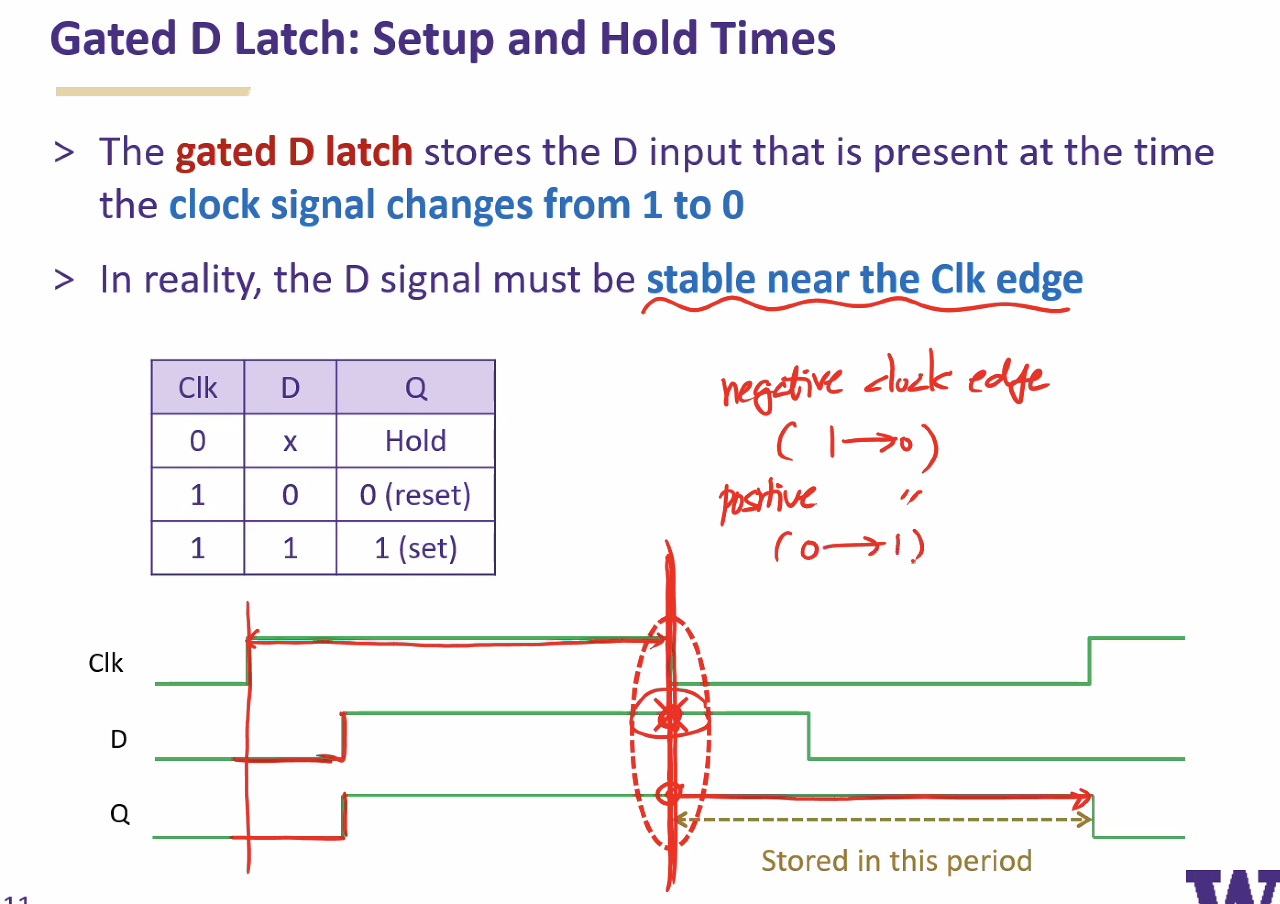

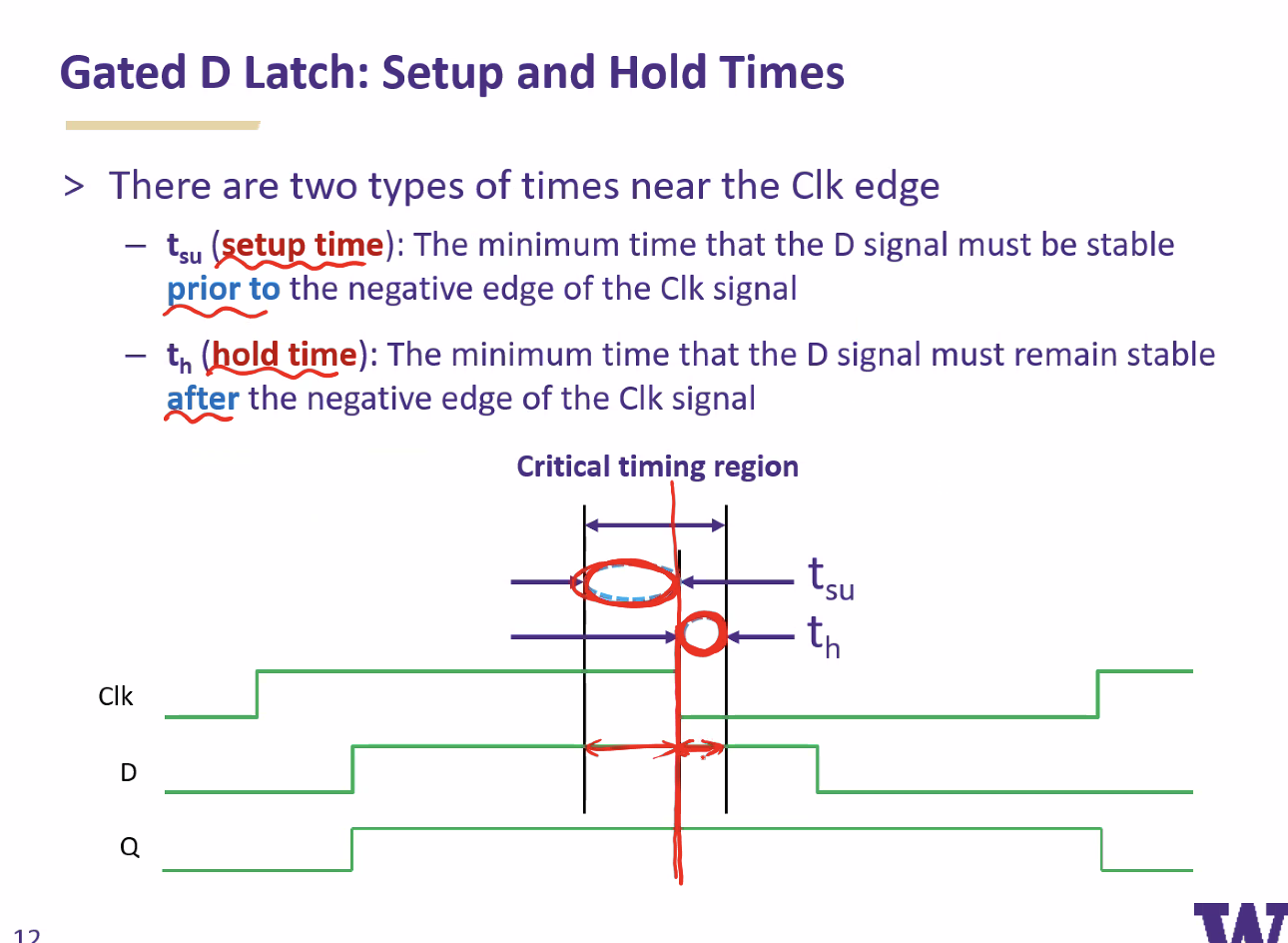

Gated d-latch. as long as clock is 1, the output tracks the input

with positive edge trigger flipflop, the output updates only when the clock signal goes positive

with negative edge trigger flipflop, the output only updates when the signal goes positive

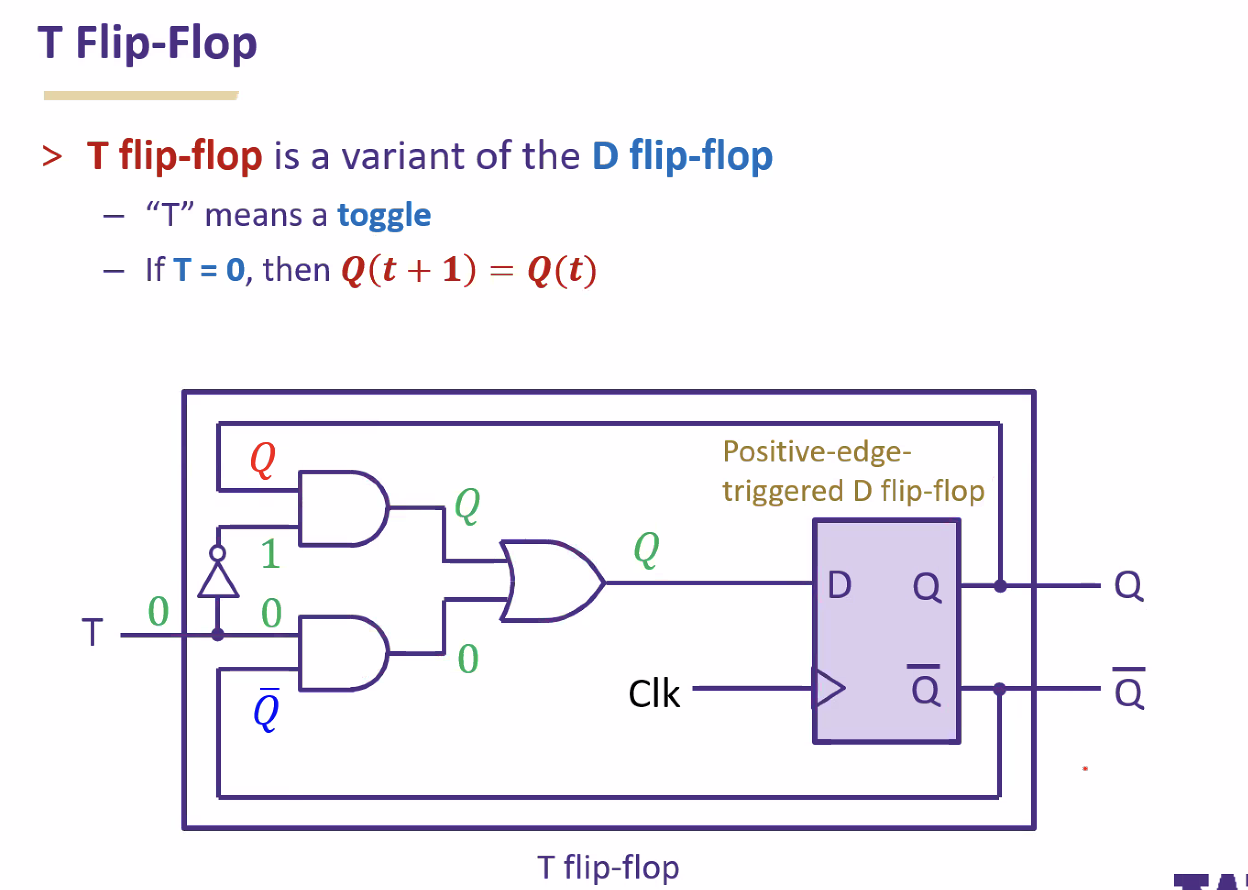

output value is flipped

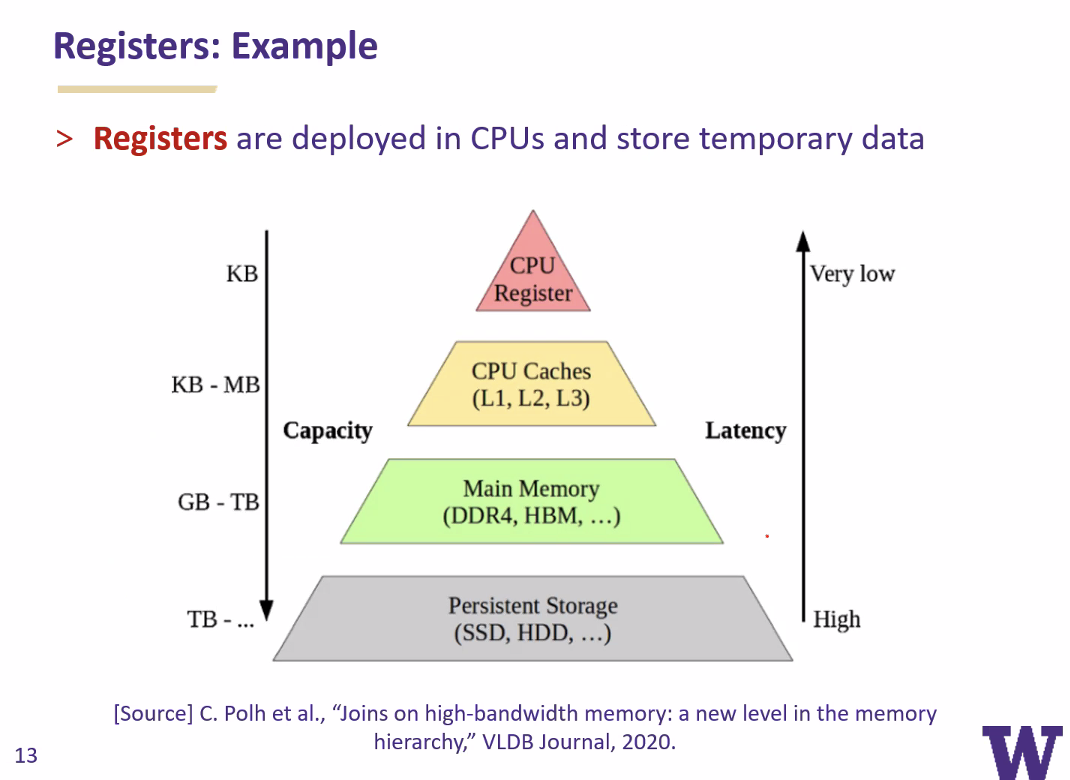

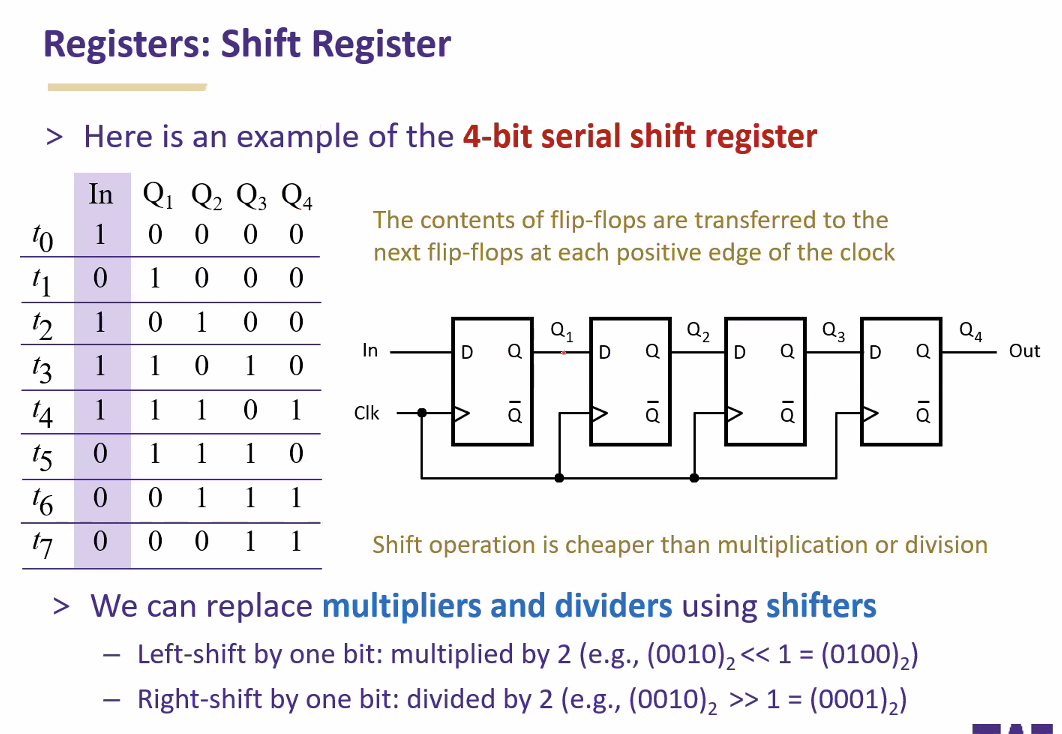

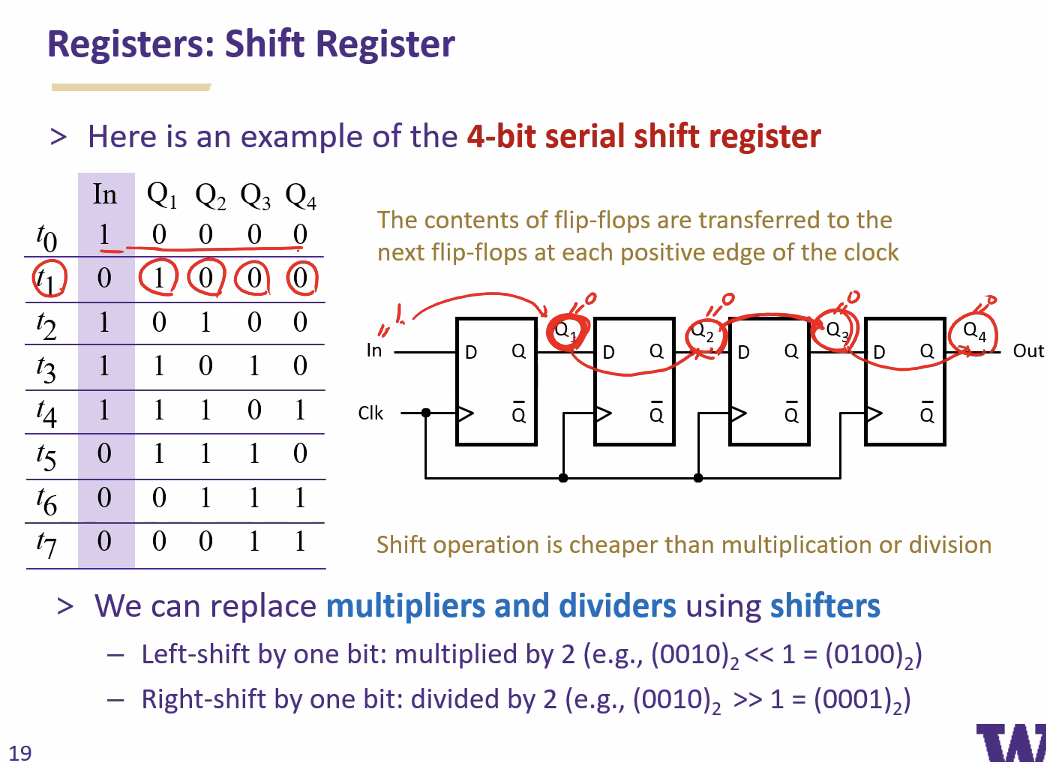

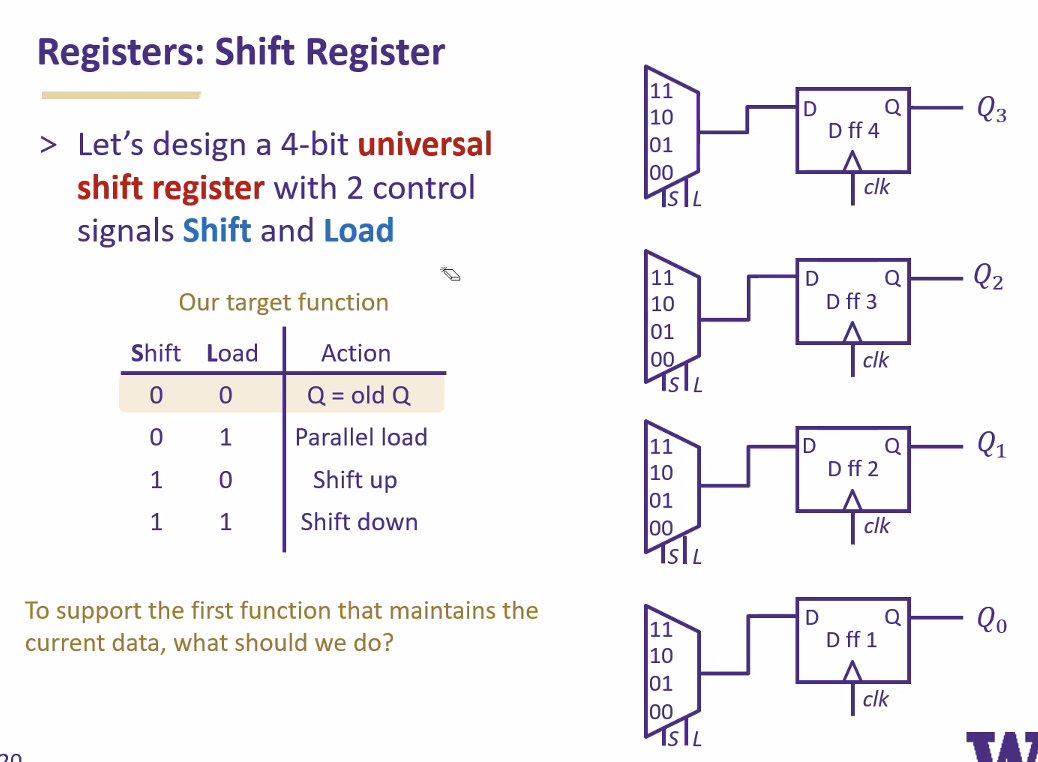

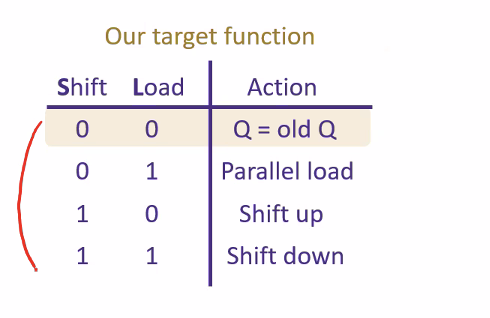

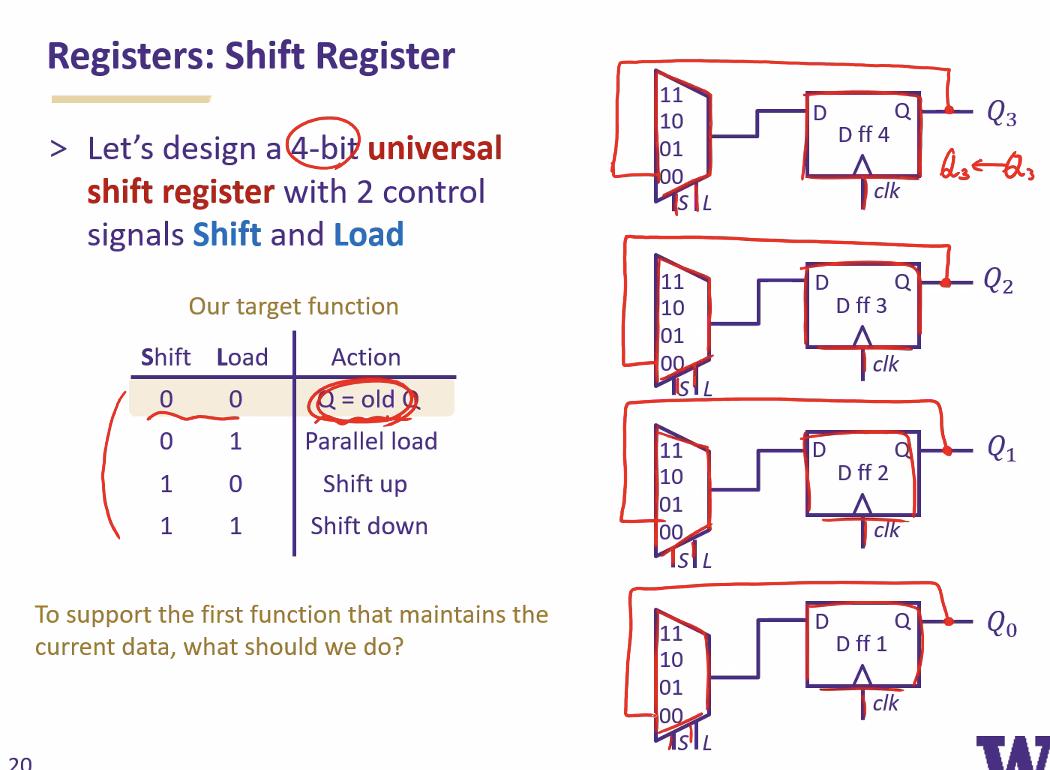

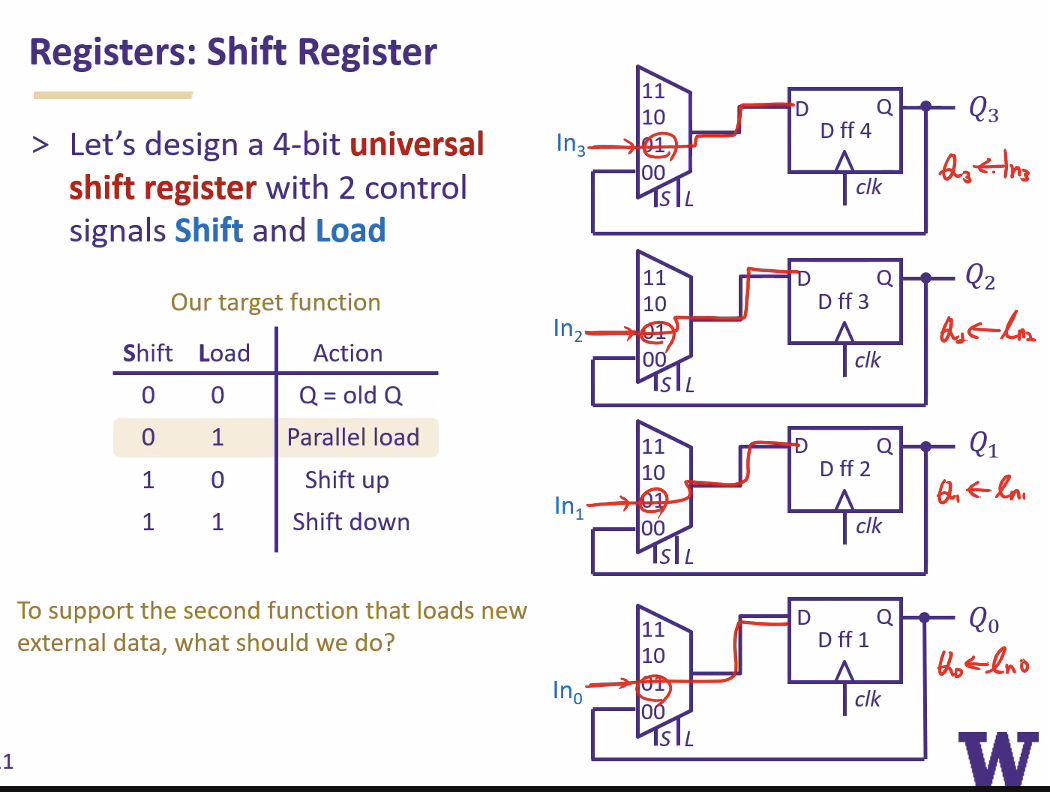

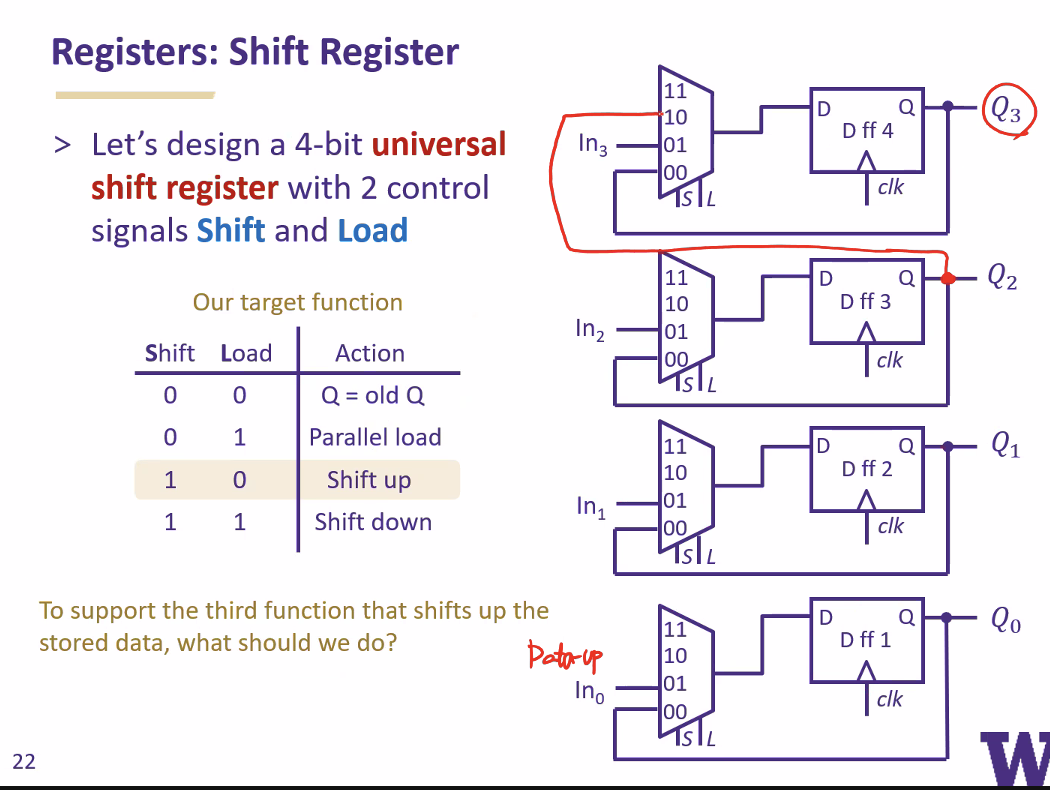

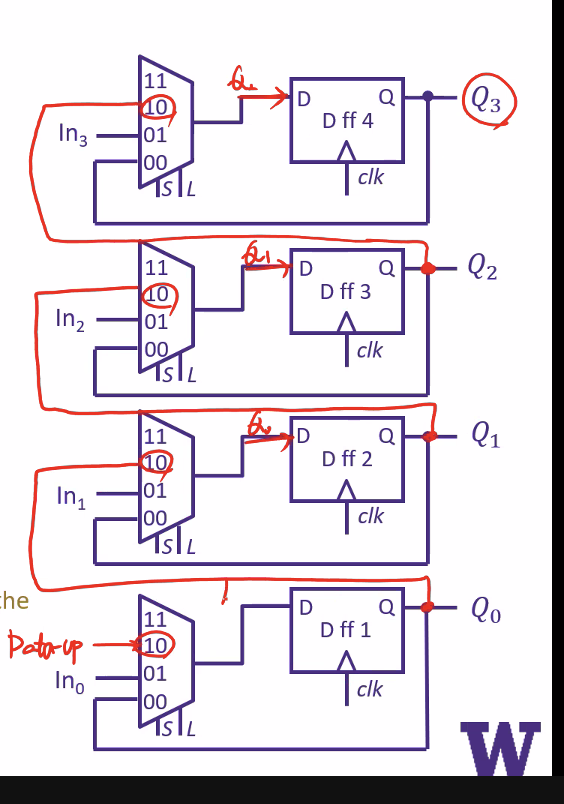

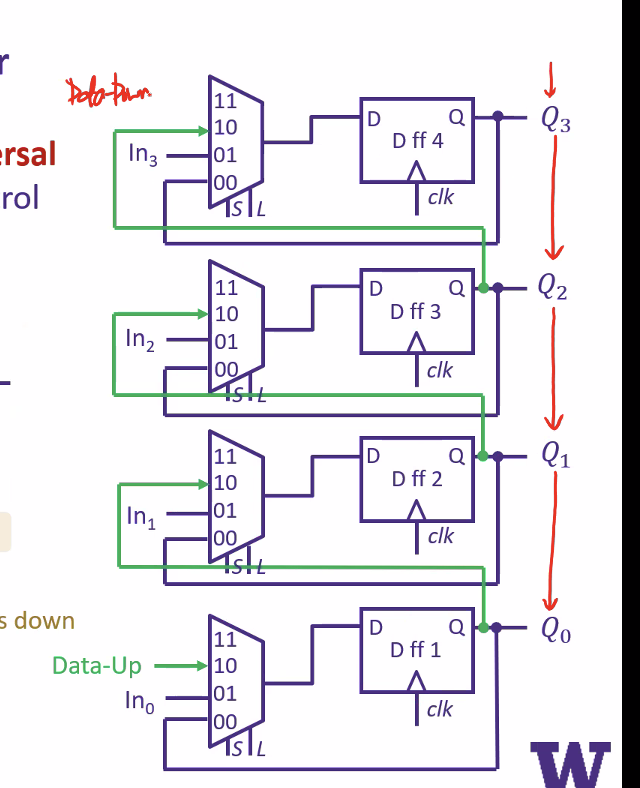

Registers

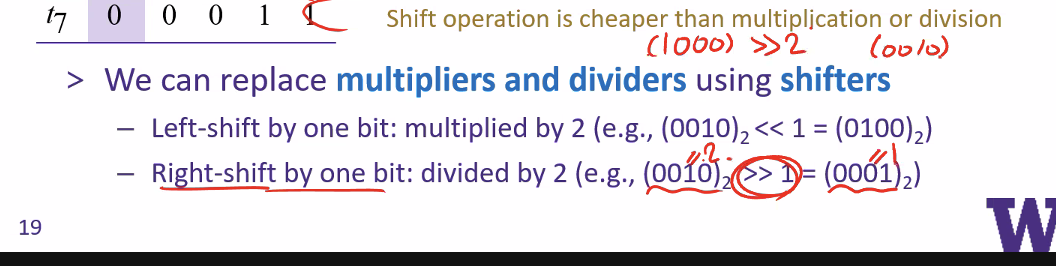

Right shifted by 2 is dividing by 2 twice.

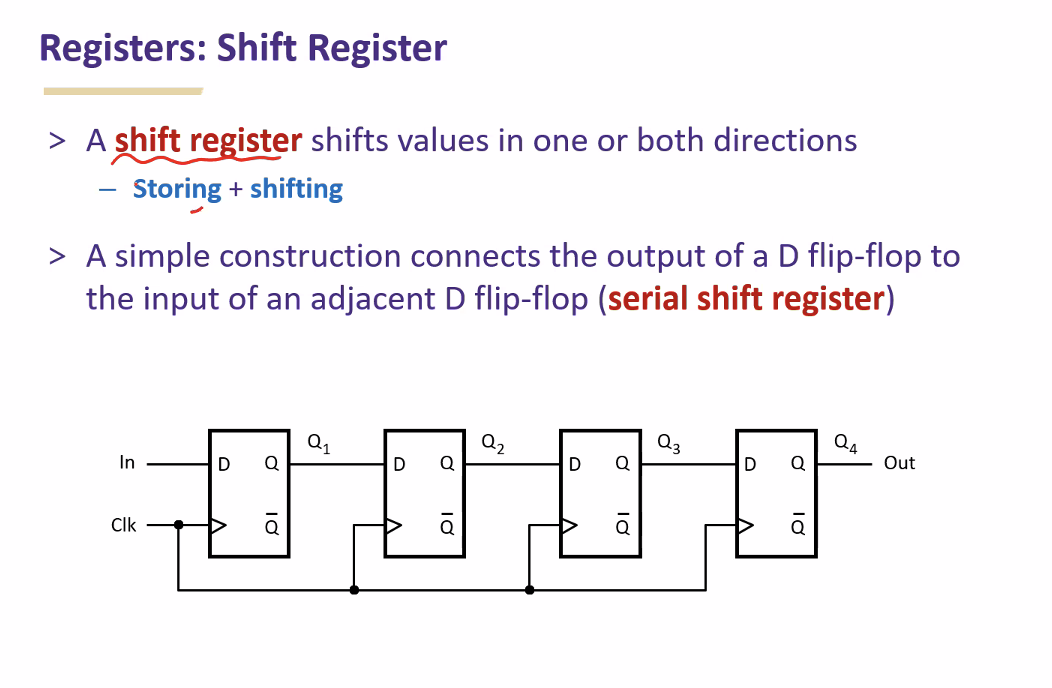

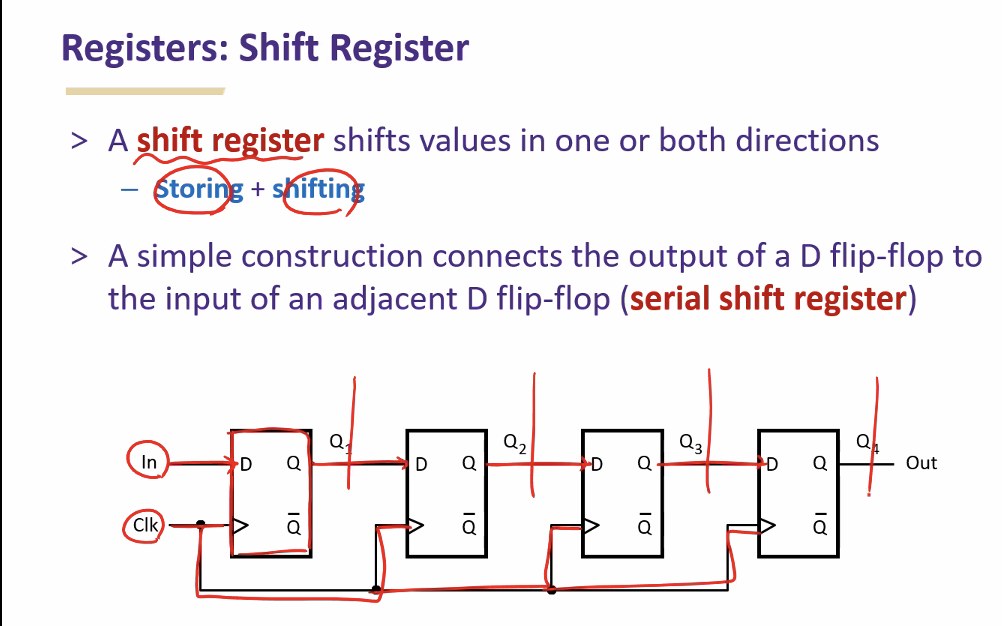

Shift Register

Updated at next positive clock edge

Shift up, q3 is updated using q2, q2 with q1 etc

Data Up

is just a data input for the shift up

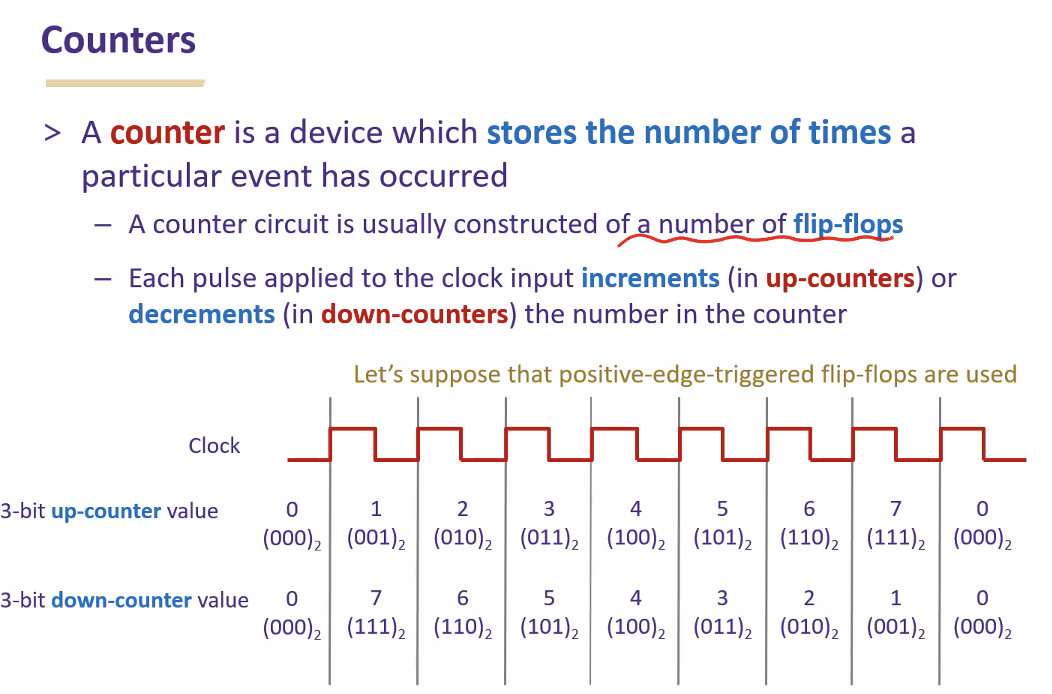

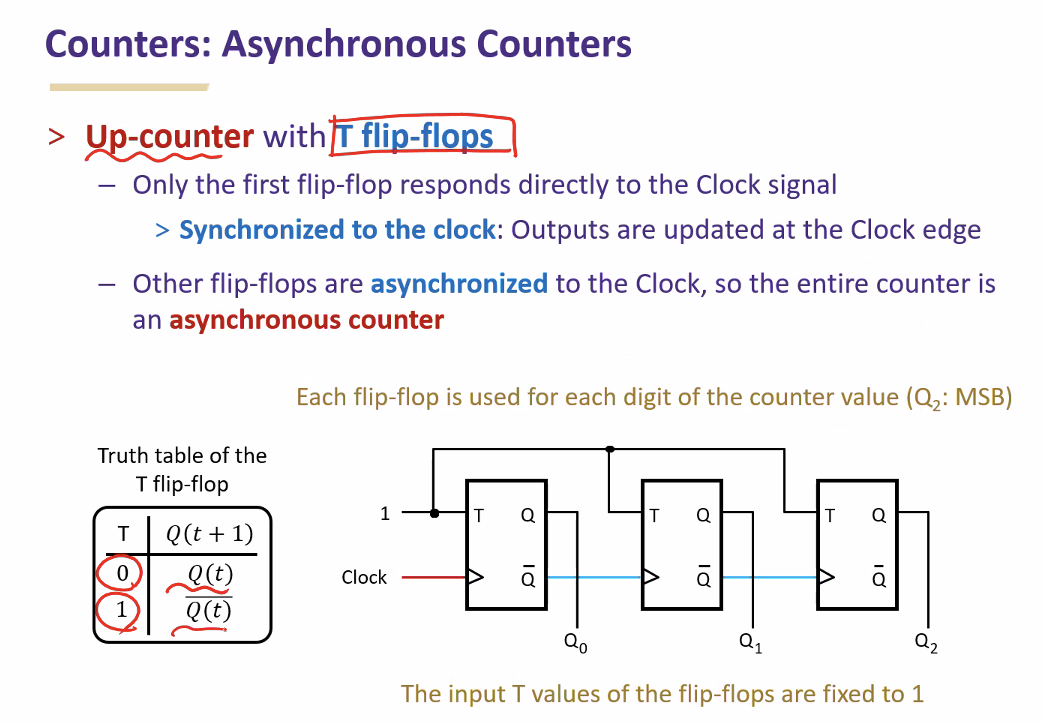

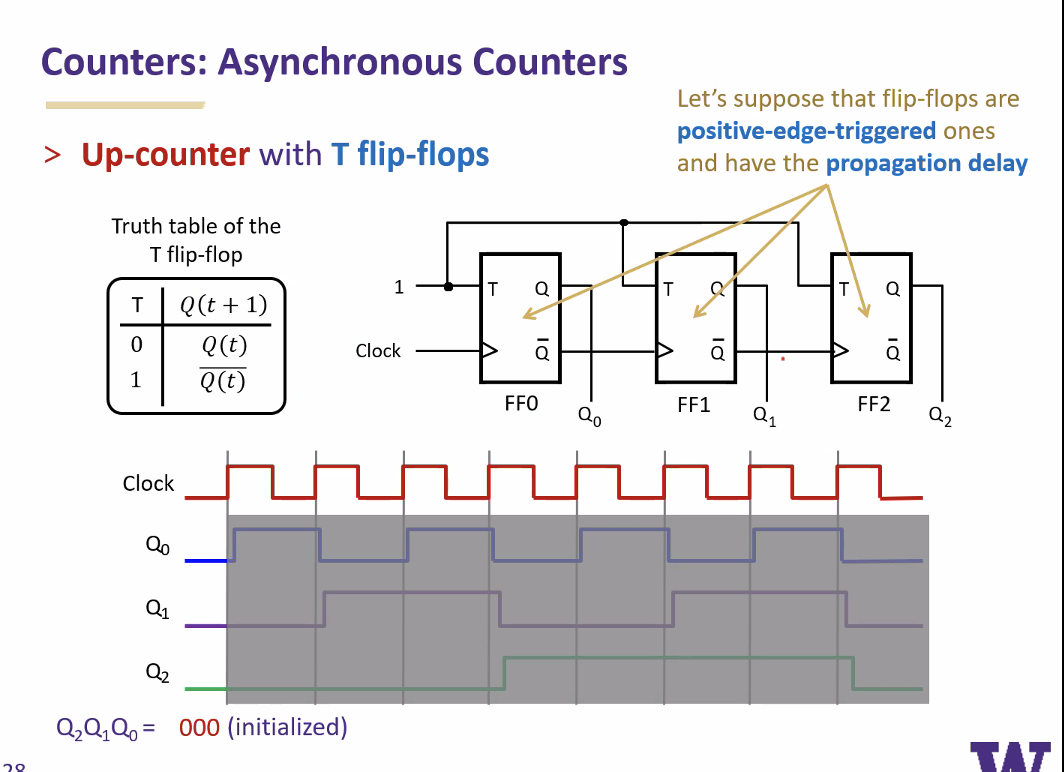

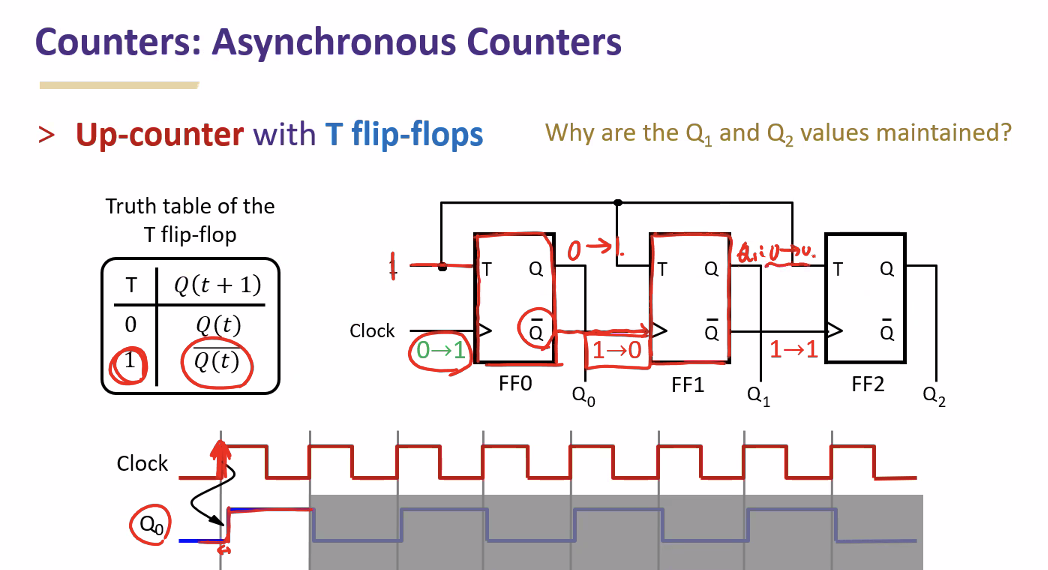

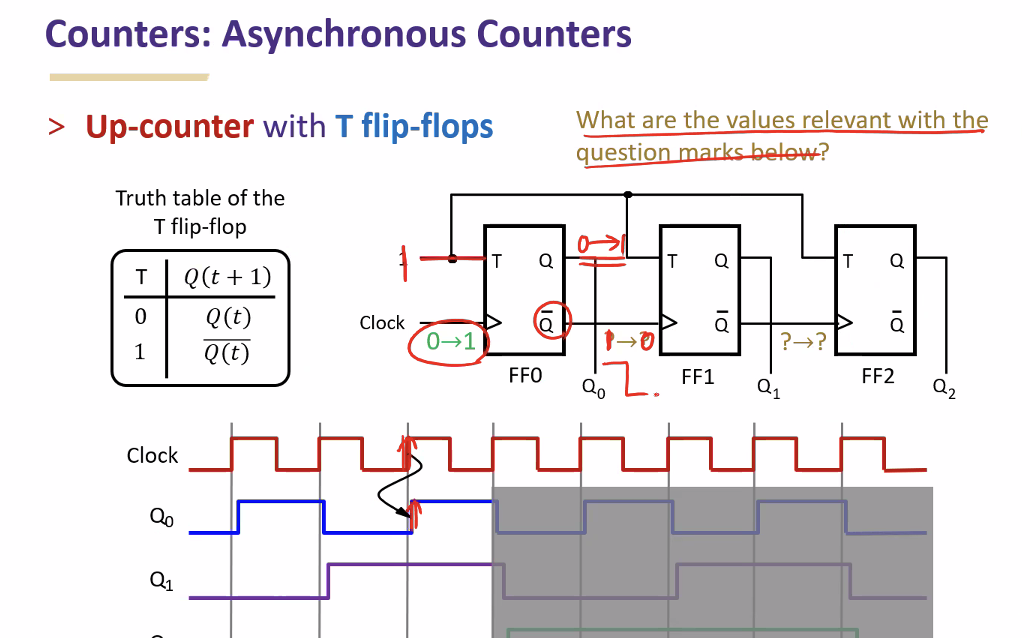

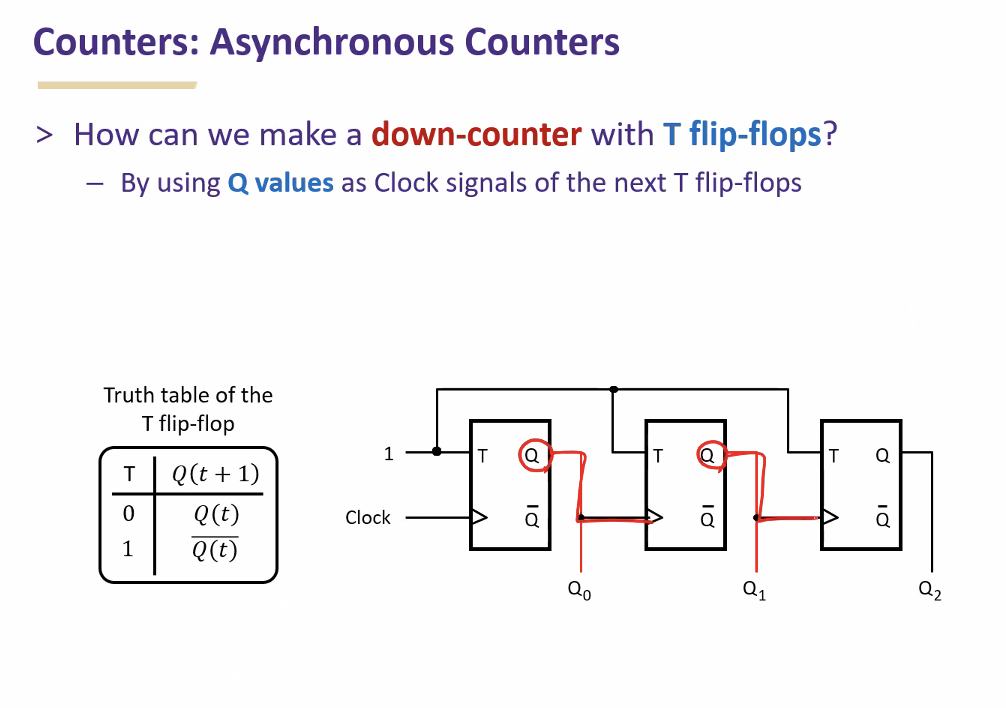

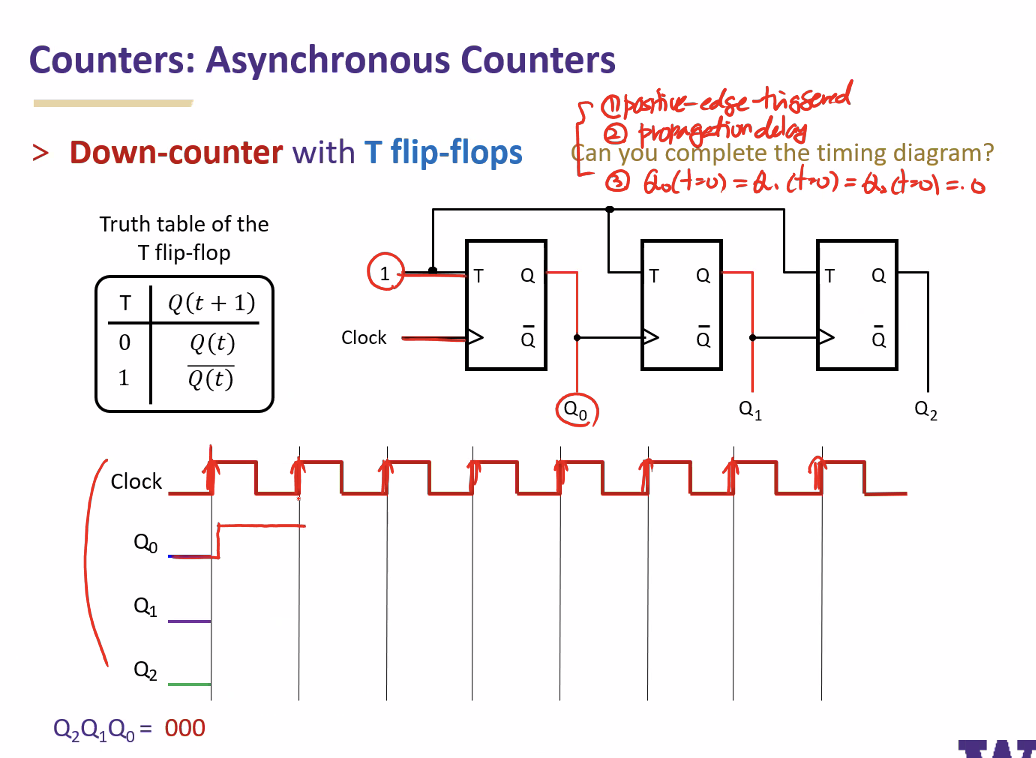

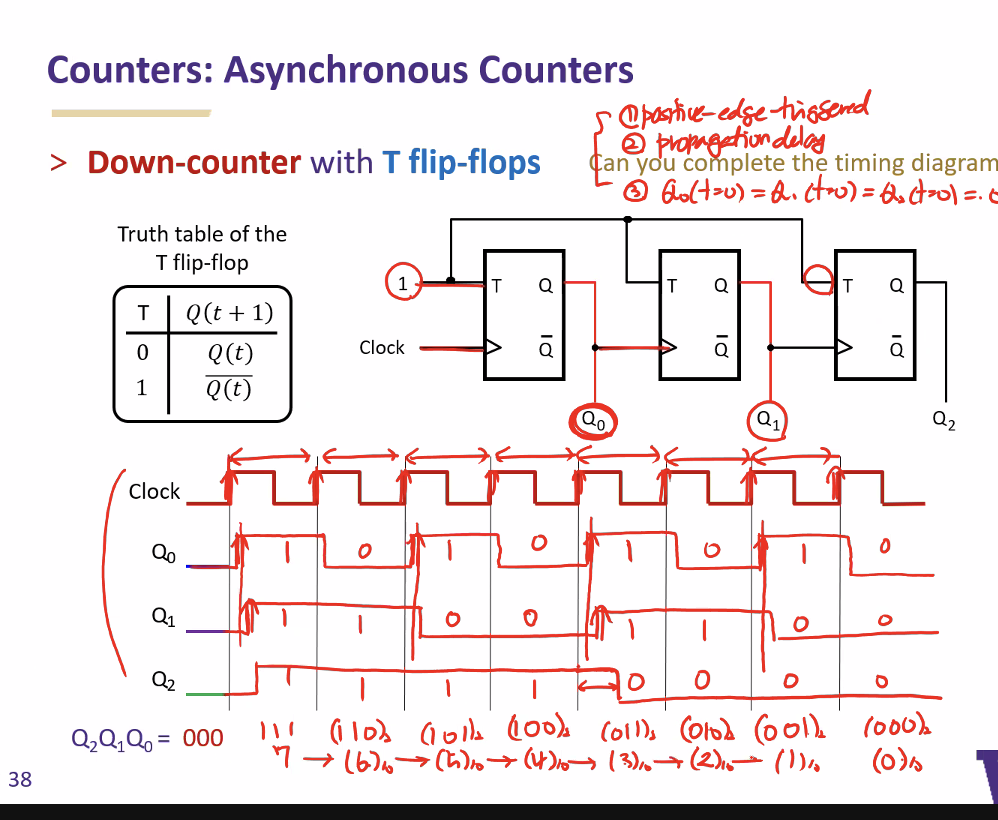

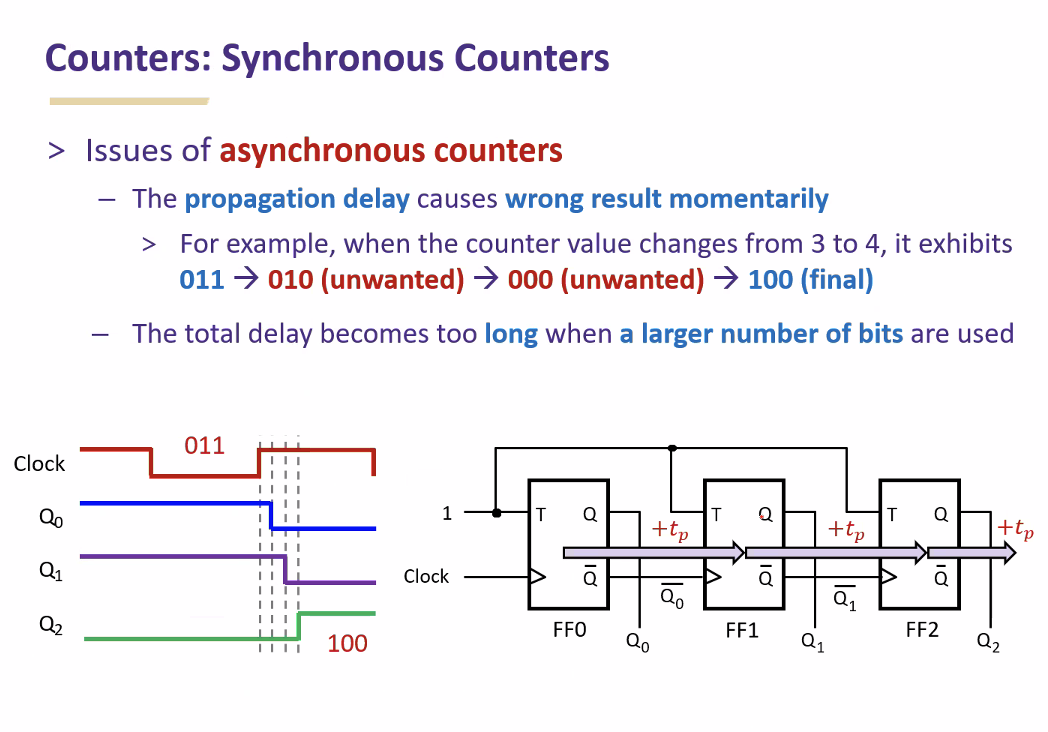

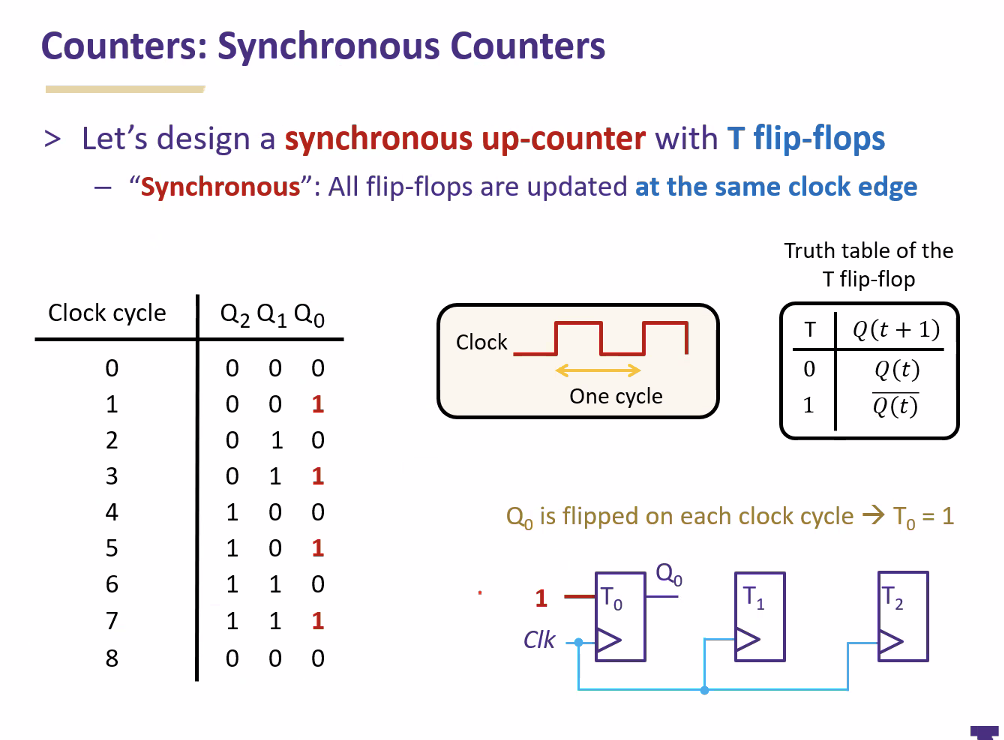

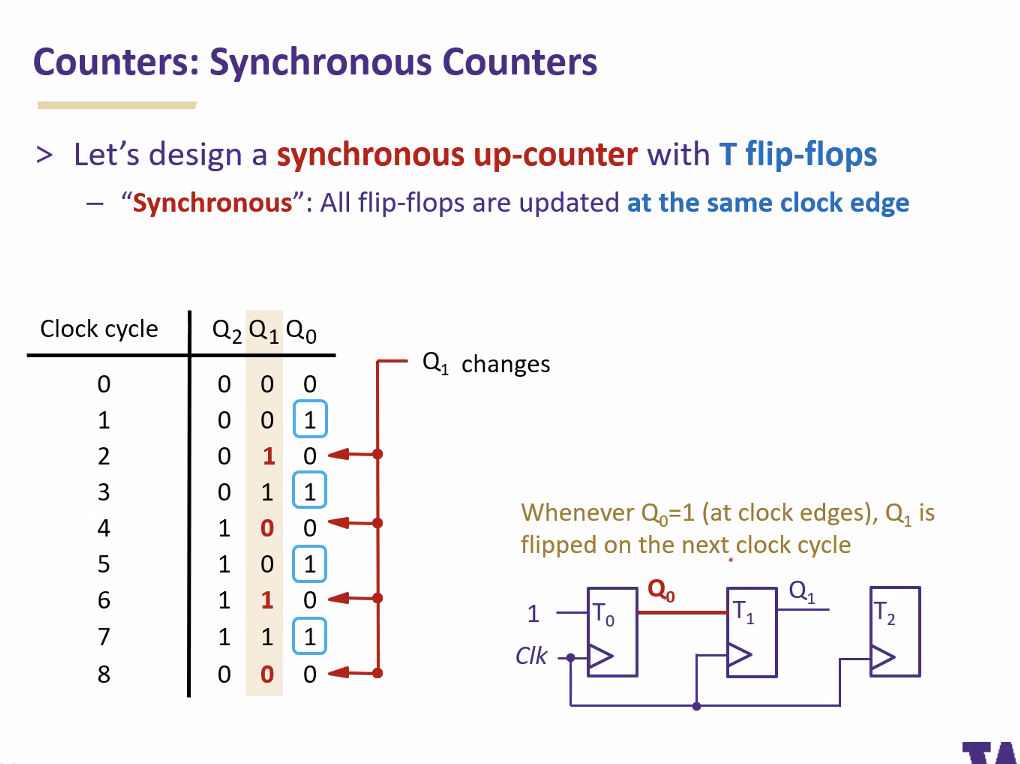

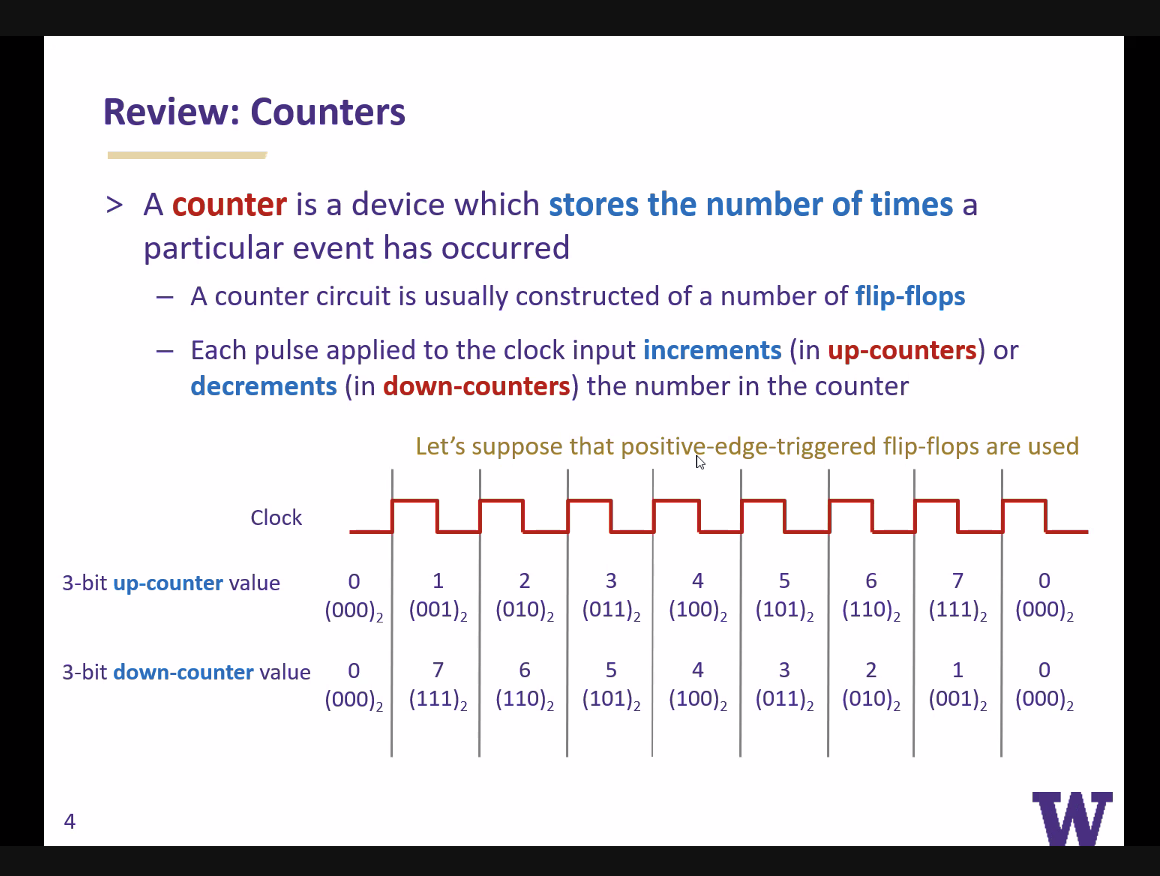

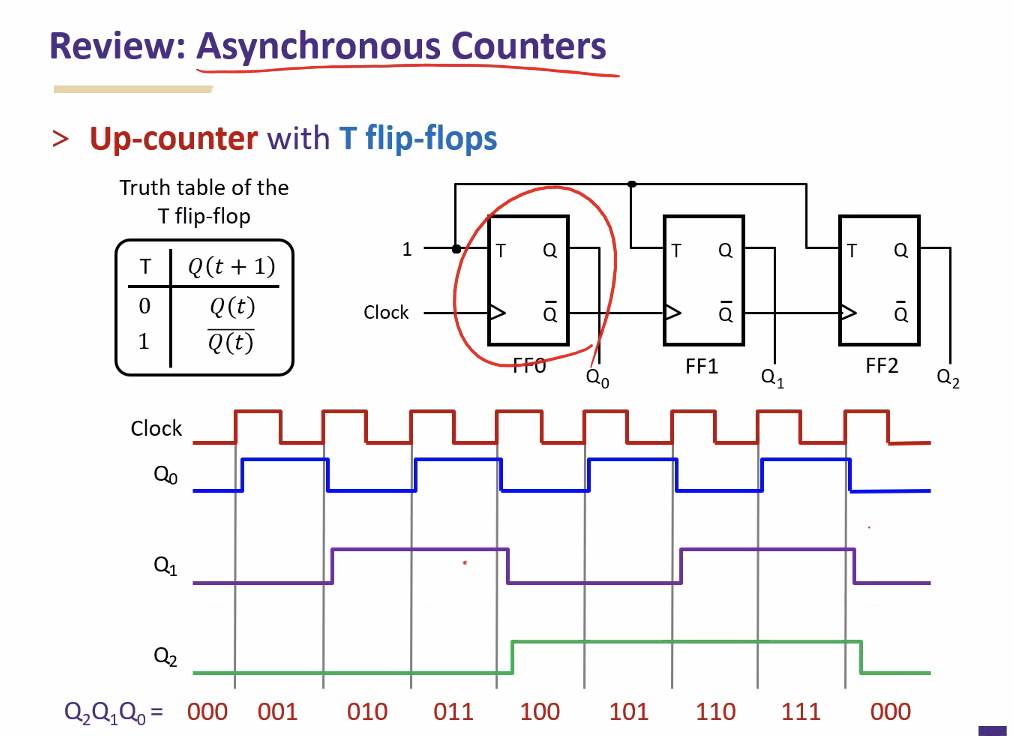

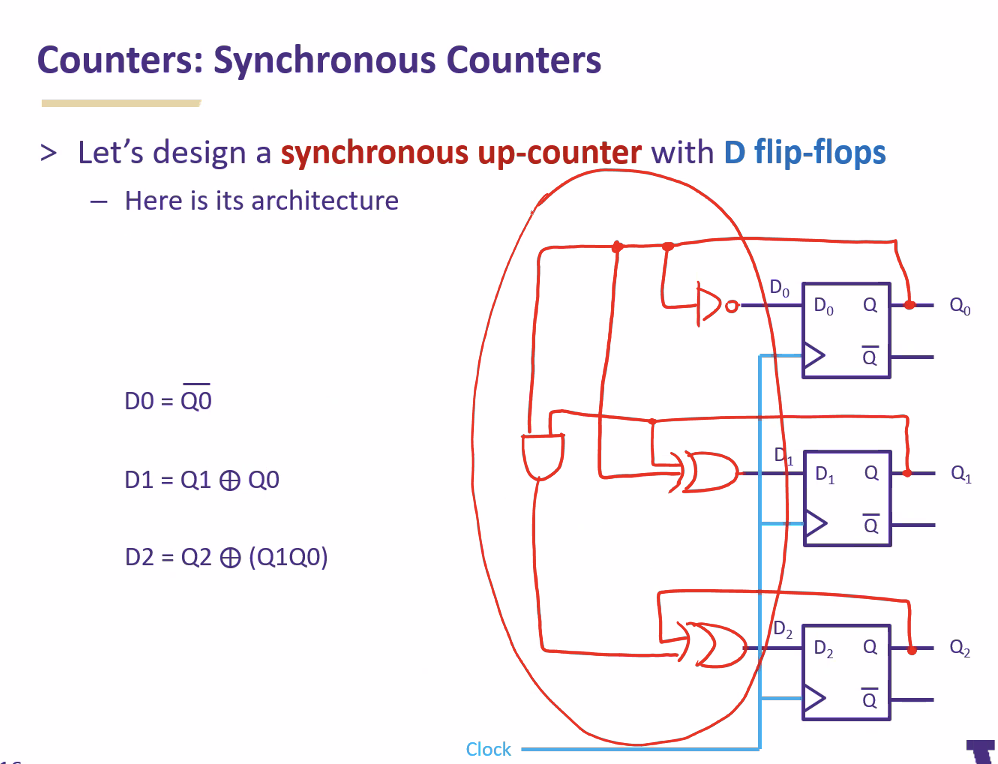

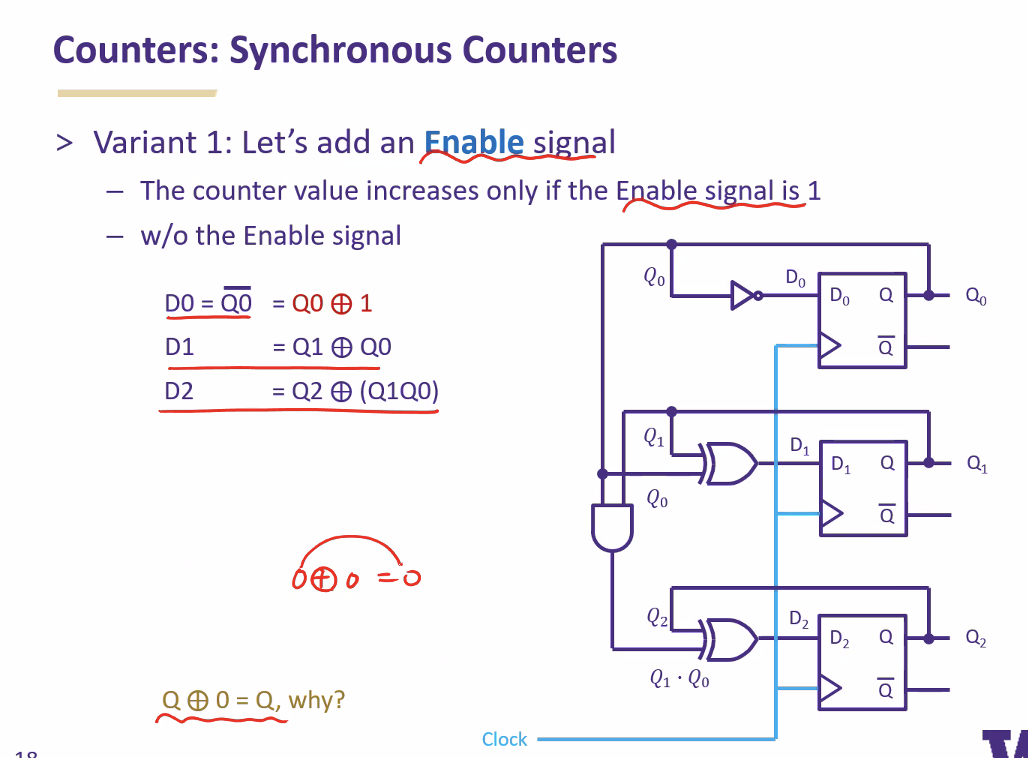

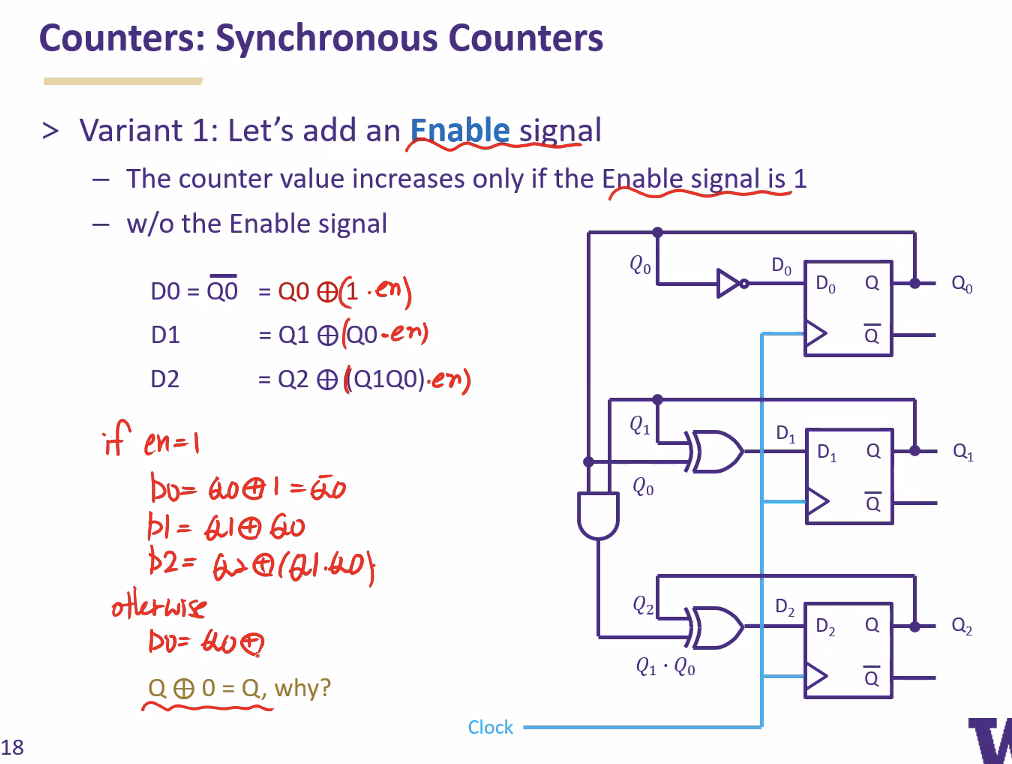

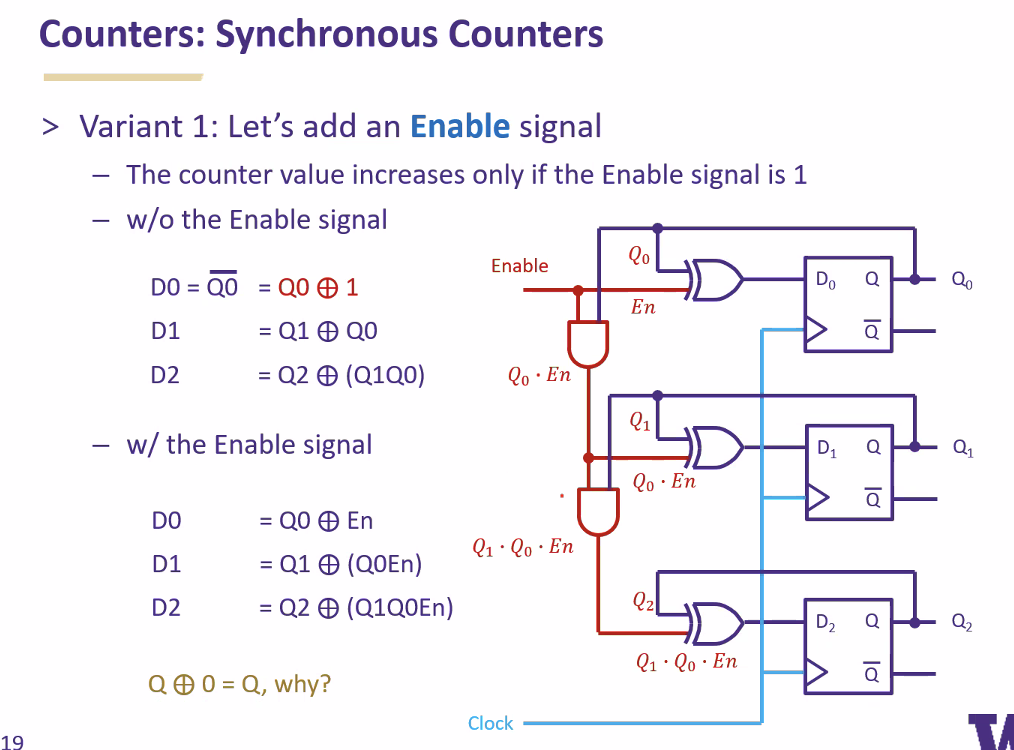

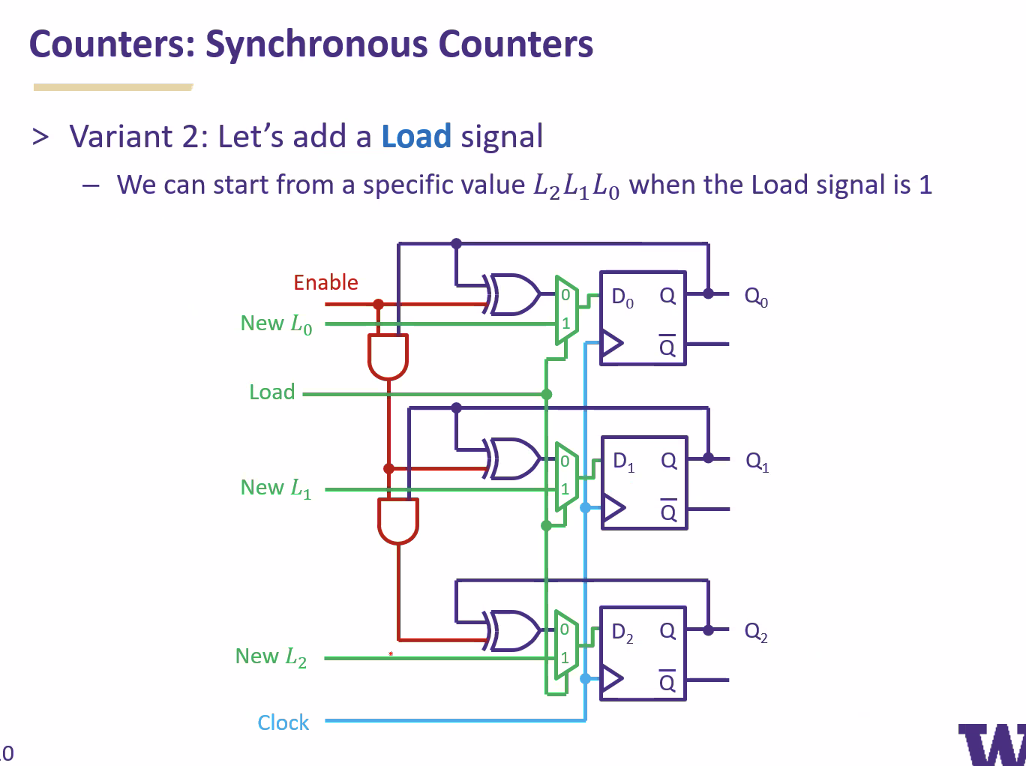

Counters

A counter is a device that stores times an event has occured

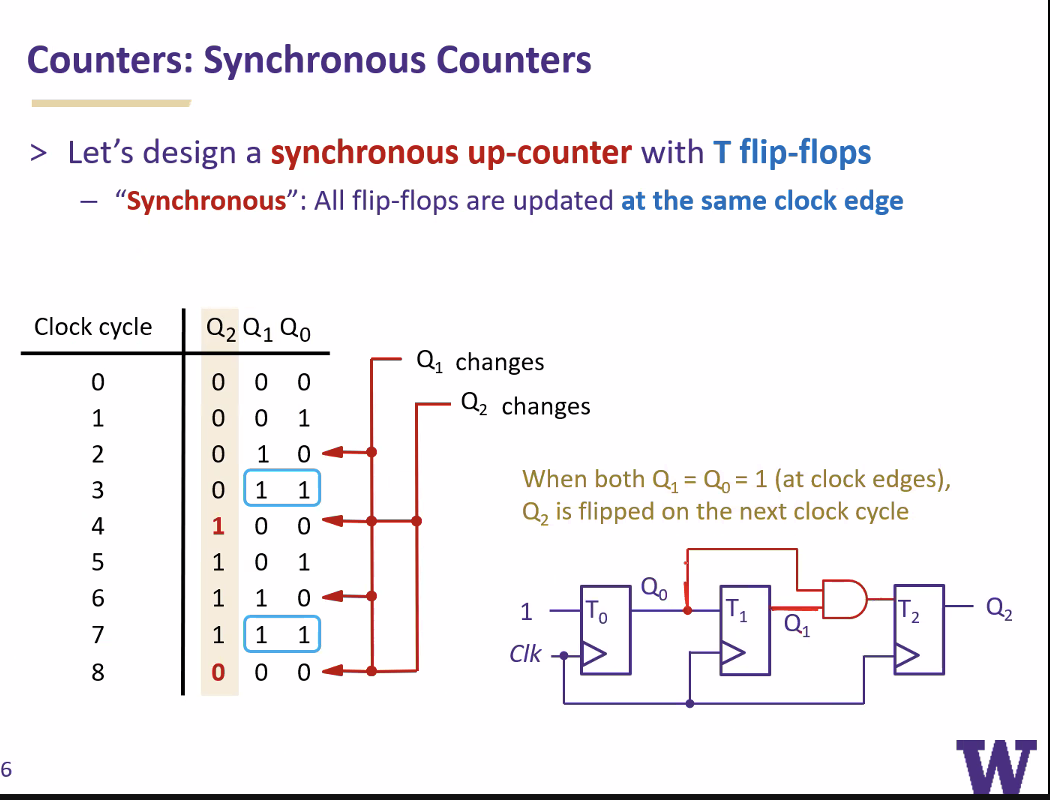

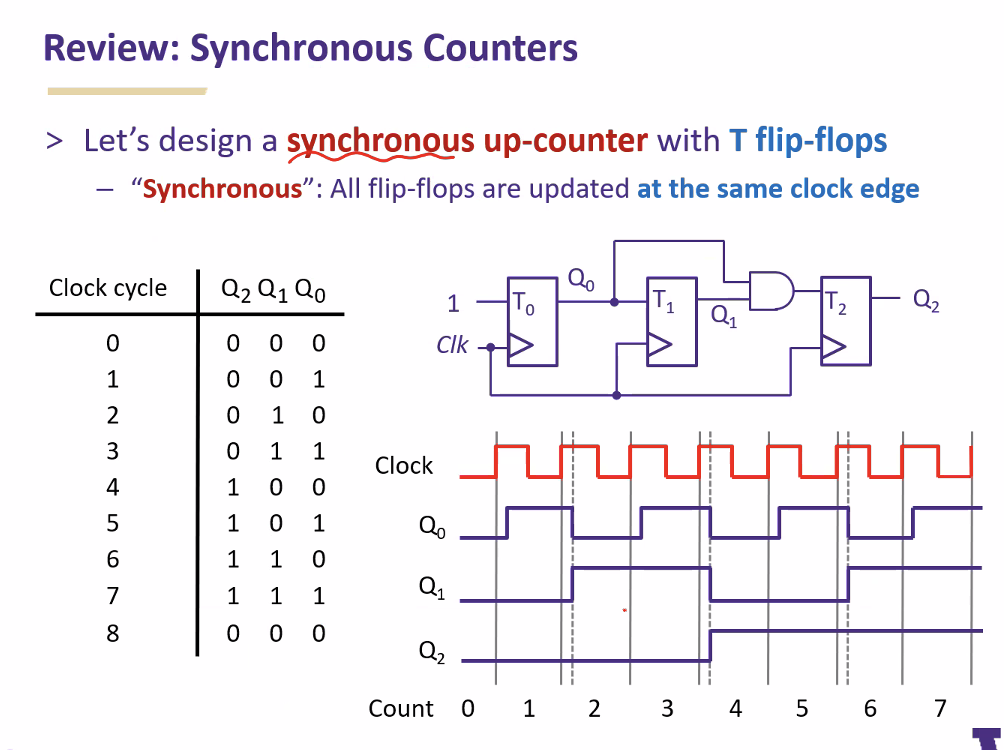

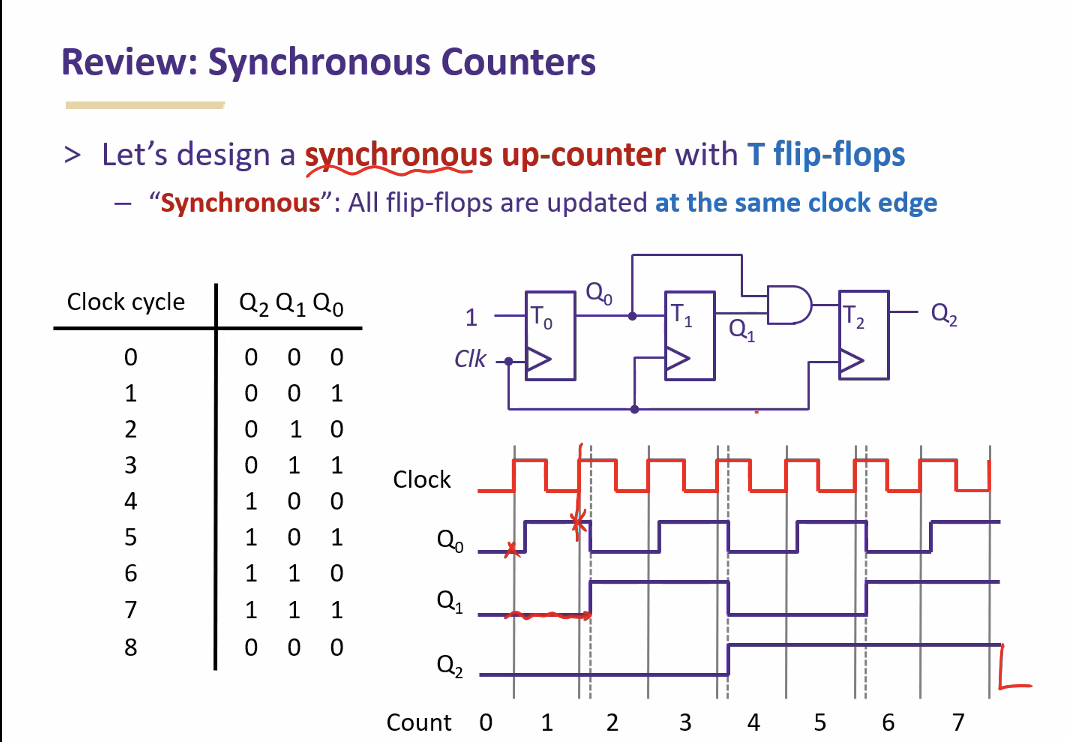

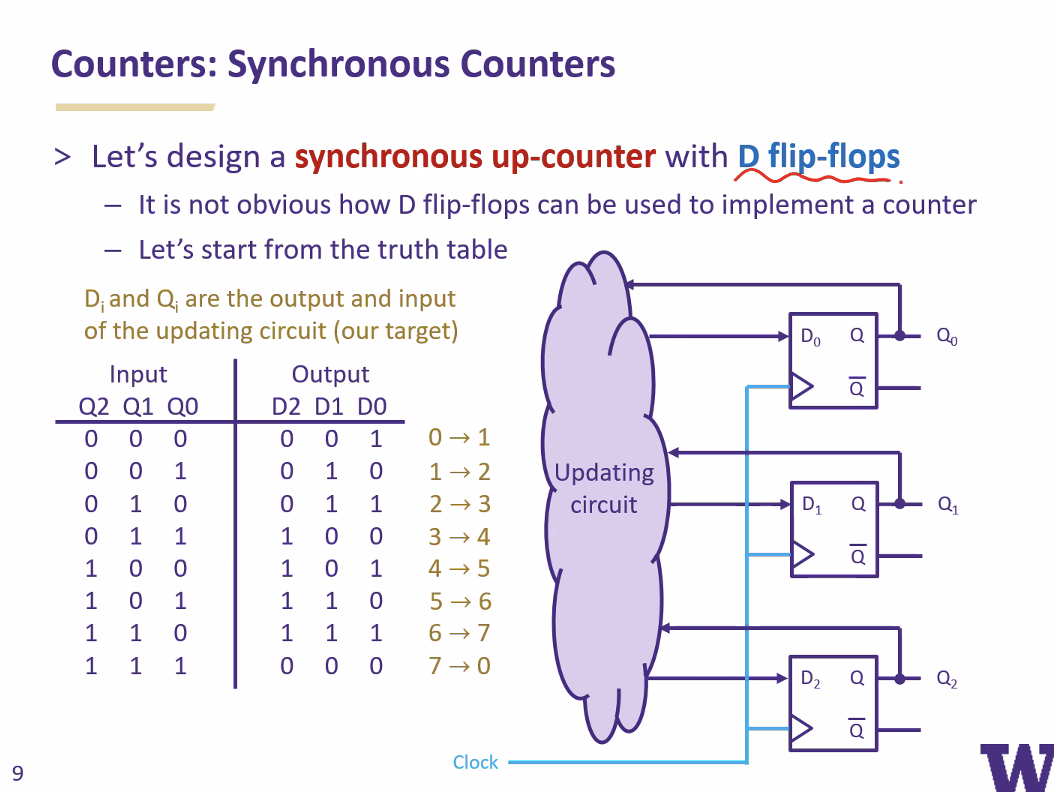

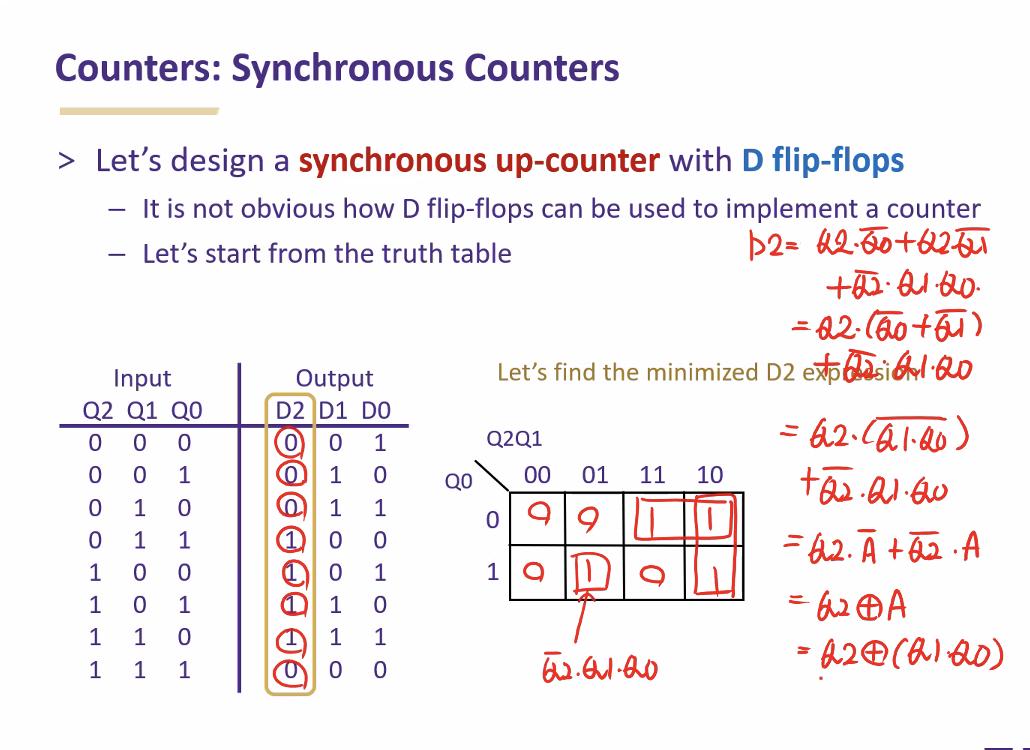

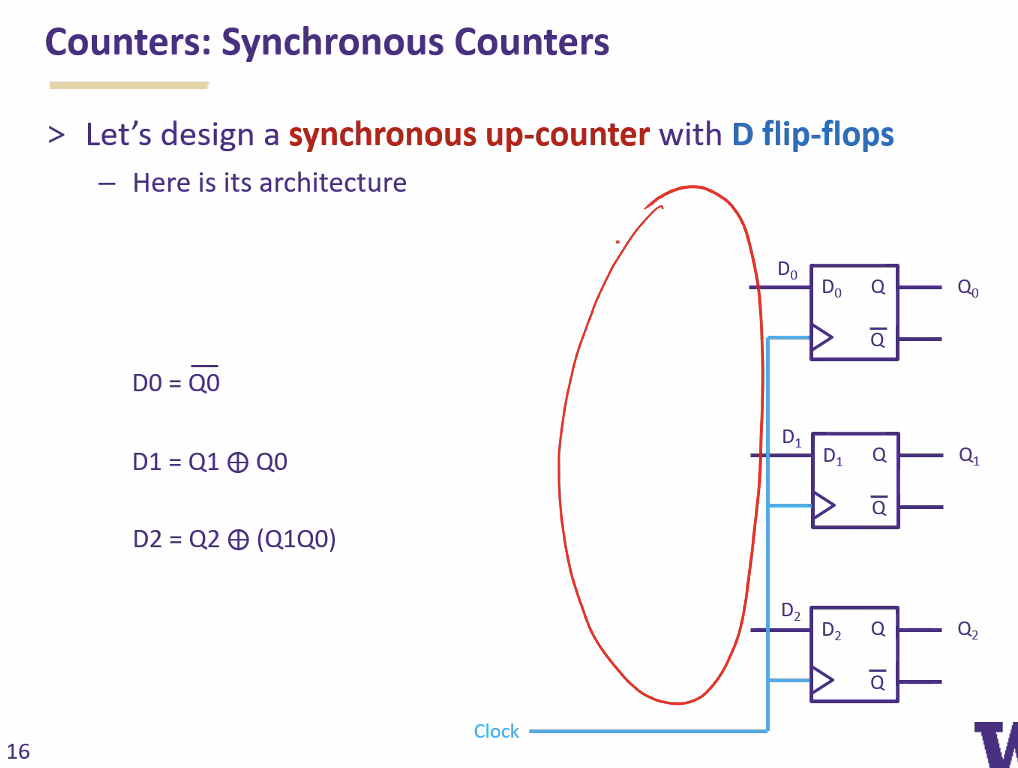

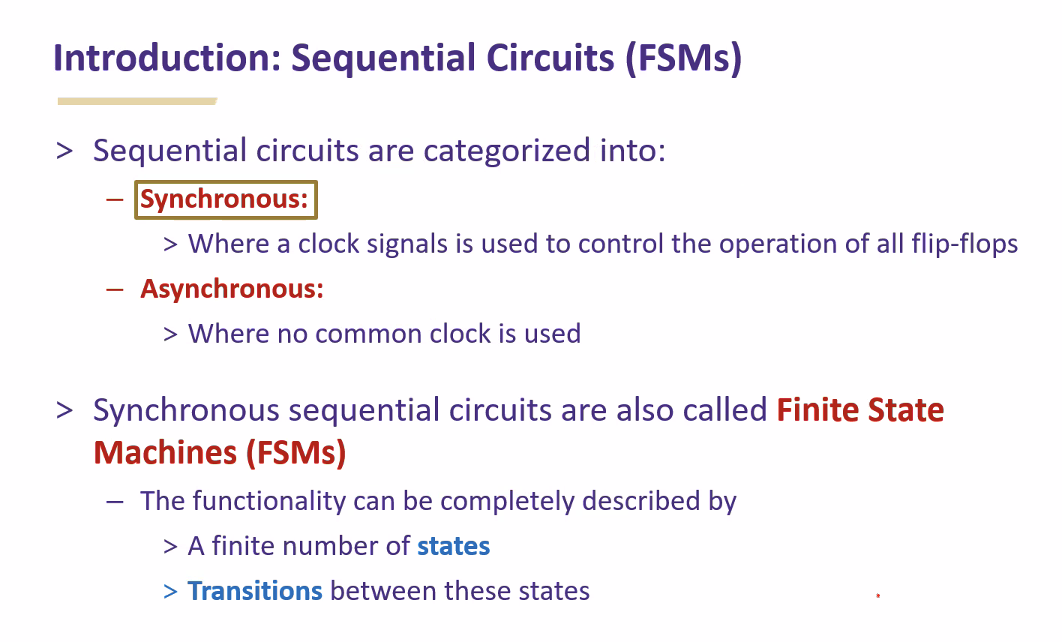

Syncronous counters

Lecture 13

Lecture 14

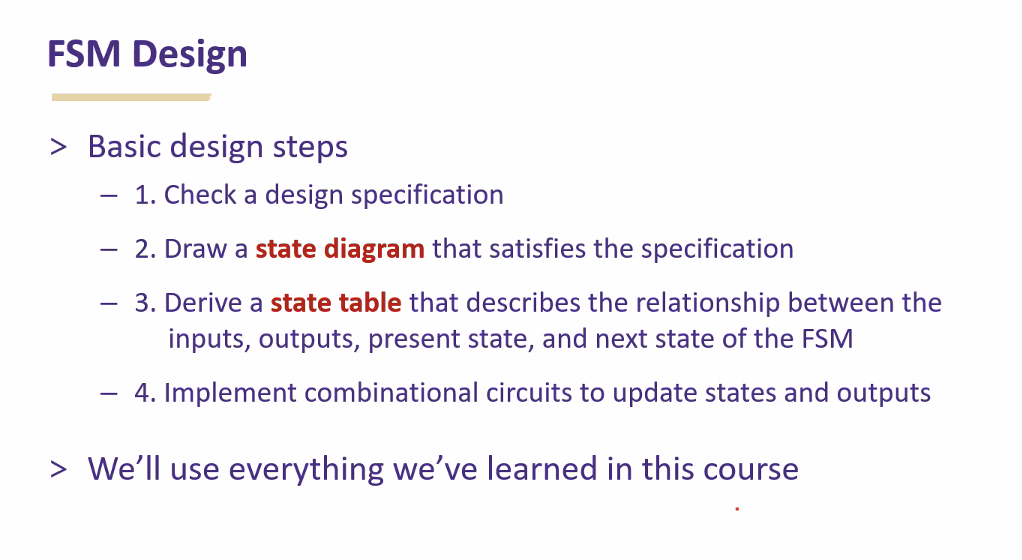

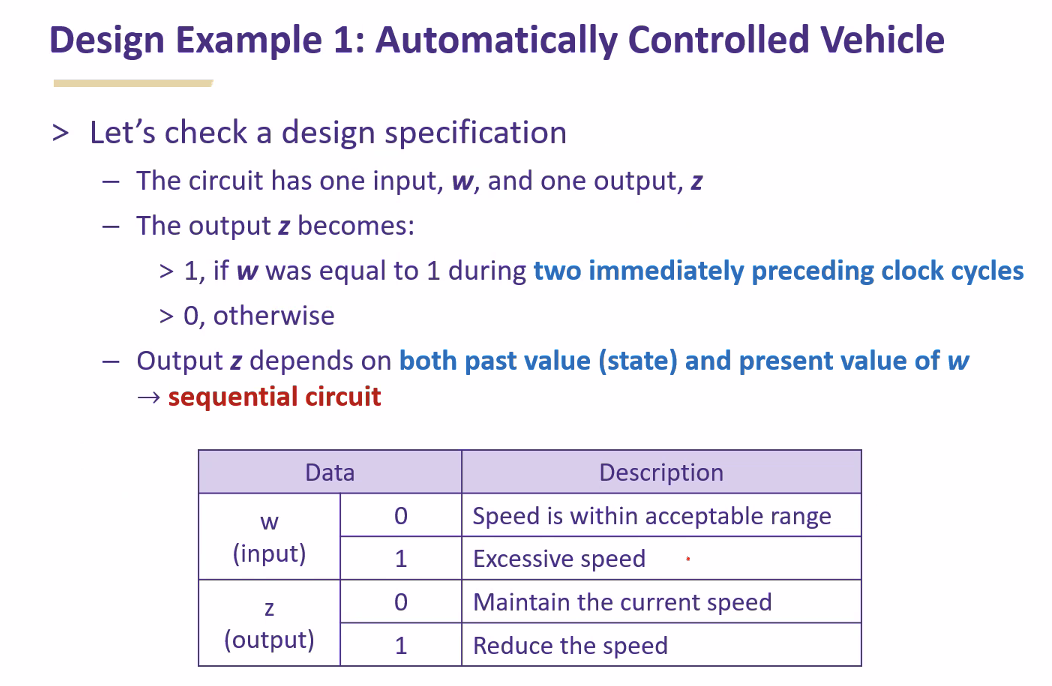

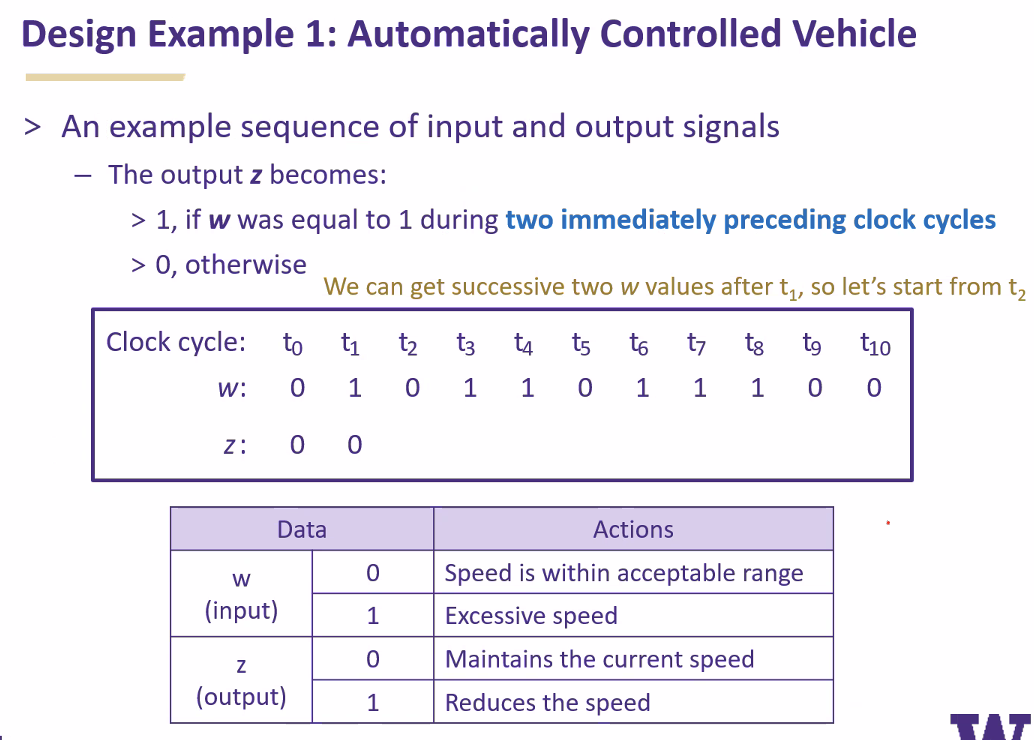

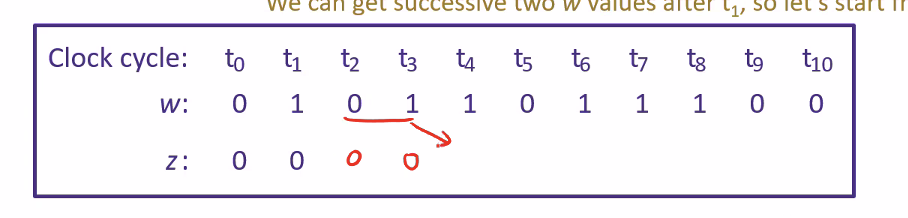

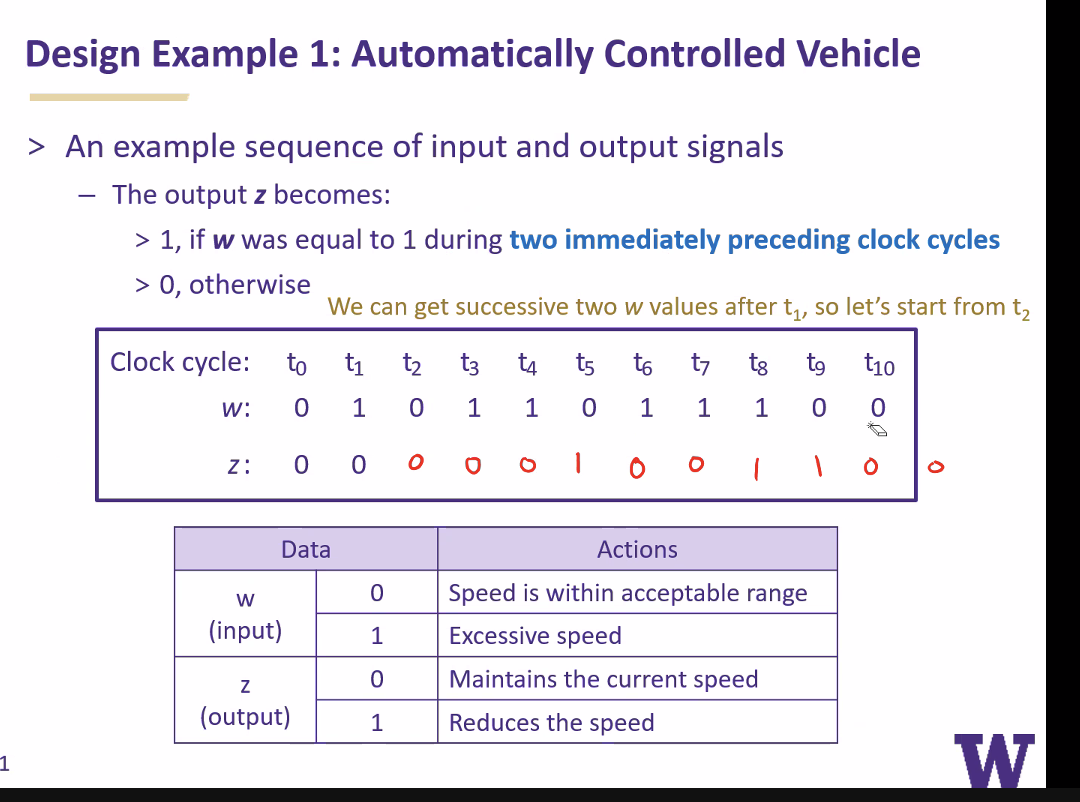

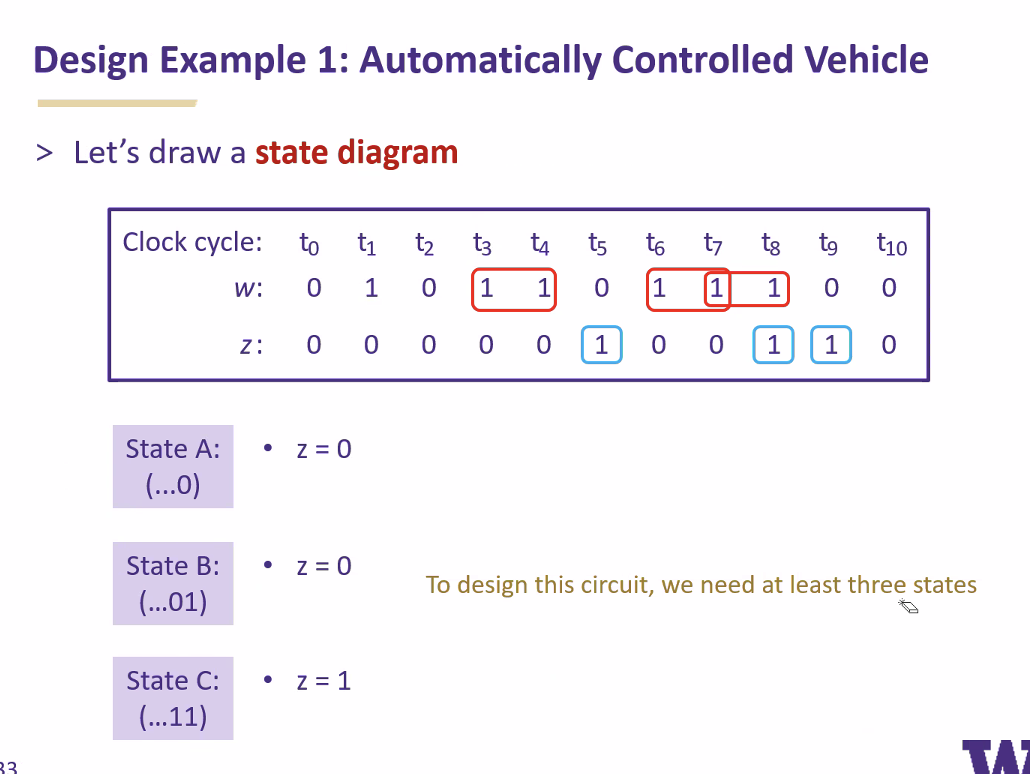

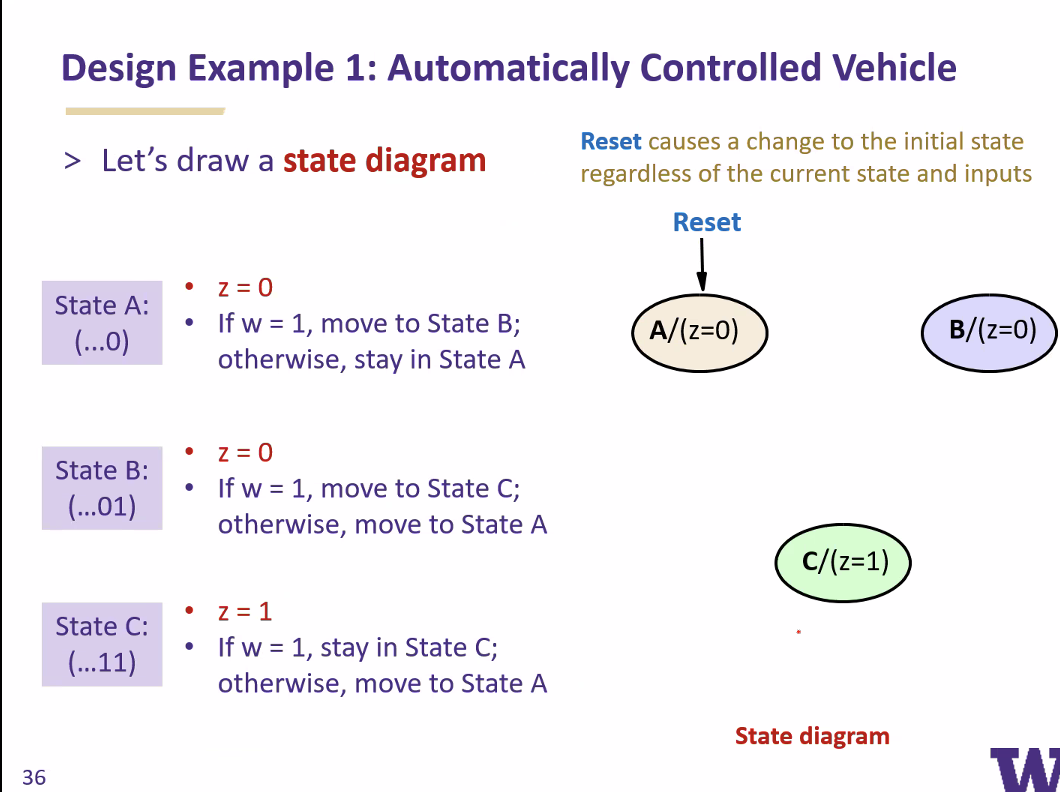

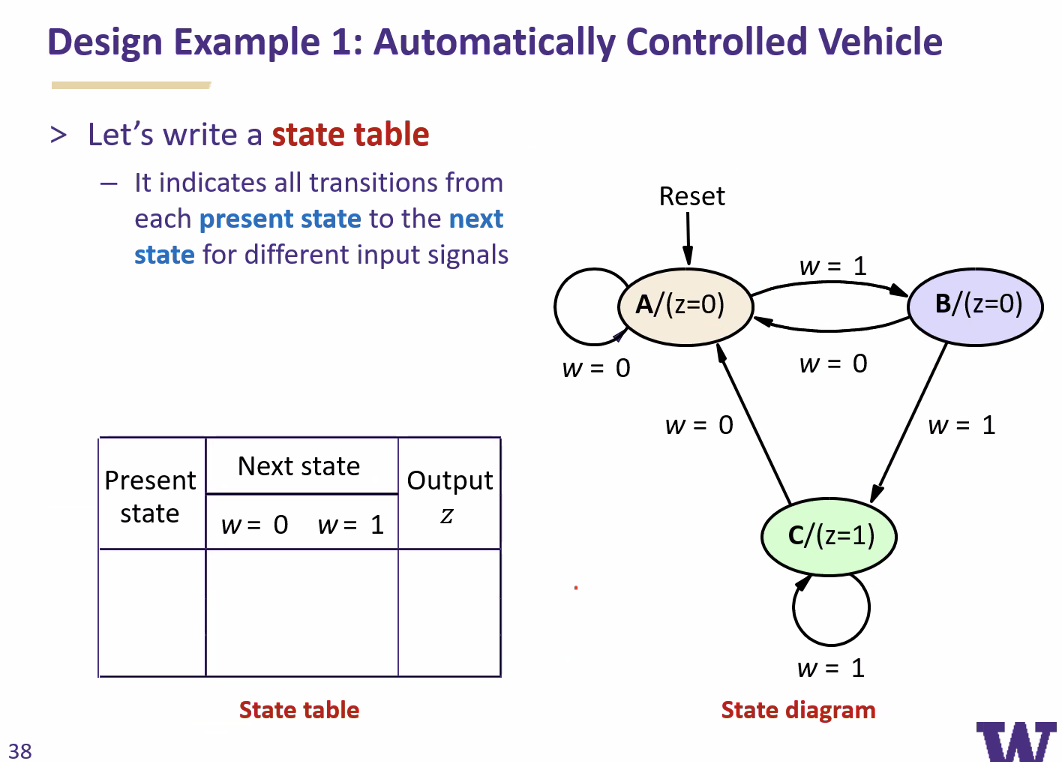

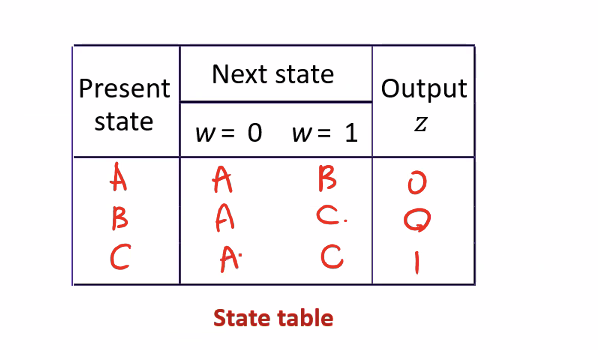

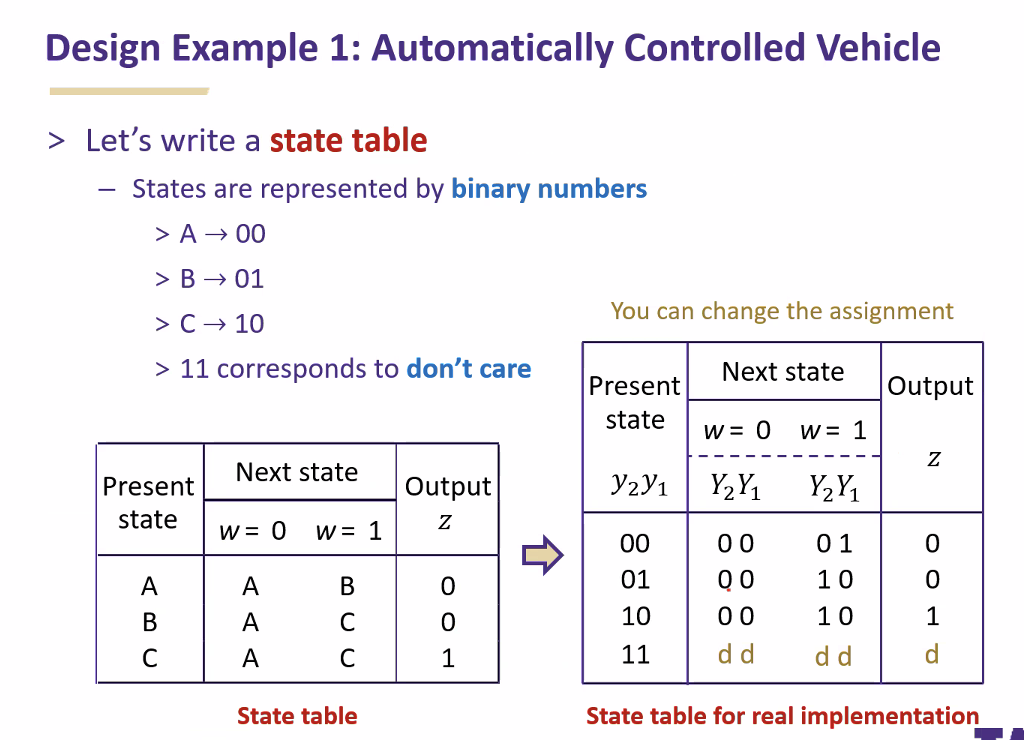

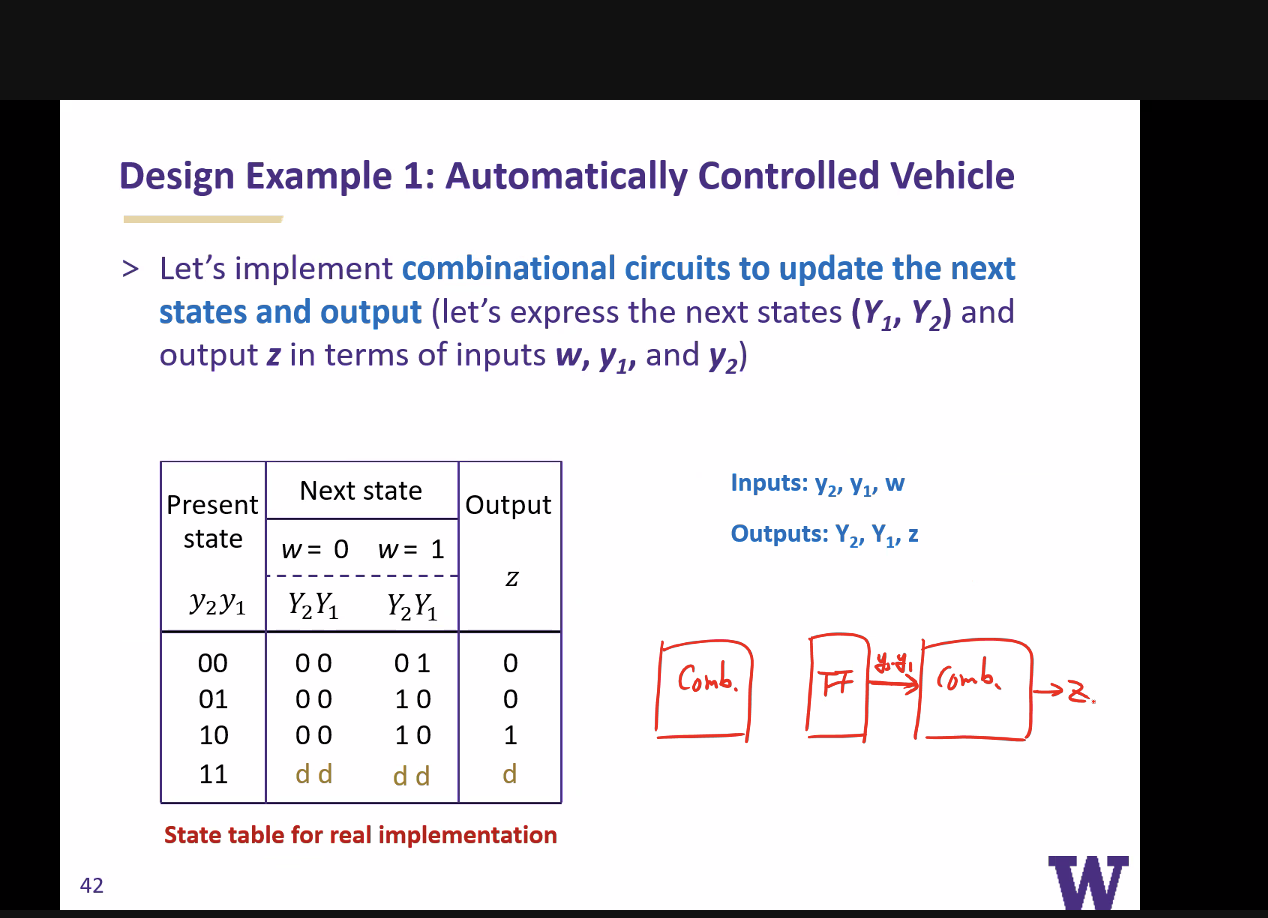

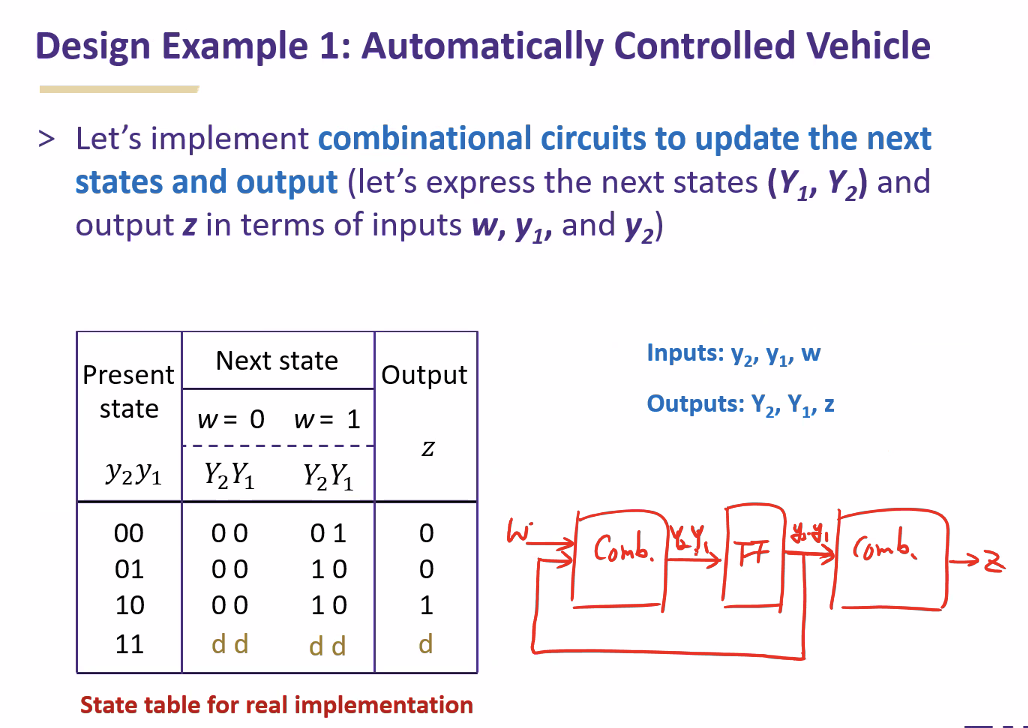

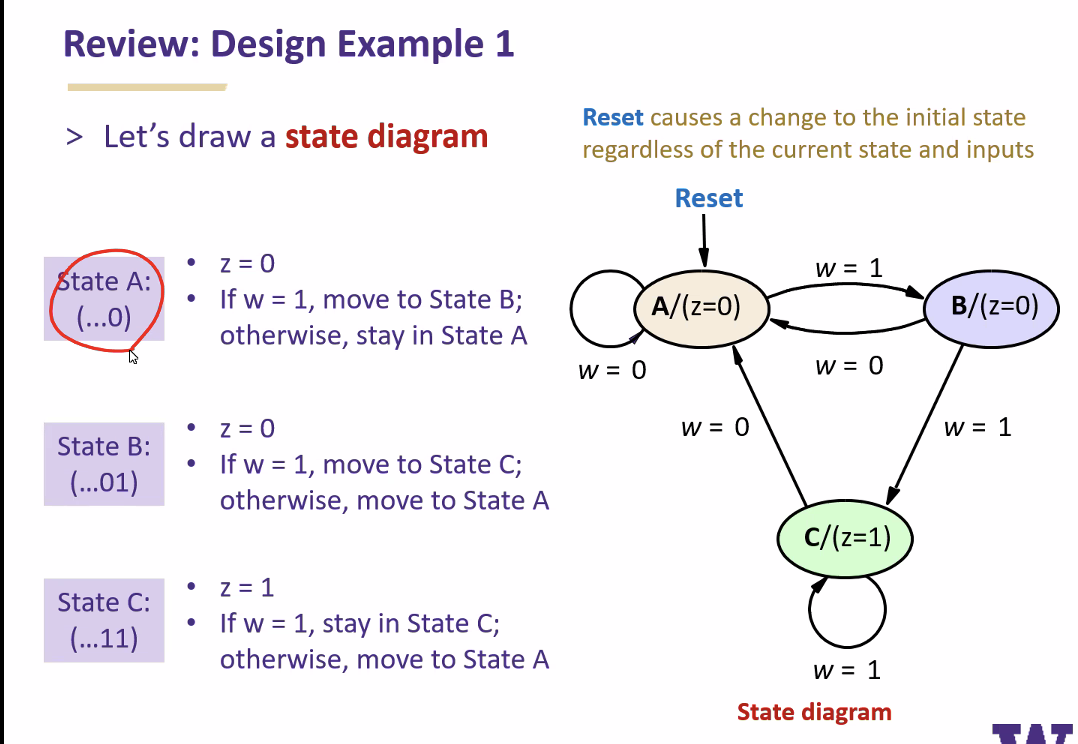

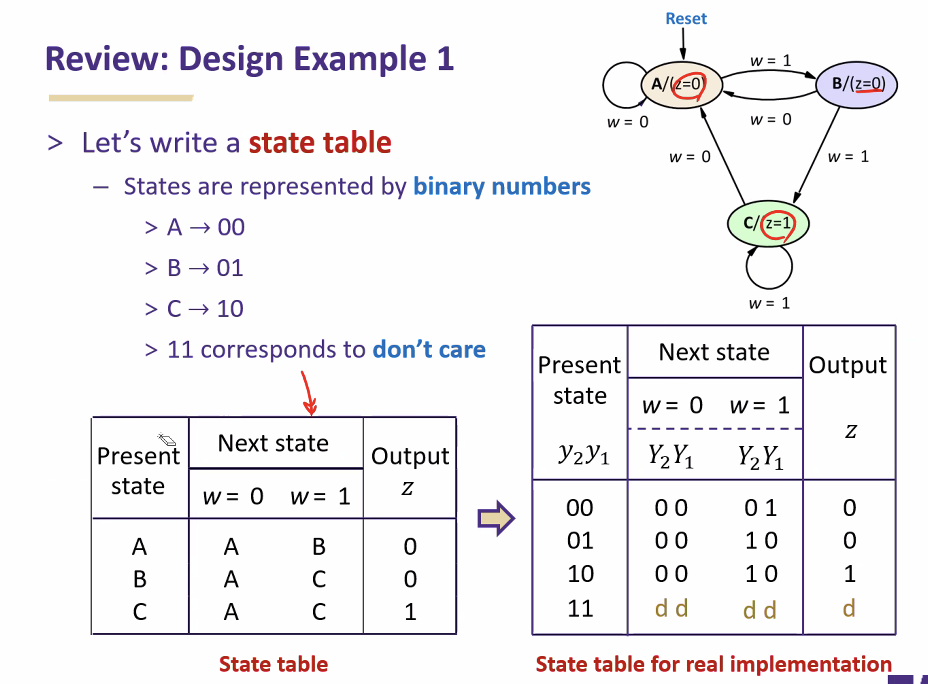

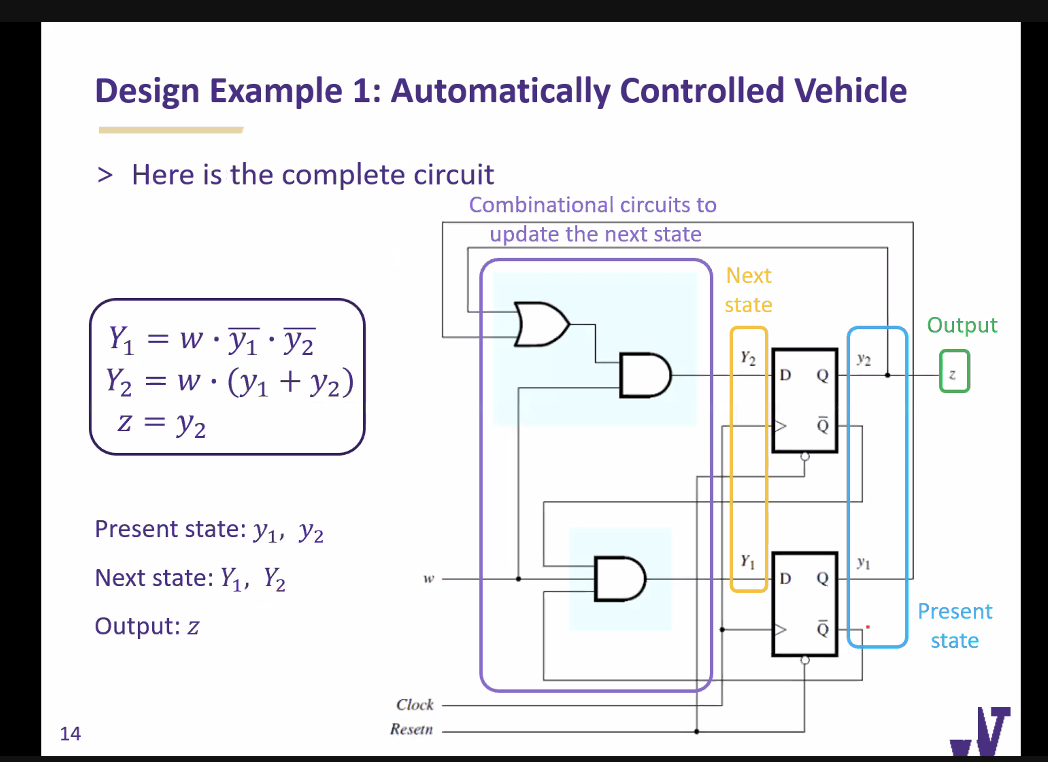

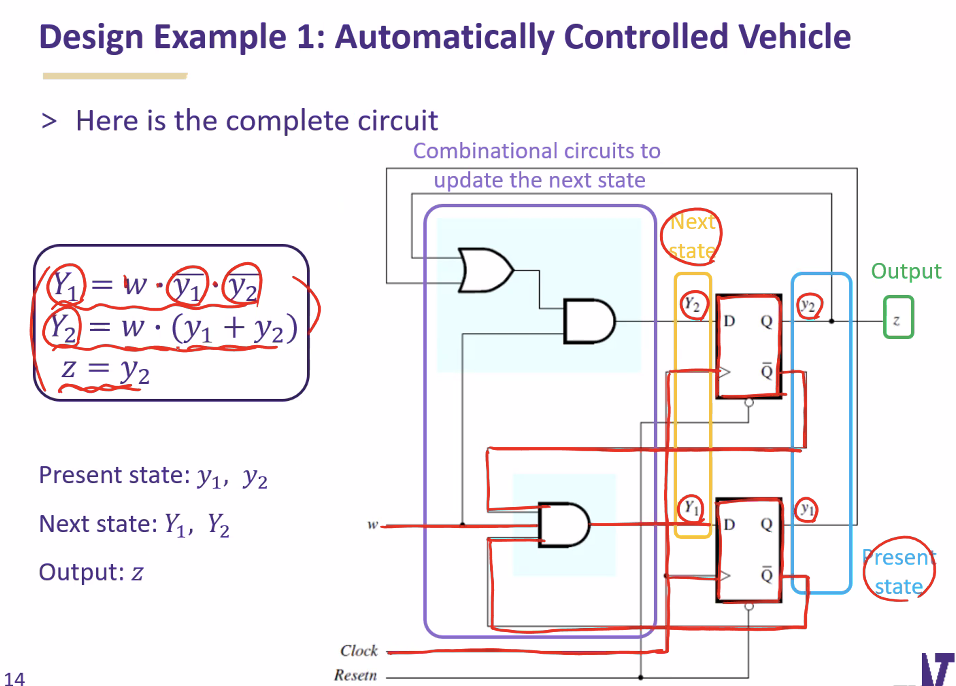

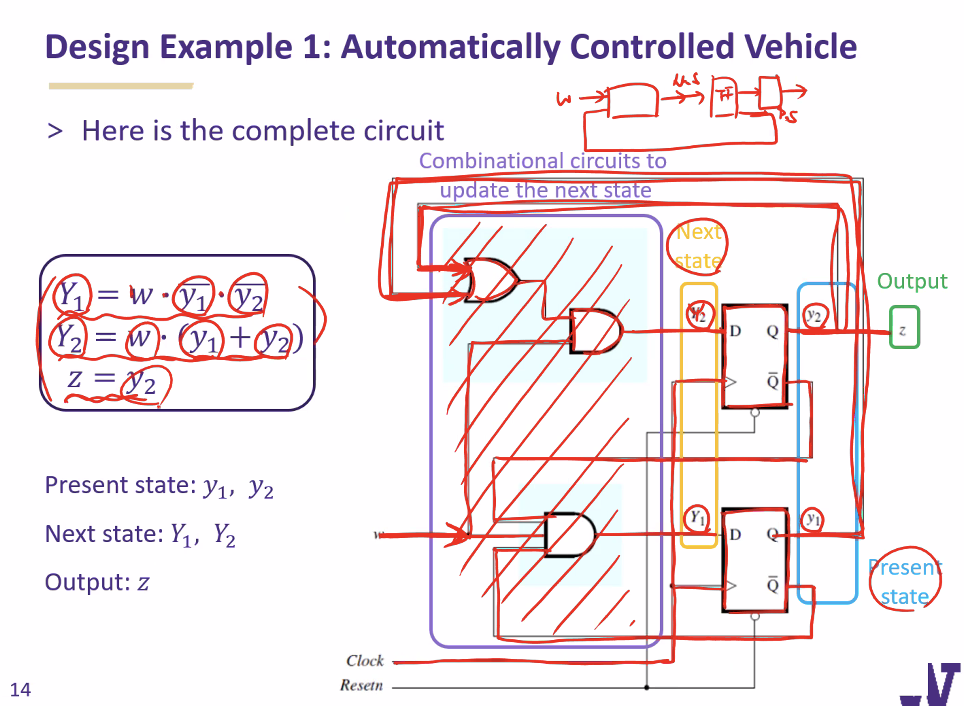

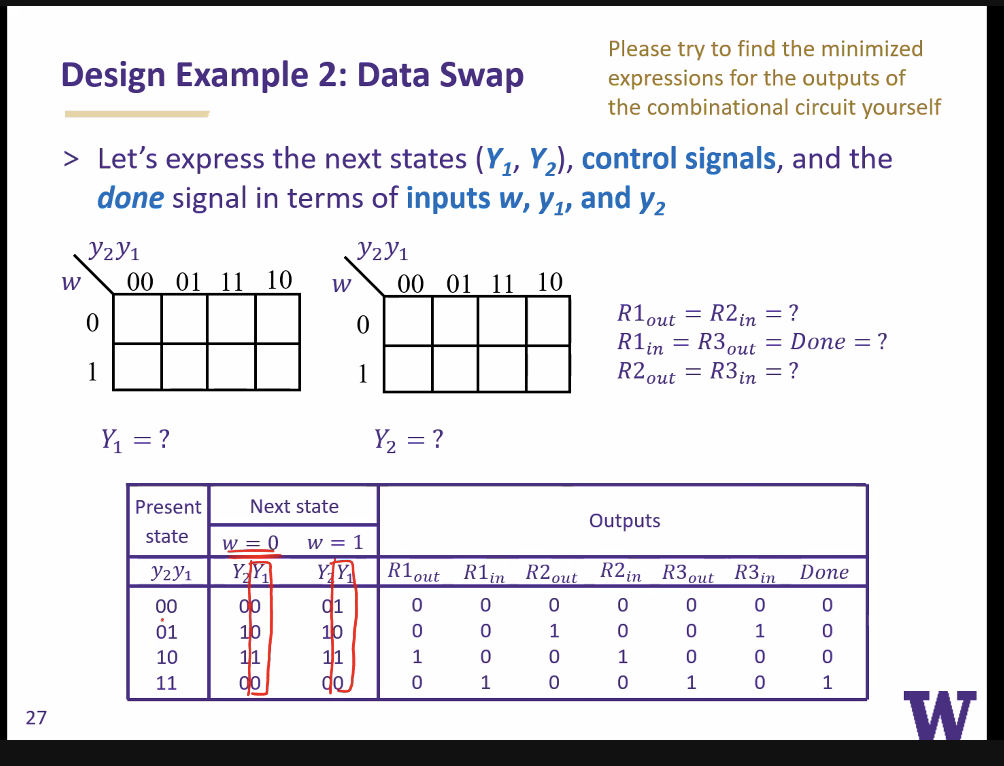

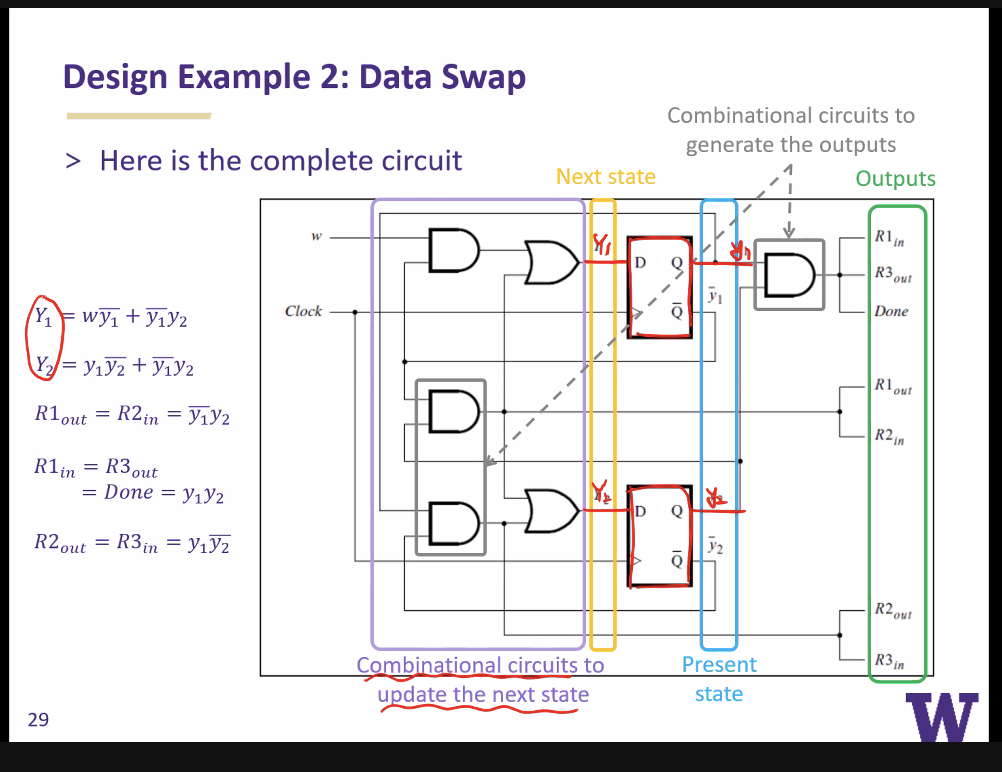

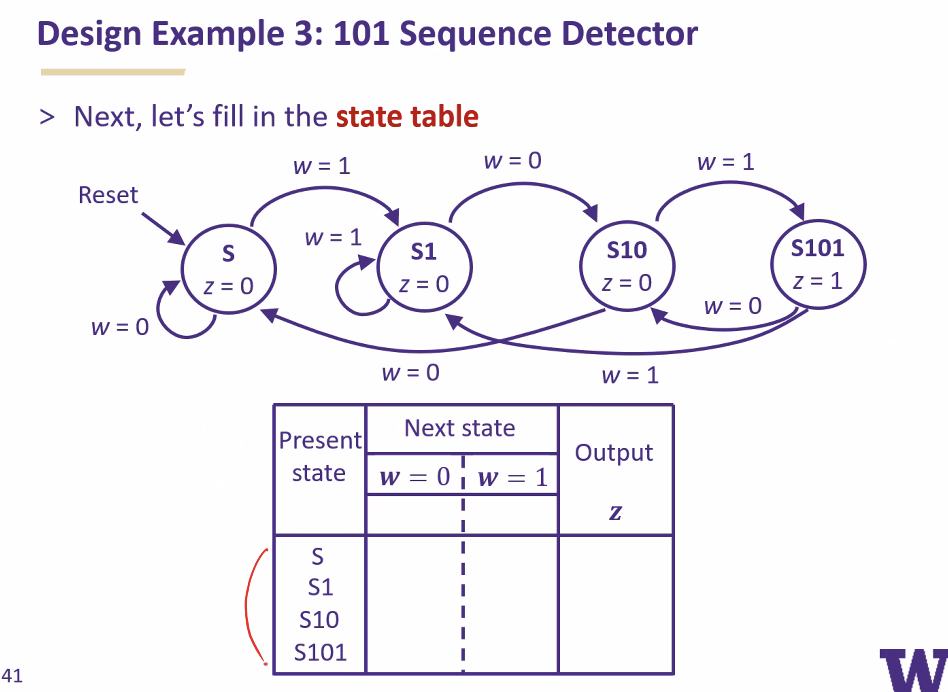

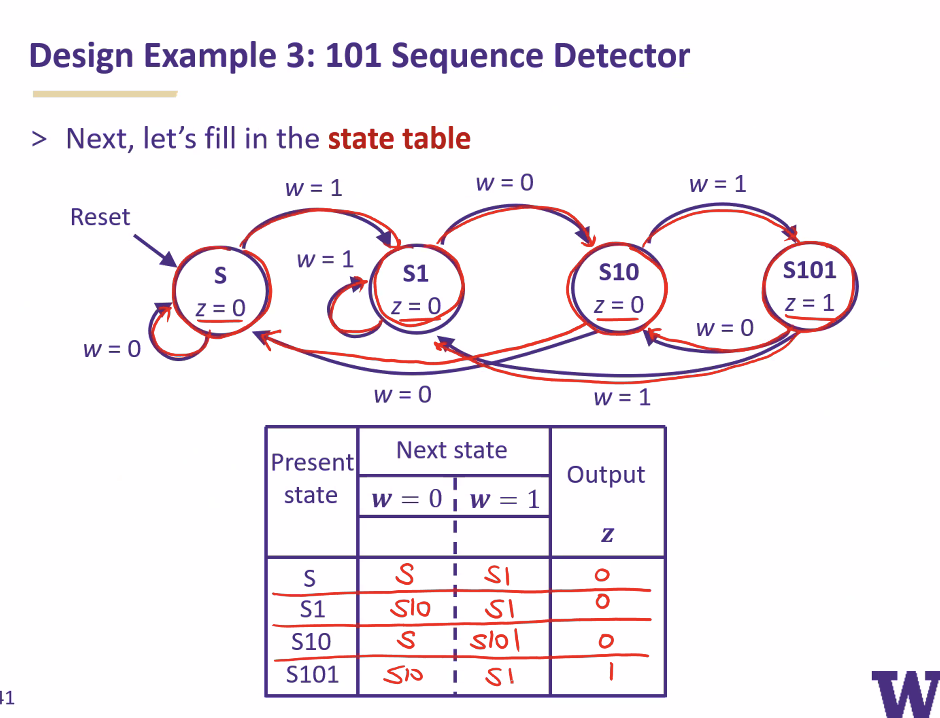

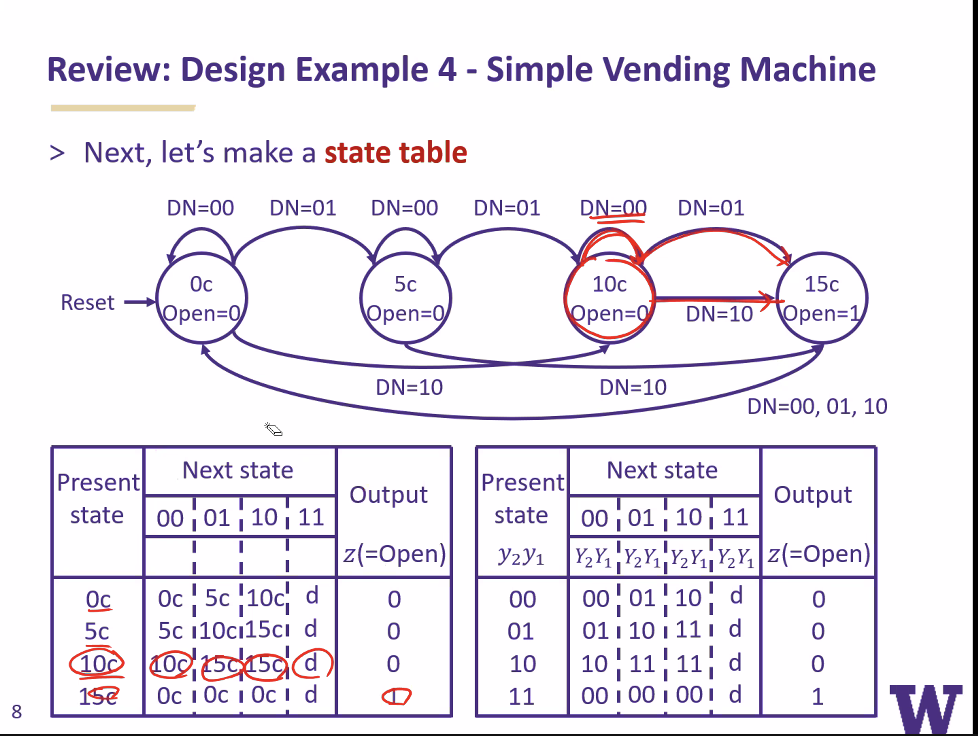

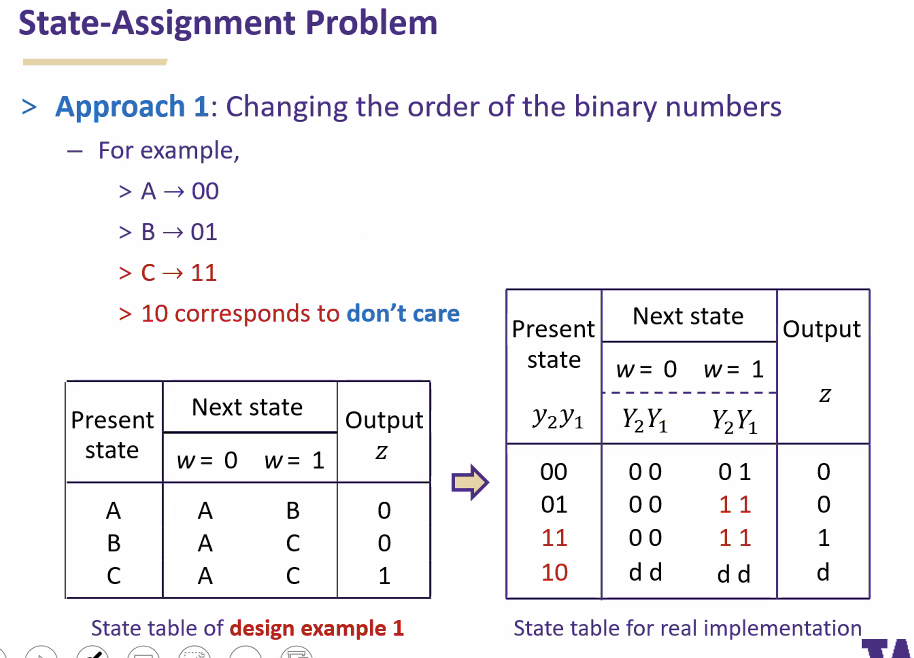

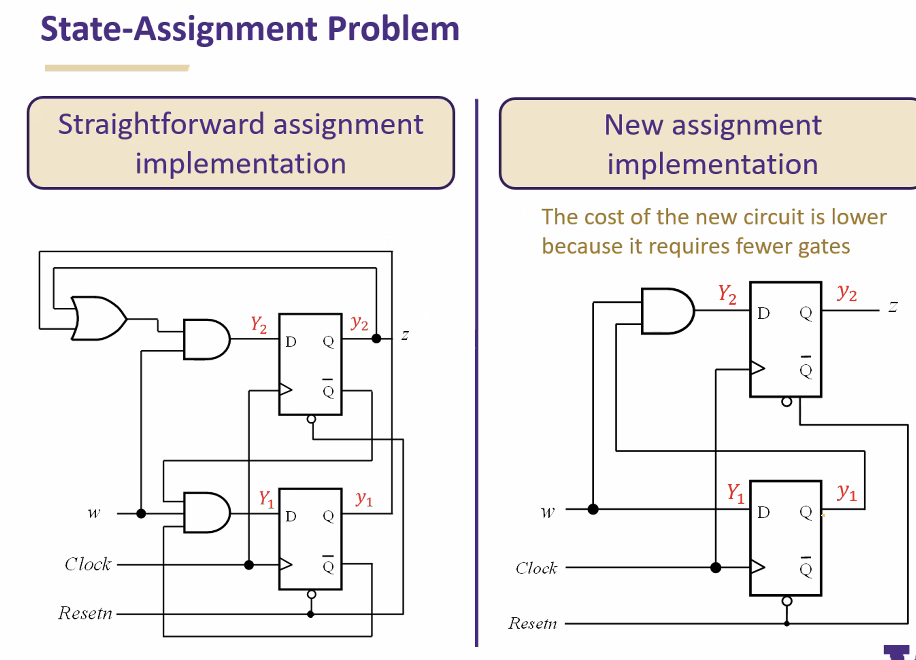

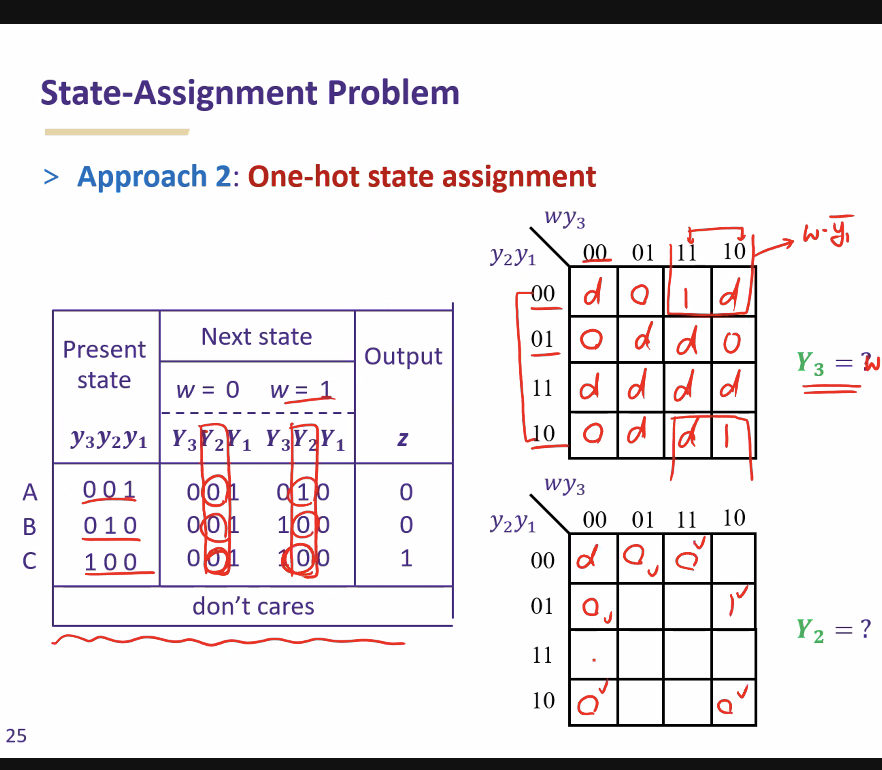

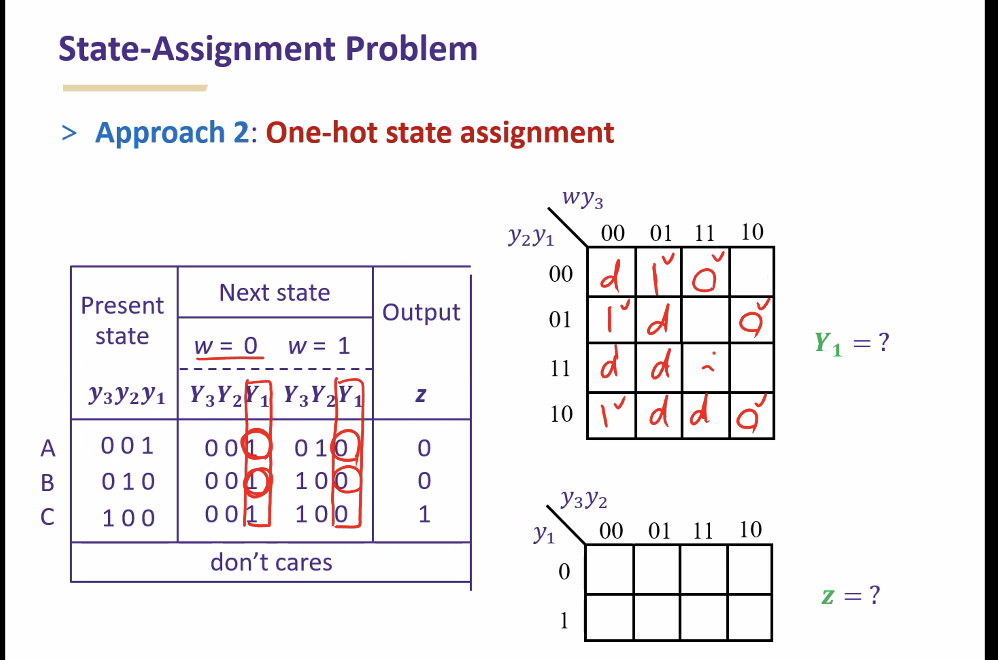

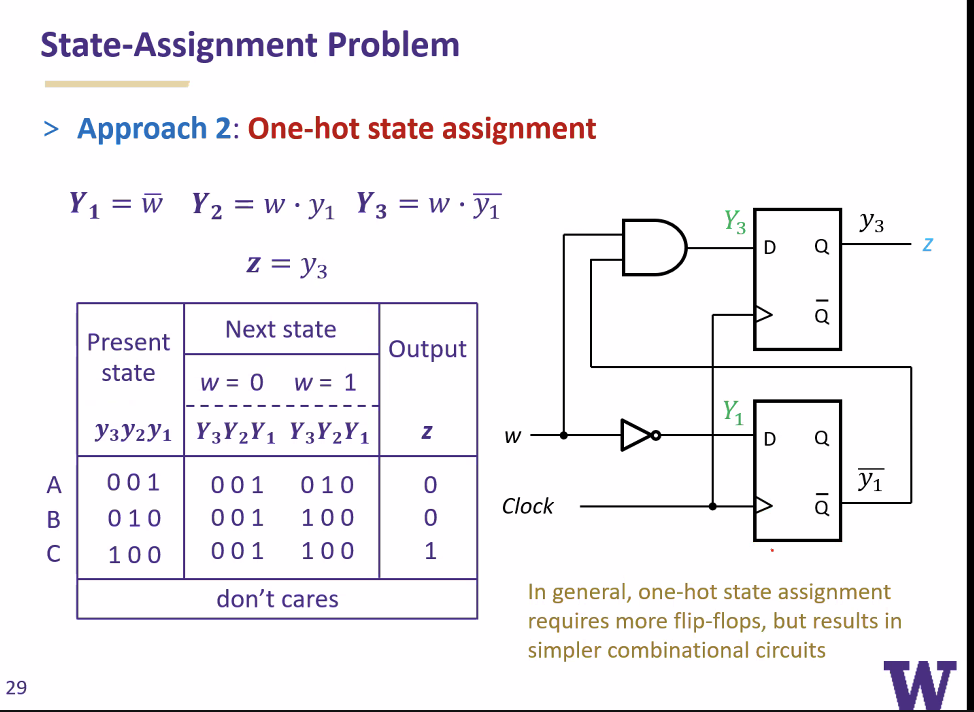

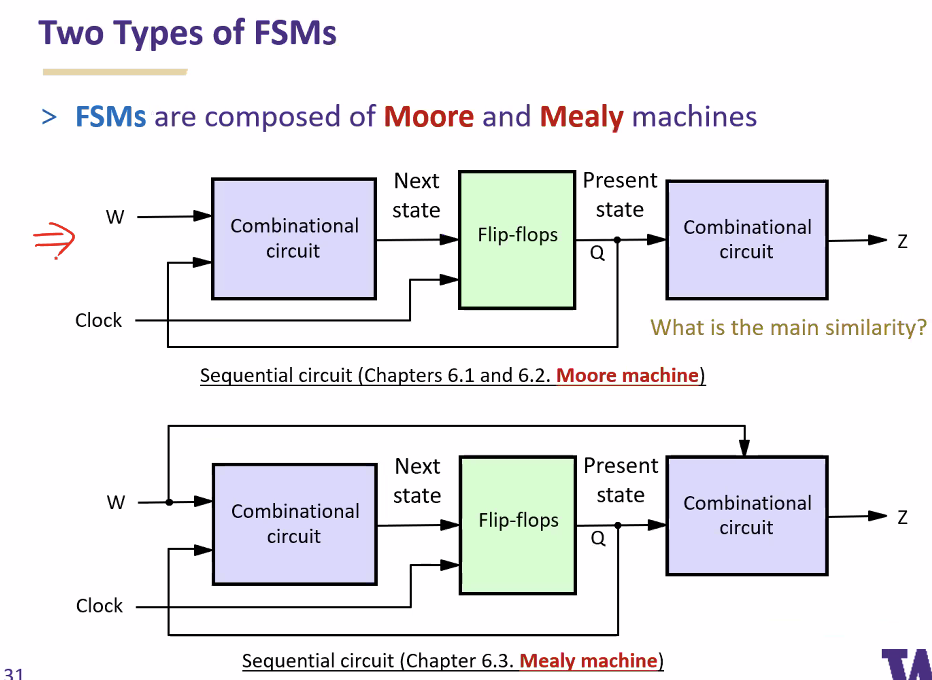

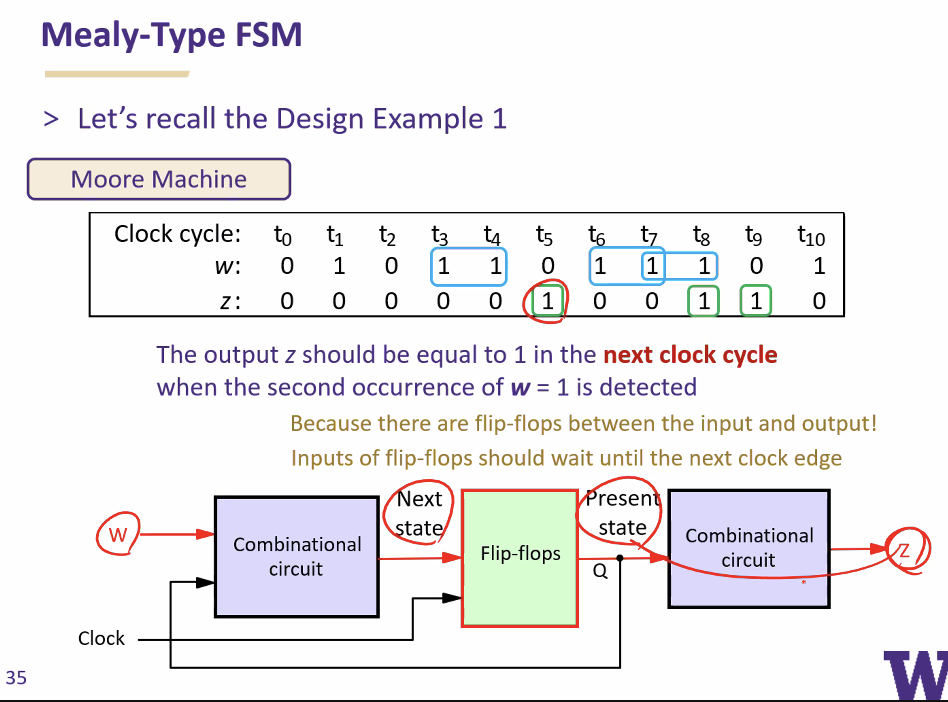

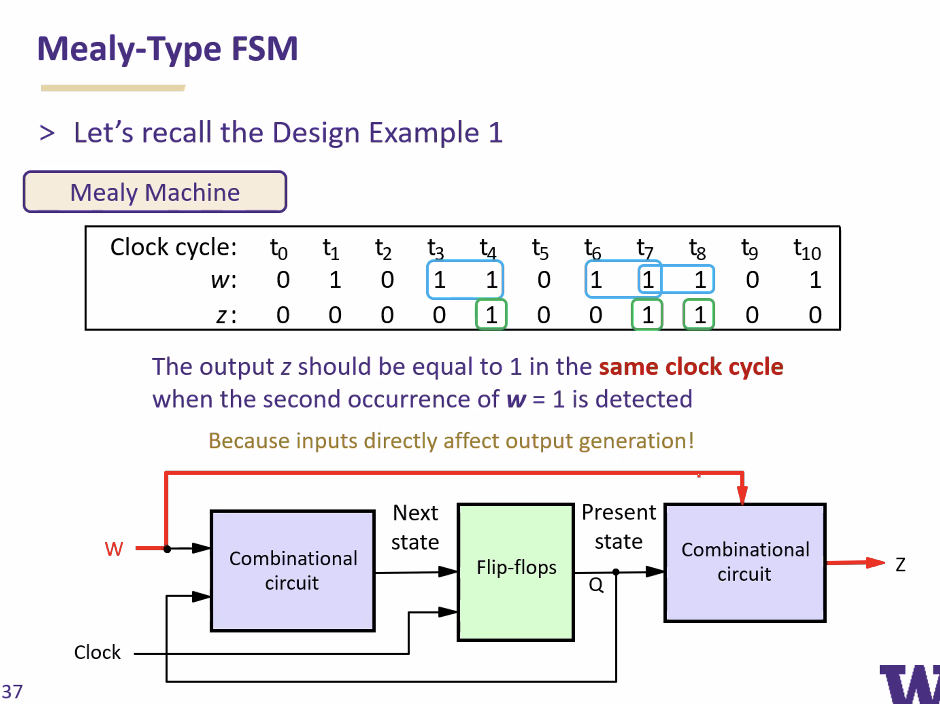

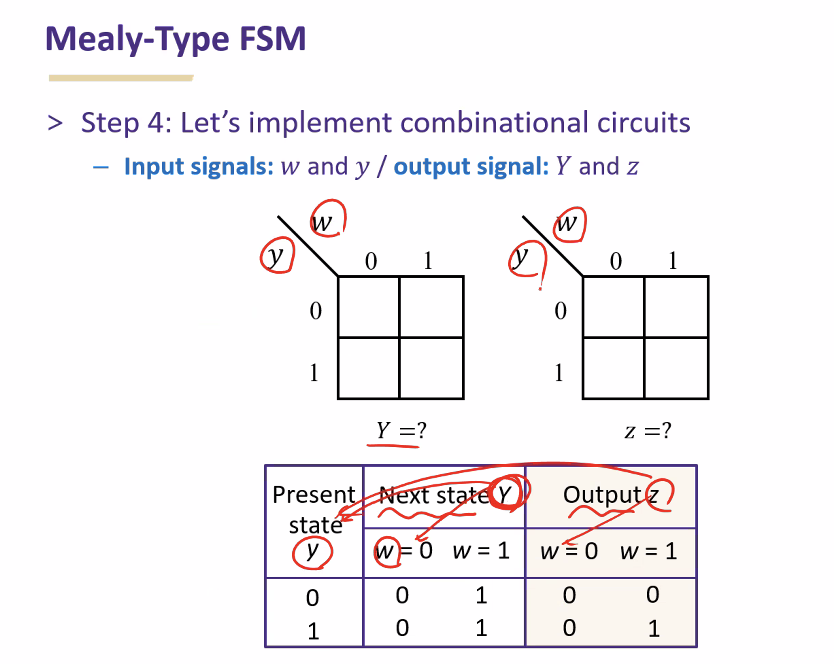

Sequence detector

Lecture 15

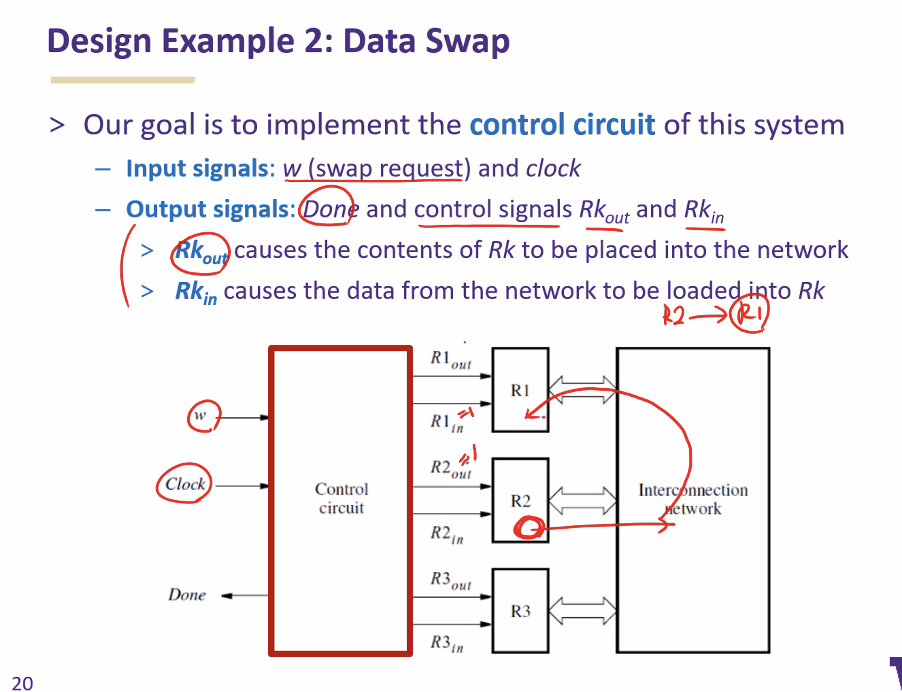

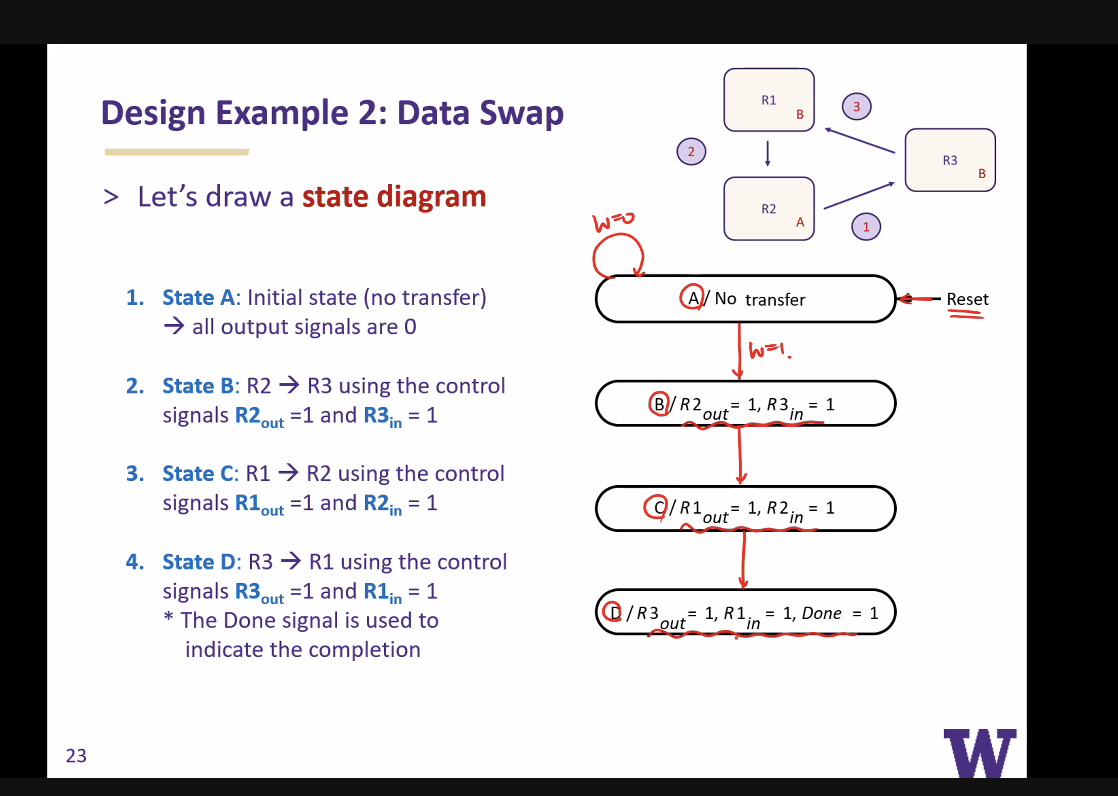

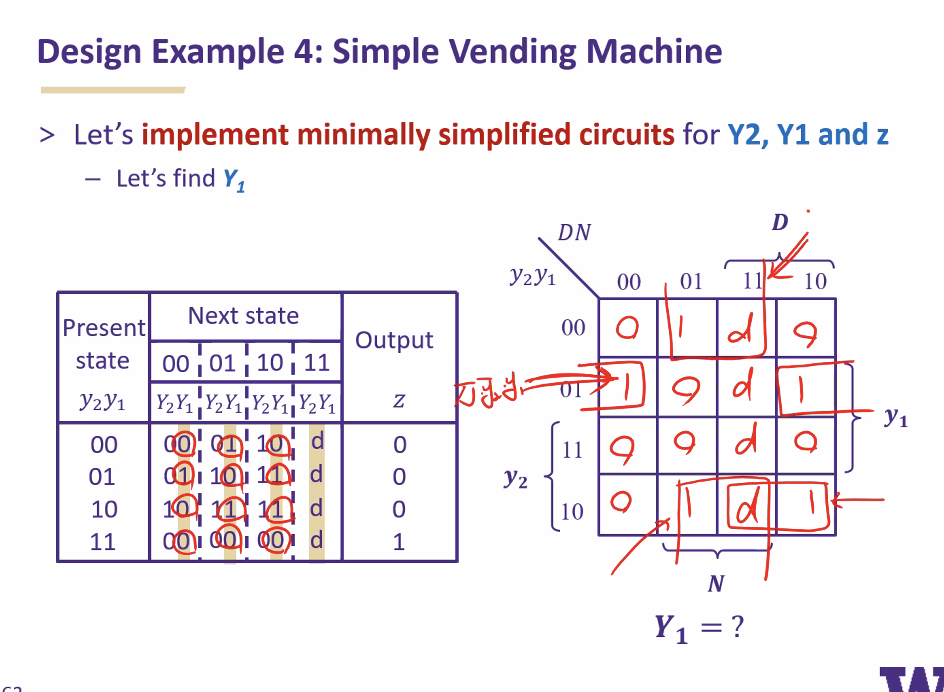

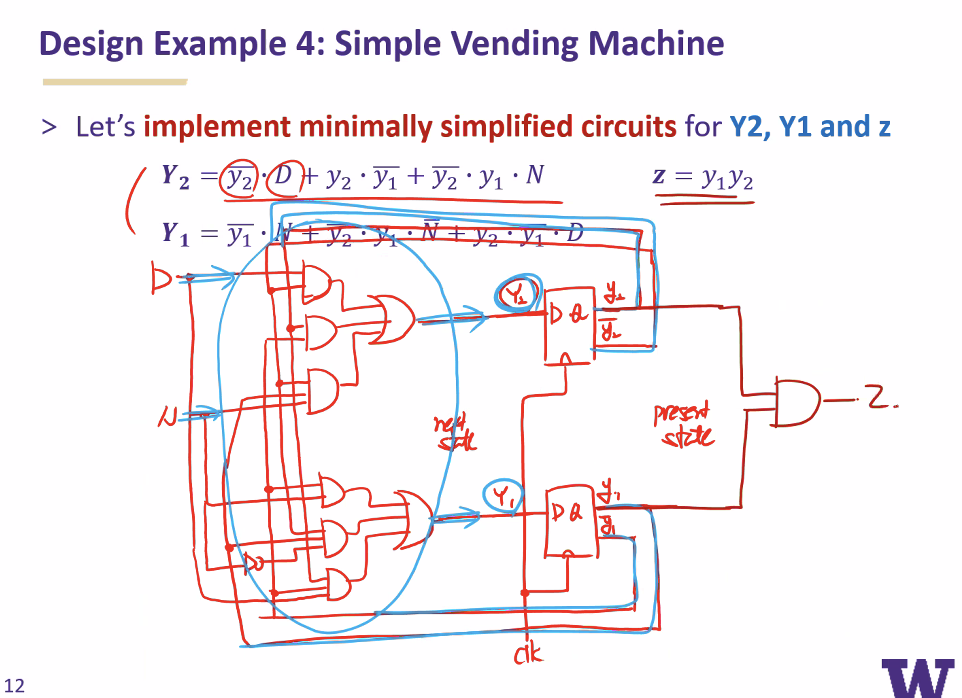

Lecture 16/17

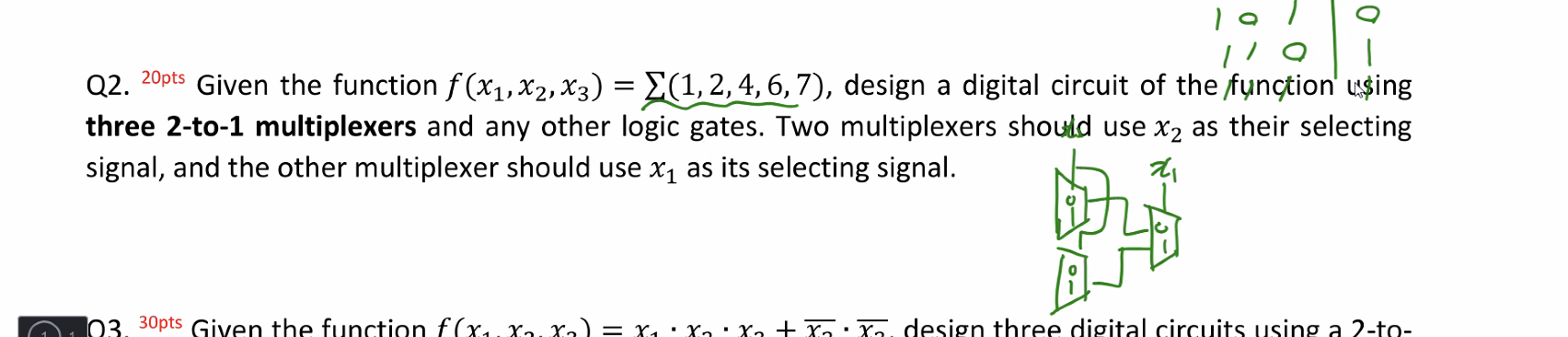

Review